Микро-80/Радио 1983-02/Процессорный модуль

| Данный материал защищён авторскими правами!

Использование материала заявлено как добросовестное, исключительно для образовательных некоммерческих целей. Автор: Г. ЗЕЛЕНКО, В. ПАНОВ, С. ПОПОВ Источник: http://retro.h1.ru/MK80/CPU/M80CPUi.php |

Основой нашей микро-ЭВМ является микропроцессор КР580ИК80А. Он выполнен в виде БИС в пластмассовом корпусе с 40 выводами. Перечислим сигналы ни выводах, с которыми работает микропроцессор, и их назначение.

- ША [0—15] - выходные сигналы тины адресов для адресации памяти или портов ввода — вывода:

- ШД [0—7] — входные или выходные сигналы двунаправленной шины данных для обмена данными с памятью или портами ввода — вывода, а также для вывода из микропроцессора информации о его состоянии;

- С1, С2 — входные периодические сигналы для тактирования микропроцессора;

- С — выходной сигнал синхронизации, вырабатываемый в начале каждого машинного цикла и указывающий, что, но шине данных передается информация о состоянии микропроцессора;

- СБР — входной сигнал установки микропроцессора в начальное состояние, обеспечивающее выполнение программы с команды, содержащейся в ячейке памяти с адресом 0000Н;

- ПМ — выходной сигнал, инициирующий выдачу данных периферийными модулями на шину данных;

- ВД — выходной сигнал, сопровождающий выдачу микропроцессором информации на шину данных для записи в периферийные модули;

- ГТ — входной сигнал от модулей памяти или портов ввода — вывода, указывающий на их готовность к обмену данными с микропроцессором;

- ОЖ — выходной сигнал при ожидании микропроцессором готовности периферийных модулей;

- ЗХ — входной сигнал, инициирующий перевод шин адресов и данных микропроцессора в высокоимпедансное состояние;

- ПЗХ — выходной сигнал, подтверждающий перевод шин адресов и данных микропроцессора в высокоимпедансное состояние;

- РПР — выходной сигнал разрешения прерывания выполнения текущей программы;

- ЗПР—входной сигнал запроса прерывания.

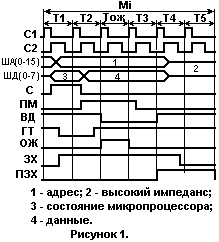

Микропроцессор тактируется импульсами С1 и С2, формируемыми внешним тактовым генератором. Выполнение каждой команды происходит за один или несколько (до 5) машинных циклов, каждый из которых связан с обращением за командой или данными к памяти или портам ввода — вывода. В свою очередь, машинный цикл разделяется на 3—5 тактов, длительность которых равна периоду следования тактирующих импульсов.

В каждом такте любого машинного цикла микропроцессор выполняет определенные действия:

- T1 — устанавливает код адреса периферийного модуля на шине адресов.

- Т1/Т2 — выводит информацию о своем состоянии по шине данных,

- Т2 — проверяет состояние сигналов на входах ГТ и ЗХ,

- Т3 — реализует обмен одним байтом информации с памятью или портами,

- Т4/Т5 — выполняет внутренние межрегистровые передачи и обработку данных в соответствии с командой.

Временная диаграмма выполнения обобщенного машинного цикла приведена на рис.1. Следует заметить, что здесь оба сигнала ПМ и ВД изображены активными условно. В течение реального машинного цикла активным может быть только один из них.

Адрес порта или ячейки памяти, с которым идет обмен информацией в текущем машинном цикле, формируется микропроцессором на шине адресов в такте Т1 и остается неизменным до окончания такта Т3.

Сигналы ПМ и ВД являются общими как для модулей памяти, так и для портов ввода—вывода, что приемлемо только в простейших микроЭВМ. В более сложных микро-ЭВМ используют дополнительные сигналы управления, выдаваемые микропроцессором на шину данных в тактах Т1/Т2 в виде 8-разрядного кода — байта состояния, который по сигналу синхронизации С запоминается (фиксируется) во внешнем регистре и определяет действия микропроцессора в остальных тактах текущего машинного цикла. Использование байта состояния позволяет однозначно определить, с какой группой периферийных модулей происходит обмен данными в текущем машинном цикле. Наличие единицы в отдельных разрядах байта со стояния является признаком выполнения микропроцессором в текущем машинном цикле следующих действий:

- ЩД[О] (ППР) — обслуживание запроса прерывания;

- ШД[1] (3В) — запись в память или вывод данных в порт;

- ШД[2] (СТК) — обращение к области памяти, используемой в качестве стека;

- ШД[3] (ОСТ) — останов микропроцессора по команде HLT,

- ШД[4] (ВЫВ) — вывод данных в порт,

- ШД[5] (Ml) — чтение кода операции команды,

- ШД[6] (ВВ)- ввод данных из порта,

- ШД[7] (ЧТП) — чтение данных из памяти.

В такте Т2 во время действия сигнала С2 микропроцессор анализирует входные сигналы ГТ и ЗХ. Если входной сигнал ГТ имеет уровень 0 (далее вместо выражений «логическая единица» или «логический нуль» будем использовать обозначения 1 или 0 соответственно), то после такта Т2 выполняются вспомогательные такты ожидания ТОЖ. Это позволяет использовать в микро-ЭВМ память и периферийное оборудование с малым быстродействием. Число вспомогательных тактов ожидания определяются длительностью поддержания памятью или другим периферийным модулем входного сигнала ГТ в состоянии 0. Как только периферийный модуль будет готов к обмену данными, он установит на этом входе состояние 1, что позволит микропроцессору перейти к выполнению такта Т3.

Если во время действия такта Т2 на входах ЗХ присутствует сигнал с уровнем 1, то микропроцессор реагирует на это в конце такта Т3 или следующего за ним такта в зависимости от того, выполнялся ли цикл чтения или записи соответственно. При этом на выводе ПЗХ возникает сигнал подтверждения того, что шины адресов и данных микропроцессора переведены в высокоимпедансное состояние. Продолжительность пребывания в таком состоянии определяется длительностью поддержания входного сигнала ЗХ. Это позволяет обеспечить периферийным модулям запись или считывание данных непосредственно в память микро-ЭВМ или из нее, минуя микропроцессор. При этом периферийные, модули должны самостоятельно устанавливать на шине адресов микро-ЭВМ адрес требуемой ячейки памяти, а также формировать соответствующие сигналы записи или считывания. Такой обмен данными между периферийными модулями и памятью микро-ЭВМ называется прямым доступом к памяти.

В первом машинном цикле Ml микропроцессор считывает в такте Т3 код операции команды из памяти микро-ЭВМ и. если для ее реализации не требуются дополнительные действия по обмену данными с памятью или портами ввода — вывода, выполняет команду в такте Т4 (или Т4 и Т5). В противном случае в дополнительных машинных циклах (М2—М5) происходит обмен данными между микропроцессором и памятью или портами ввода—вывода.

Для примера в таблице приведена последовательность действий, совершаемых микропроцессором при выполнении команды IN ADR.

| Машинный цикл | Машинный такт | Действие |

| Ml | Т1 | Вывод содержимого указателя адреса на тину адресов |

| Т1/Т2 | Вывод на тину данных информации о состоянии микропроцессора | |

| Т2 | Опрос состояния входов ГТ и ЗХ | |

| Т3 | Чтение коды команды из памяти, увеличение на 1 содержимого указателя адреса | |

| Т4 | Подготовка микропроцессора к выполнению команды | |

| М2 | Т1 | Вывод содержимого указателя адреса на тину адресов |

| Т1/Т2 | Вывод на тину данных информации о состоянии микропроцессора | |

| Т2 | Опрос состояния входов ГТ и ЗХ | |

| Т3 | Чтение из памяти адреса порта ввода, увеличение на 1 содержимого указателя адреса | |

| М3 | Т1 | Вывод на шину адресов адреса порта ввода |

| Т1/Т2 | Вывод на шину данных информации о состоянии микропроцессора | |

| Т2 | Опрос состояния входов ГТ и ЗХ | |

| Т3 | Чтение из порта ввода байта данных в аккумулятор, опрос состояния входа ЗПР |

При появлении на входе микропроцессора сигнала запроса прерывания ЗПР микропроцессор прерывает выполнение текущей программы и переходит к выполнению подпрограммы обработки запроса прерывания. Это возможно только в том случае, если ранее в программе была выполнена команда разрешения прерывания ЕI. Эта команда обеспечивает формирование на выводе РПР микропроцессора уровня 1, что свидетельствует о возможности прерывания текущей программы.

С появлением сигнала запроса прерывания ЗПР микропроцессор в первом такте цикла Ml очередной команды устанавливает на шине данных байт состояния, где вместо признака чтения данных из памяти ЧТП присутствует признак подтверждения прерывания ППР. В результате этого микропроцессор вместо кода очередной команды текущей программы считывает по сигналу ЧТКП с шины данных микроЭВМ код одной из команд передачи управления, формируемый модулем контролера прерывания. Одновременно снимается выходной сигнал РПР, что не позволяет микропроцессору в дальнейшем реагировать на новые запросы прерывания вплоть до выполнения следующей команды EI. Запретить прерывание текущей программы можно также командой запрета прерывания DI в любом месте выполняемой программы. При этом выходной сигнал РПР микропроцессора приводится к уровню 0.

С дополнительными сведениями о структуре и некоторых особенностях работы микропроцессора в различных режимах читатель может познакомиться во второй главе книги [1], где описан зарубежный аналог — микропроцессор 8080 фирмы INTEL.

Микропроцессор и ряд вспомогательных интегральных схем образуют процессорный модуль. Электрическая принципиальная схема модуля представлена на рис.2, находящемся в альбоме. В состав модуля, кроме микропроцессора, входят генератор тактовых импульсов, входной регистр, формирователи сигналов шины адресов и шины данных микро-ЭВМ, а также узел формирования сигналов шины управления микро-ЭВМ. Генератор тактовых импульсов выполнен на элементах D1.1 и D1.2 и возбуждается кварцевым резонатором Z1, резонансная частота которого может находиться в пределах от 4000 до 20000 кГц, что обеспечивает период следования тактовых импульсов соответственно от 2 до 0,4 мкс. Сигнал с выхода элемента D1.2 поступает на тактовый вход С1 формирователя тактовых импульсов, выполненного на основе двоичного счетчика D4 и логических элементах D1.6, D2.3. D7.1 и D7.2. С первого и второго выходов счетчика D4 снимаются соответственно сигналы ТИ1 и ТИ2, а с выходов логических элементов D2.3 и D1.6 — соответственно сигналы Ф1 и Ф2, которые используют для тактирования некоторых периферийных модулей микро-ЭВМ. Сигналы, формируемые на выходах логических элементов D7.1 и D7.2, совпадают во времени с сигналами Ф1 и Ф2 и поступают соответственно на входы С1 и С2 микропроцессора. Амплитуда этих сигналов равна 12В, что обеспечено использованием логических элементов с открытым коллектором и нагрузочными резисторами R1 и R3.

Для фиксации состояния входных управляющих линий УСТ. ЗПР. ЗХ и ГТ служит входной регистр D8, занесение информации, в которой происходит по входам D1—D4 в момент перехода сигнала на счетном входе С в состояние 1. Входная линия ГТ нагружена на резистор R8, что позволяет подключать сюда через элементы с открытым коллектором, но схеме «проводное ИЛИ» одноименные выходные линии периферийных модулей, требующих замедления работы микропроцессора при обмене данными с ним. Входные линии ЗПР и ЗХ также нагружены на резисторы R6 и R7 соответственно, что обеспечивает работоспособность процессорного модуля, если в микро-ЭВМ не использованы модули контроллера прерываний и прямого доступа к памяти. Для надежной установки внутренних узлов микропроцессора в начальное состояние длительность сигнала СБР должна быть не менее трех периодов следования тактирующих сигналов С1 и С2, что обеспечивают резистор R5 и конденсатор С12. Сигналы с выхода регистра D8 поступают непосредственно на управляющие входы микропроцессора, обеспечивая перевод его в соответствующий режим работы.

Так как низкая нагрузочная способность выходных линий микропроцессора (выходной ток при уровне 0 всего 1,8мА) не позволяет подключать к ним более одного входа ТТЛ интегральных схем, в состав процессорного модуля введены формирователи сигналов шины адресов, шины данных и шины управления микро-ЭВМ. При этом достигается повышение нагрузочной способности шин микро-ЭВМ до 120мА для выходного тока уровня О и допустимой емкости нагрузки до 300пФ, что позволяет подключать к шинам микро-ЭВМ большое число различных периферийных модулей.

Формирователи сигналов шины адресов микро-ЭВМ выполнены с использованием четырехразрядных шинных формирователей с инверсией D13—D16. На входы D11—D14 которых, поступают сигналы с адресных выходов микропроцессора. Выходные линии DB1--DB4 формирователей D13—D16 образуют шину адресов микро-ЭВМ. Шинные Формирователи справляются по входам выбора микросхем ВМ При наличии на этих входах сигналов 0 выходные сигналы шины адресов микропроцессора поступают на соответствующие линии шины адресов микро-ЭВМ. При появлении на входах ВМ сигнала 1 запрещается прохождение сигналов с входов D11—D14 шинных формирователей D13—D16 на выходы DB1— DB4, которые переходят в высокоимпедансное состояние.

Формирователи сигналов шины данных микро-ЭВМ выполнены также на основе четырехразрядных шинных формирователей D11 и D12, но работающих в двунаправленном режиме. Каждая разрядная линия двунаправленной шины данных микропроцессора соединяется с одним из входов D11— D14 и одним из соответствующих выходов D1—D4 шинных формирователей D11 и D12. Их выходные линии DB1—DB4 образуют двунаправленную шину данных микро-ЭВМ, позволяющую передавать данные от микропроцессора к памяти или другим периферийным модулям, а также в обратном направлении. Направление передачи данных через шинные формирователи D11 и D12 определяется сигналами на входах выбора шины ВШ. Сигнал 0 на этих входах обеспечивает передачу данных с входов D11—D14 через линии DB1—DB4 на шину данных микро-ЭВМ. Выходы D1—D4 при этом не оказывают влияния на работу шинных формирователей, так как в это время находятся в высокоимпедансном состоянии. При подаче на входы ВШ сигнала 1 направление передачи данных через шинные формирователи D11—D12 меняется на противоположное. В этом случае сигналы на шине данных микро-ЭВМ через линии DB1—DB4 поступают на выходы D1—D4 шинных формирователей и далее к микропроцессору. Управление формирователями шины данных микроЭВМ по входам ВМ происходит аналогично формирователям адресной шины.

Узел формирования сигналов шины управления микро-ЭВМ служит для получения управляющих сигналов. Обеспечивающих передачу информации между различными компонентами микро-ЭВМ. В состав узла входят регистр состояния микропроцессора D10, логические элементы D1.3-D1.5, D2.1, D2.2, D2.4, D3.1-D3.5 и D6.1-D6.3 и шинный формирователь D5. Информация о состоянии микропроцессора поступает на входы Д1—Д8 регистра D10 с выводов шины данных микропроцессора и фиксируется в нем при совпадении отрицательного сигнала на входе ВМ1 и положительного на входе ВМ2. При наличии уровня 1 на входе ВР принятая информация о состоянии микропроцессоров с выводов Q1 и Q8 регистра D10 поступает на соединительный разъем процессорного модуля и может быть использована для управления различными периферийными модулями микро-ЭВМ. При появлении сигнала 0 на входе ВР выходные линии Q1—Q8 регистра D10 переходят в высокоимпедансное состояние, что позволяет организовывать режим прямого доступа к памяти микро-ЭВМ.

Кроме сигналов состояния микропроцессора по шине управления микро-ЭВМ передаются сигналы, используемые при обращении к памяти или портам ввода—вывода для записи или считывания информации. Эти сигналы формируются на выходах DB1—DB4 шинного формирователя D5, которые переходят в высокоимпедансное состояние при наличии положительного сигнала на входе ВМ. В этом случае линии ЧТЗУ, ЗПЗУ. ЧТВВ и ЗПВВ микро-ЭВМ могут быть использованы для прямого доступа к памяти. Назначение других управляющих сигналов, формируемых в процессорном модуле, было определено ранее при описании работы микропроцессора.

Кроме выводов микропроцессора, о назначении которых также говорилось выше. У него есть еще три вывода для подведения напряжения питания +5В, +12В и —5В и один вывод — общий. Для нормальной работы микропроцессора рекомендуется одновременная подача всех питающих напряжении. Допустима и неодновременная подача с соблюдением следующей последовательности: первым подают напряжение —5В, затем +5В и последним +12В. Отключают питающие напряжения в обратной последовательности. В цепи питания микропроцессора рекомендуется установить фильтрующие керамические конденсаторы емкостью 0,022…0,15 мкФ на расстоянии не более 5 см от микросхемы. Потребляемый процессорным модулем ток от источника +5В не превышает 1А, +12В — около 100мА и —5В — менее 1мА.

Конструктивно процессорный модуль может быть выполнен как функционально законченный универсальный узел. Как и любой универсальный узел, он обладает определенной избыточностью, как по числу использованных управляющих сигналов, так и по нагрузочной способности шин. Модуль рассчитан на применение его в микроЭВМ с большим числом периферийных модулей, возможностью организации ввода—вывода методом прямого доступа к памяти и системы прерываний.

Такая избыточность, на наш взгляд, вполне оправдана, так как в дальнейшем позволит радиолюбителям по мере приобретения опыта и возникновения новых задач усложнять микро-ЭВМ.

В более простых конструкциях можно ряд микросхем модуля изъять или заменить другими. Так, если не требуется прямого доступа к памяти, вместо микросхемы К589ИР12 (D10) могут быть использованы любые D-триггеры. Элементы К589АП26 (D13—D16) могут быть заменены обычными инверторами, например К155ЛА1, а элементы D5, D11 и D12 (К589АП16) могут быть исключены совсем. Однако при всех таких изменениях надо помнить о нагрузочной способности шин микро-ЭВМ.

Отсканировано с журнала РАДИО № 2 1983 г.

Отредактировано Лесных Ю. И. 1999 г.