КМ1801ВМ3

| Данный материал защищён авторскими правами!

Использование материала заявлено как добросовестное, исключительно для образовательных некоммерческих целей. Источник: Справочник |

КМ1801ВМ3А, КМ1801ВМ3Б, КМ1801ВМ3В

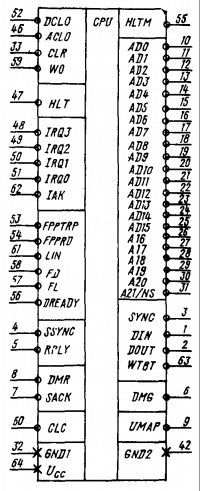

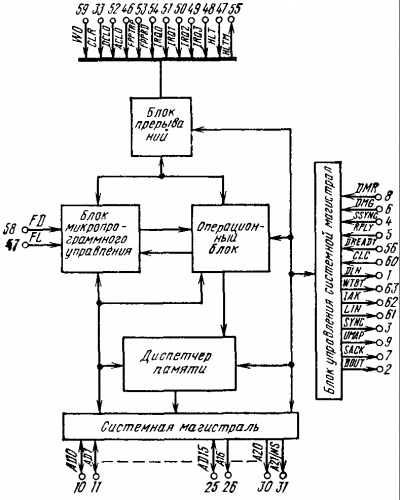

Микросхема КМ1801ВМ3 — 16-разрядный однокристальный микропроцессор, включающий операционный блок, блок микропрограммного управления, блок прерываний, диспетчер памяти и блок управления системной магистрали. Содержит 200000 интегральных элементов. Корпус 2136.64-1.

Отличительной особенностью КМ1801ВМ3 являются большой объем адресуемой памяти, высокое быстродействие и возможность подключения сопроцессора арифметики чисел с плавающей запятой (СППЗ).

Основные параметры КМ1801ВМ3

| Объем адресуемой памяти | 4М байт |

| Принцип управления | Микропрограммный |

| Число команд | 72 с фиксированной запятой, 46 с плавающей запятой (при подключении СППЗ) |

| Число регистров общего назначения | 8 |

| Производительность операций «Регистр-регистр» (для КМ1801ВМ3А) | Сложение в потоке 1,5 млн операций/с; умножение 100 тыс. операций/с; деление 50 тыс. операций/с |

| Число линий запросов на прерывание | 4 |

| Тактовая частота | |

| КМ1801ВМ3А | 6 МГц |

| КМ1801ВМ3Б | 5 МГц |

| КМ1801ВМ3В | 4 МГц |

| Напряжение питания | 4,75…5,25 В |

| Выходное напряжение низкого уровня | 0,5 В |

| Выходное напряжение высокого уровня | 2,4 В |

| Входное напряжение низкого уровня | 0,7 В |

| Входное напряжение высокого уровня | 2,2 В |

| Ток утечки на входе | 1 мкА |

| Ток утечки на выходе | 10 мкА |

| Выходной ток низкого уровня | 3,2 мА |

| Выходной ток высокого уровня | -1,0 мА |

| Входная емкость | 10 пФ |

| Выходная емкость | 15 пФ |

| Емкость нагрузки | < 100 пФ |

| Мощность потребления | 1,5 Вт |

| Максимальное входное напряжение | 5,25 В |

| Минимальное входное напряжение | -0,5 В |

| Температура окружающей среды | -10…+70°С |

| Срок сохраняемости | 15 лет |

| Минимальная наработка | 50 000 ч |

Микросхема содержит шесть регистров общего назначения (R0—R5), три регистра — указателя стека R6 (SP), используемых в режимах операционной системы (KSP), пользователя (USP) и в пультовом режиме (HSP), и регистр R7, который служит также счетчиком команд (PC). Регистр SP содержит адрес последней заполненной ячейки стека, a PC — адрес команды, следующей за выполняемой.

Программно доступным регистром является также регистр состояния процессора PSW. Информация, содержащаяся в PSW, влияет на режимы выполнения команд и прерываний, определяет режим работы диспетчера памяти.

Регистр PSW доступен также из процессора по физическому адресу 17777776.

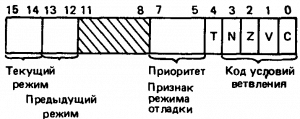

Назначение разрядов регистра PSW:

- разряды 0 — 3 (N, Z, V, С) — признаки знака, нуля, переполнения и переноса, описывающие результат последней выполненной команды;

- разряд 4 (Т) — признак режима отладки;

- разряды 5, 6, 7 — код приоритета внешних прерываний IRQ (3—0);

- разряды 13, 12 — предыдущий режим работы МП;

- разряды 15, 14 — текущий режим работы МП (11 — режим пользователя, 00 — режим операционной системы).

В микросхеме используются три типа команд безадресные, одноадресные и двухадресные. В безадресных командах код команды содержит только код операции. В кодах одноадресных и двухадресных команд содержится информация, определяющая; выполняемую функцию (код операции); регистры общего назначения, используемые при выборке операндов, метод адресации.

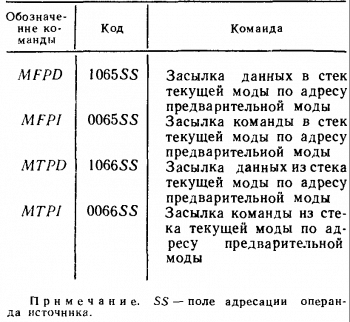

Система команд КМ1801ВМ3 включает команды МП КМ1801ВМ2 и дополнительные команды, которые приведены в таблице:

Диспетчер памяти обеспечивает:

- расширение емкости адресуемой памяти с 64К до 266К или до 4М байт;

- преобразование виртуальных адресов в физические и защиту памяти в системах с разделением времени;

- использование различных областей адресов для режима пользователя и режима операционной системы (ОС).

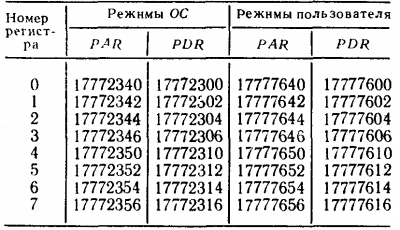

Расширение емкости адресуемой памяти осуществляется преобразованием 16-разрядного виртуального адреса в 18- или 22-разрядный физический адрес. Преобразование выполняется с помощью набора 16 регистров — адресов страниц PAR и 16 регистров — описателей страниц PDR.

Диспетчер памяти преобразует все адреса автоматически, поэтому пользователь работает в области виртуальных адресов. Область виртуального адреса делится на восемь отдельных страниц. Каждая виртуальная страница имеет свой код защиты. Есть три вида защиты памяти: разрешены запись и чтение, разрешено только чтение, запрещен любой доступ. Все попытки запрещенного доступа вызывают прерывание МП.

Диспетчер памяти обеспечивает три режима работы: ОС, пользователя и пультовый. Для каждого режима работы существует свой набор регистров PAR/PDR.

Регистры PAR/PDR включают два набора по восемь 27-разрядных регистров PAR/PDR для режимов ОС н пользователя и четыре 16-разрядных регистра адреса страницы PARH для обеспечения пультового режима. Физические адреса регистров PAR/PDR приведены и таблице:

При 18-разрядном физическом адресе базовый адрес страницы в регистре PAR содержится в разрядах 0—11, а при 22-разрядном — в разрядах 0—15.

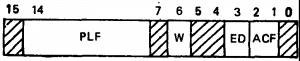

Формат регистра PDR имеет вид:

Поле PLF определяет длину страницы в блоках (один блок — 32 слова) и позволяет установить ее от 0 до 1778.

Разряд 3 (ED) — направление расширения страницы: при ED = 0 — расширение вверх, при ED = l — расширение вниз. При расширении вверх PLF устанавливается на 1 больше необходимой длины. При расширении вниз в PLF заносится дополнительный код длины страницы.

Поле ACF определяет тип доступа к странице памяти: 00 — недоступна, прерывание при любом обращении; 01 — доступна только по чтению, прерывание при попытке записи; 10 — не используется, прерывание при любом обращении; 11 — разрешены чтение и запись.

Разряд 6 (W)—признак записи, указывает, что в страницу произведена запись. Разряд W очищается автоматически при записи в PAR и PDR данной страницы. Установлен этот признак может быть только аппаратно логической схемой управления диспетчера памяти (ДП).

Регистры состояния диспетчера памяти

Диспетчер памяти содержит три регистра состояний: SR0, SR2, SR3. Четвертый регистр состояния SR1 аппаратно не реализован, и при обращении по адресу этого регистра (17777574) всегда считываются нули. В случае нарушения условия защиты памяти процессор немедленно прерывается и переходит к программе обработки прерывания по вектору 2508 в области памяти ОС. Регистры состояния SR0 и SR2 служат для анализа возникшего прерывания.

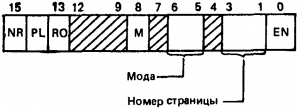

Регистр SR0 (адрес 17777572) содержит флаги ошибок, бит разрешения преобразования адреса в ДП и другую информацию, необходимую ОС для обработки ошибки и возврата к прерванной программе. Формат регистра SR0 имеет вид

Назначение разрядов регистра SR0:

- разряд 15 (NR) — ошибка по запрету доступа. Возникает при попытке обращения к недоступной или неиспользуемой странице; разряд 14 (PL) — ошибка по нарушению длины страницы;

- разряд 13 (RO) — ошибка по записи. Возникает при попытке записи в страницу, доступную только по чтению;

- разряд 8 (М) — бит, устанавливающий диагностический режим работы ДП; при установленном М выполняется преобразование адреса только последнего обращения в память приемника;

- разряды 5, 6 — режим МП (пользователя или ОС), при обращении к которому произошла ошибка ДП;

- разряды 1, 2, 3 — номер страницы, при обращении к которой произошла ошибка ДП;

- разряд 0 (EN) — бит включения ДП. При EN = 1 выполняются преобразование адресов и защита памяти в ДП.

Регистр SR2 (адрес 17777576) содержит виртуальный адрес первого слова выполняемой команды. Он не изменяется, если в данной команде произошло прерывание по ошибке ДП. Доступен только по чтению.

Регистр SR3 (адрес 1777757) содержит два разряда. Разряд 4 содержит бит AS. При AS = 1 адрес физический, 22разрядный, при АS = 0 — 18-разрядный. Разряд 5 содержит бит UM. При UM = 1 устанавливается для внешней аппаратуры режим включения схем преобразования адресов.

Формирование физического адреса в ДП изображено на рисунке:

В сумматоре выполняется сложение виртуального адреса VA (разряды 6 — 12) с выбранным PAR (разряды 0 — 11) при 18-разрядном адресе и PAR (разряды 0 — 15) при 22-разрядном адресе. В результате полный физический адрес содержит разряды 0 — 5 виртуального адреса и разряды 6 — 17 (21) — результат суммы.

Система прерываний процессора

Прерывания делятся на аппаратурные и командные. Часть аппаратных прерываний вызывает немедленный переход к их обработке. Это так называемые фатальные ошибки. Они возникают при ошибках системной магистрали, ДП, СППЗ. Анализ таких аппаратных прерываний, как авария источника питания, внешний сигнал HALT, прерываний IRQ (разряды 0 — 3), переполнения стека в моде операционной системы производится после завершения очередной команды в соответствии с приоритетом, указанным в таблице:

| Приоритет | Прерывание |

|---|---|

| Высший Самый низкий |

Команда HALT Нечетный адрес |

К командам прерывания относятся ЕМТ, TRAP, BPT, ЮТ, а также (если учитывать алгоритм выполнения) и резервные коды. Вектора прерываний приведены в таблице:

| Вектор | Прерывание |

|---|---|

|

004 |

Зависание, нечетный адрес, переполнение стека |

При прерывании МП помещает в стек PC и PSW и считывает новые значения PC и PSW из ячеек, определяемых вектором прерывания, причем загрузка PC и PSW ведется из области памяти операционной системы. Особый случай представляет собой возникновение фатальной ошибки в ходе выполнения микропрограммы обработки прерывания, так называемой «двойной ошибки». В этом случае процессор переходит в пультовый режим.

В пультовой режим процессор переходит при: выполнении команды HALT в моде ОС; возникновении «двойной ошибки»; возникновении внешнего сигнала HALT = 0 и отсутствии в этот момент других, более приоритетных прерываний.

При входе в пультовый режим процессор загружает в стек HSP константу 1000008; загружает в стек регистры PSW и PC; заносит в регистр PSW значение 3408, а в PC — 0; включает ДП на преобразование виртуальных адресов в

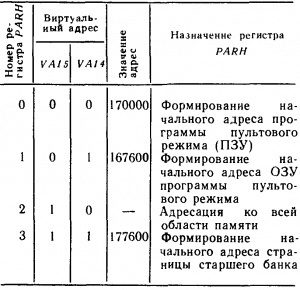

22-разрядные физические и переходит к выполнению программы, расположенной по виртуальному адресу 0. В ДП с целью реализации пультового режима введены четыре регистра адреса страницы PARH:

адресация к которым производится двумя старшими разрядами виртуального адреса. Регистр PARH2 позволяет осуществлять обращение ко всему адресному пространству путем записи в него соответствующего кода. Адрес регистра PARH2 — 177512.

В пультовом режиме существуют некоторые отличия в выполнении команд и прерываний. Например, команды RT1 и RTT выполняются без учета значения Т-бита.

При включении питания извне устанавливается сигнал DCLO и МП переходит в режим ожидания сигнала ACLO. При поступлении сигнала ACLO МП начинает выполнение одной из процедур начального пуска в зависимости от сигнала W0:

- W0 = 0. МП загружает PSW содержимым 26-й ячейки памяти, PC — содержимым 24-й ячейки и начинает выполнение программы с этого адреса;

- W0 = 1. МП загружает в PSW константу 340, а РС — 173000 и начинает выполнение программы с этого адреса.

При выполнении любой команды МП осуществляет хотя бы одно обращение к каналу, называемое циклом обращения к каналу. Перед каждым циклом МП осуществляет процедуру захвата канала.

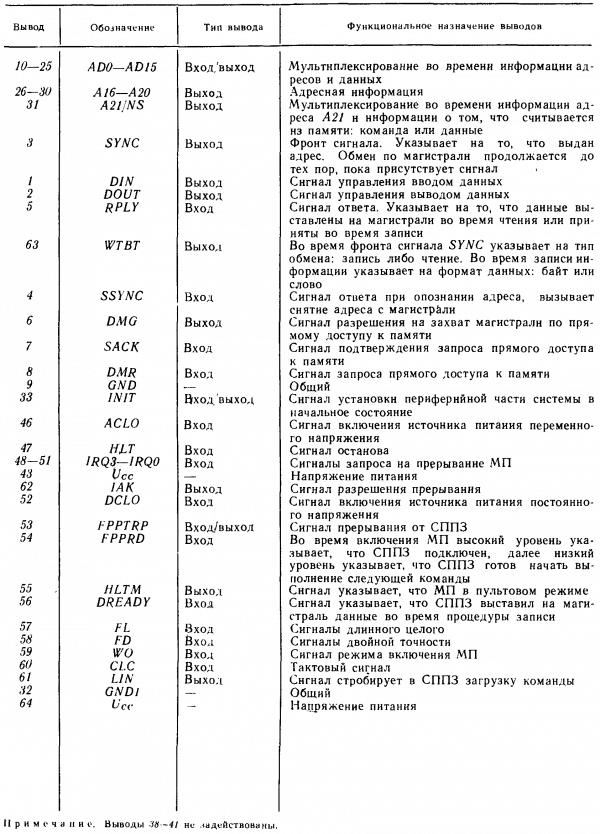

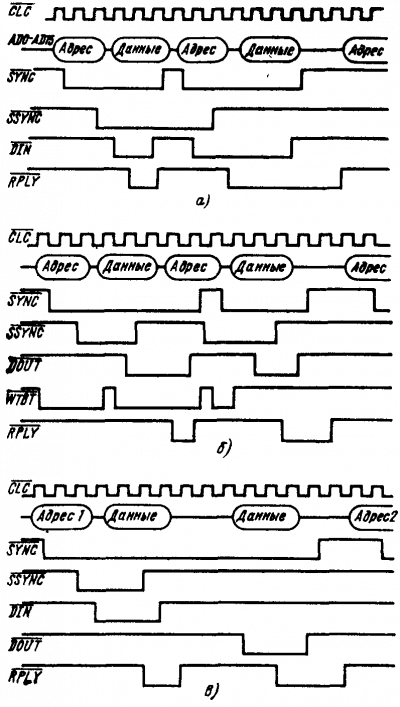

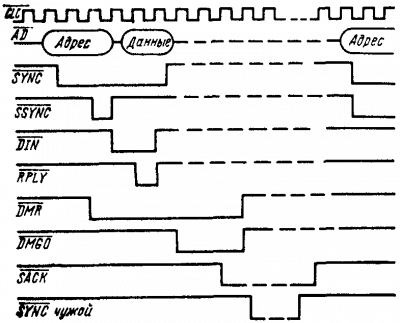

Цикл «Чтение». Цикл разделен на фазы передачи адреса и приема данных. Адрес из МП сопровождается сигналом SYNC, снимается после приема сигнала SSYNC, и затем выставляется сигнал DIN. Микросхема переключает элементы входа/выхода на выводах AD0 — AD15 на прием и ожидает сигнал RPLY. Фаза приема данных. После приема сигнала RPLY МП принимает данные и снимает сигналы DIN н SYNC.

Цикл «Запись». Передача адреса сопровождается сигналом WTBT, который снимается одновременно со снятием адреса и указывает, что происходит цикл «Запись». После окончания фазы передачи адреса МП выставляет на выводы AD0 — AD15 данные и сигнал DOUT и ожидает сигнал RPLY. После приема сигнала RPLY МП снимает сигнал DOUT, данные и сигнал SYNC. По снятию сигнала DOUT пассивное устройство снимает сигнал RPLY.

Цикл «Чтение — модификация — запись». Цикл разделен на фазы передачи адреса, приема и записи данных. Фаза записи начинается после того, как пассивное устройство сняло сигнал RPLY в ответ на снятие сигнала DIN.