Микро-80/Радио 1983-10/Модуль динамического ОЗУ

| Данный материал защищён авторскими правами!

Использование материала заявлено как добросовестное, исключительно для образовательных некоммерческих целей. Автор: Г. ЗЕЛЕНКО, В. ПАНОВ, С. ПОПОВ |

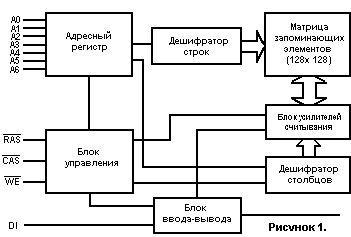

Описываемый модуль динамического ОЗУ, с которым Вы познакомитесь в этой статье, предназначен дли микро-ЭВМ с объемом памяти от 16 до 64. Кбайт. В модуле использована БИС динамического ОЗУ К565РУ3А. Эти микросхемы выполнены по n-МОП технологии и имеют информационную емкость 16384 бит с организацией 1024х1 разряд. Входные и выходных сигналы микросхемы совместимы по уровням напряжения с ТТЛ-микросхемами. Структурная схема БИС К565РУ3А показана на рис.1.

Основой микросхемы является матрица запоминающих элементов, способных хранить информацию в виде заряда. Для доступа к какому-либо запоминающему элементу матрицы необходимо выбрать соответствующую строку н столбец. Выбор происходит по сигналам дешифраторов строк и столбцов, которые подключены к семи младшим и семи старшим разрядам адресного регистра микросхемы.

Микросхема К565РУЗА имеет всего 16 выводов — один вывод общий, три вывода — для подключения питающих напряжении, два информационных: D1 и D0 — для ввода и вывода бита данных, и вывод WE — для управляющего сигнала записи бита данных в ячейку памяти. Оставшихся выводов не хватает для передачи на адресный регистр 14-разрядного кода адреса для выбора ячейки памяти (именно 214=16384бит). Поэтому код адреса заносится я адресный регистр последовательно — сначала через адресные входы А0-А6 микросхемы поступают коды семи младших, а затем семи старших разрядов адреса, сопровождаемые сигналами RAS (сигнал выборки строки) и CAS (сигнал выборки столбцов) соответственно.

Такой режим передачи кода называется мультиплексированным по времени. Мультиплексирование по времени часто применяют в БИС из-за «несоответствия» количества выводов у корпусов БИС и количества сигналов, которые необходимо обработать. Вспомните, что, например, шина данных в микропроцессоре также используется, в мультиплексном режиме. Кроме того, сейчас уже имеются БИС ОЗУ с информационной емкостью 64 Кбит и более, в которых также используется считывание бита из ячейки БИС ОЗУ происходит в момент действия сигнала CAS, если предварительно уже был установлен сигнал RAS. На время действии сигнала CAS информационный выход D0 микросхемы переходит из высокоимпедансного состояния в режим выдачи сигнала нулевого или единичного уровня, в зависимости от значения хранимого бита в ячейке, адресуемой содержимым адресного регистра. Если одновременно с сигналом CAS при предварительно установленном сигнале RAS действует сигнал WE, то бит данных с входи DI будет записан в ячейку памяти. При этом выход D0 микросхемы остается в высокоимпедансном состоянии в течение всего цикла записи.

Обращение к матрице запоминающих элементов для записи или чтения бита данных вызывает подключение к усилителям считывания одной строки матрицы запоминающих элементов, содержащей 128 ячеек памяти. При этом автоматически происходит подзаряд запоминающих конденсаторов всех ячеек памяти выбранной строки до исходного уровня. Этот процесс называется процессом регенерации памяти.

Для предотвращения разряда запоминающих конденсаторов ячеек памяти необходимо обращаться к каждой строке матрицы запоминающих элементов не реже чем через 2мс. При выполнении микропроцессором реальной программы это условие не соблюдается, так как обращение к одним ячейкам происходит часто, а к другим очень редко. Поэтому необходим специальный блок, ответственный за регенерацию памяти. Этот блок должен (естественно только в те моменты времени, когда к БИС ОЗУ нет обращений со стороны микропроцессора) циклически формировать на входах А0-А6 значения всех адресов от 00Н до 7FH. сопровождая каждое из них одним управляющим сигналом, RAS (то есть формировать адреса строк матрицы запоминающих элементов) с периодом не более 2мс.

Момент регенерации можно выбрать двумя путями. Во-первых, можно до начала регенерации приостановить работу микропроцессора, воздействуя на его вход ГТ. Получив ответный сигнал ОЖ, можно провести цикл регенерации. В нашем модуле динамического ОЗУ использован другой путь: регенерация происходит не в моменты останова микропроцессора, а в те моменты времени, когда в соответствии с временной диаграммой работы микропроцессора гарантировано отсутствие обращений к памяти. Такое решение позволяет избежать простоев микропроцессора, что особенно важно в микропроцессорных устройствах, управляющих какими-либо быстрыми процессами (то есть работающих в реальном масштабе времени). Однако из-за жесткой привязки к временной диаграмме рассматриваемый модуль не универсален — он может работать только с набором сигналов процессорного модуля, описанного ранее. Для хранения 8-разрядных данных БИС ОЗУ объединяются в блоки по 8 микросхем, каждый из которых обеспечивает хранение 16Кбайт информации. При этом соответственно объединяются и одноименные входы А0 — А6, RAS и WE всех микросхем модуля. Информационные входы DI и выходы БИС ОЗУ во всех блоках модуля объединены поразрядно и подключены к разрядным линиям шины данных микропроцессора. Выбор блоков для записи или чтения данных происходит по сигналам CAS, поступающим на одноименные входы микросхем, объединенных в блоки.

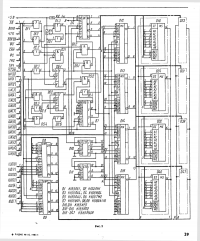

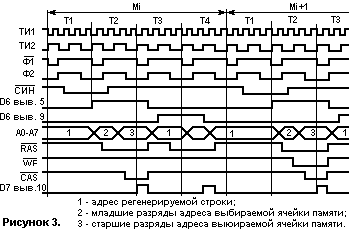

Принципиальная схема модуля динамического ОЗУ приведена на рис.2. Модуль содержит микросхемы памяти D16-D47 и блок управления. Последний включает узел формирования запросов обращения к памяти (элементы D1.1-D1.3, D2.1-D2.3, D3.1 и D6.1), узел формирования запросов регенерации памяти (элементы D2.5, D2.6, D5.3, D5.4 и D6.2). формирователь сигналов управления (элементы D2.4, D3.2, D4, D5.1, D5.2 и D7). формирователь шины данных (элементы D8 и D9), формирователь адреса регенерируемой строки (элементы D10 и D11) и коммутатор, обеспечивающий мультиплексирование сигналов с шины адресов микро-ЭВМ и формирователя адреса регенерируемой строки (элементы D12-D15). Временная диаграмма, поясняющая принцип работы модуля динамического ОЗУ. показана на рис.3.

В начале каждого машинного цикла микропроцессора, связанного с обращением к модулю динамического ОЗУ для записи или чтения информации, на его входы ЗВ, ВЫВ, ЧТП поступают сигналы, формируемые процессорным модулем. Обращение к модулю динамического ОЗУ подтверждается 1 на входе БЛКВХ модуля. При этом ни выходе элемента D1.3 появляется 1, поступающая на первый стробирующий вход V1 дешифратора D4. Этот же сигнал деблокирует по входу сброса R триггер D6.1 и поступает также на один из входов элемента D3.1. Последнее делает возможным установку по входу S триггера D6.1 при совпадении сигналов СИН и Ф1. поступающих на два других входа элемента D3.1, Поступление на вход С триггера D6.1 сигнала Ф2 не изменяет его состояния, так как на информационном входе D в это время присутствует сигнал СИН.

Установка триггера D6.1 вызывает появление 1 на управляющих входах А мультиплексоров D12-D15, разрешая прохождение адресных сигналов ША[0]-ША[6] с шины адресов микро-ЭВМ на соответствующие входы микросхем памяти. Одновременно с этим 1 с выхода триггера D6.1 поступает на первый вход элемента D5.1, а 0 с его инверсного выхода через элемент D5.2 поступает на вход последовательного занесения D0 сдвигового регистра D7, управляемого по счетным входам С1 и С2 тактовыми импульсами ТИ1, Вследствие этого по спаду очередного тактового импульса ТИ1 появляется 1 на первом выходе сдвигового регистра D7. которая через элемент D2.4 поступает на управляющие входы RAS. обеспечивая тем самым запись адреса строки выбираемой ячейки памяти с выходов мультиплексоров D12-D15 в адресные регистры микросхем памяти.

Спад следующего тактового импульса ТИ1 вызывает появлении 1 на втором выходе сдвигового регистра D7, связанного с управляющими входами В мультиплексоров D12-D15. Это обеспечивает прохождение сигналов ША[7]-ША[15] с шины адресов микро-ЭВМ на адресные входы микросхем памяти.

Одновременно сигнал со второго выхода сдвигового регистра D7 поступает на третий вход элемента D3.2 для формирования на его выходе управляющего сигнала WE для записи информации в микросхемы памяти.

Спад третьего тактового импульса ТИ1 вызывает появление 1 на третьем выходе сдвигового регистра D7. Этот сигнал поступает на второй вход элемента D5.1 и далее на стробирующий вход V2 дешифратора D4 для формирования управляющих сигналов CAS для одного из блоков микросхем памяти в зависимости от комбинации адресных сигналов ША[14] и ША[15] на его входах D1 и D2. Поступление управляющих сигналов CAS на входы микросхем памяти соответствующих блоков вызывает запись или считывание информации с шины данных микро-ЭВМ в зависимости от состояния сигнала на входах WE. Прохождение данных от микросхем памяти к шине данных микро-ЭВМ или в обратном направлении определяется управляющими сигналами, поступающими на входы ВШ и ВМ шинных формирователей D8 и D9.

Спад четвертого тактового импульса ТИ1 вызывает появление 1 на четвертом выходе сдвигового регистра D7, связанном с его управляющим входом V. Вследствие этого сдвиговый регистр D7 переходит из режима сдвига информации в режим параллельного занесения информации. Таким образом, по спаду следующего тактового импульса ТИ1 информация заносится по входам D1-D4 в сдвиговый регистр D7. При этом на его выходах будет присутствовать низкий уровень, что прекращает действие управляющих сигналов RAS'WE' и САS. Одновременно с этим поступление очередного импульса Ф2 переключает триггер D6.1 в 0, снимая запрос на обращение к модулю динамического ОЗУ. Сброс триггера D6.1 и появление сигналив 0 на управляющих входах В мультиплексоров D12-D15 вызывает прохождение на их соответствующие выходы адреса очередной регенерируемой строки с выходов двоичных счетчиков D10 и D11.

При отсутствии обращений микропроцессора к памяти формируются управляющие сигналы регенерации. В зависимости от длительности текущего машинного цикла до очередного обращения микропроцессора к памяти может быть выполнен один или несколько циклов регенерации.

Отсутствие сигнала на входе СИН модуля динамического ОЗУ и сброс триггера D6.1 вызывают появление нулевого уровня на выходе элемента D5.3. который поступает на информационный вход D триггера D6.2. Совпадение сигналов ТИ2 и Ф2 вызывает установку по входу С а 0 триггера D6.2. Сигнал низкого уровня с выхода триггера через элемент D5.2 поступает на вход последовательного занесения DO сдвигового регистра D7, цикл работы которого аналогичен циклу в режиме обращения к памяти для записи или чтения данных. При этом 0 на выходе триггера D6.1 запрещает формирование управляющих сигналов WE к CAS.

При завершении цикла регенерации уровень 1 с четвертого выхода сдвигового регистра D7 через элемент D2.6 переводит триггер D6.2 в другое устойчивое состояние, что вызывает переключение по счетному входу С1 двоичного счетчика D10 и изменение адреса регенерируемой строки.

Для совместного использования в микро-ЭВМ модуля динамического ОЗУ и комбинированного модуля ОЗУ-ПЗУ, часть адресов которых совпадают, в описываемом модуле предусмотрена возможность блокировки запроса обращения к памяти. Для этого на вход БЛКВХ модуля динамического ОЗУ должен быть подан сигнал низкого уровня с выхода БЛКВЫХ комбинированного модуля ОЗУ-ПЗУ. При этом запрос обращения к памяти для записи или чтения данных не формируется и модуль продолжает работать в режиме формирования управляющих сигналов регенерации.

Питание модуль динамического ОЗУ получает от трех источников питания — +5В, +12В и −5В, потребляемые токи не превышают соответственно 1А, 1,50мА и 0,1мА. Порядок включения и выключения питающих напряжений соответствует использованному в процессорном модуле. Ни в коем случае нельзя допустить отсутствие одного из питающих напряжений. В связи с особенностями работы динамических БИС ОЗУ, вызывающих значительные импульсные помехи в цепях питания, в конструкции модуля должны быть предусмотрены развязывающие керамические конденсаторы с низкой индуктивностью и небольшими габаритами. В цепях +12В и −5В следует устанавливать соответственно конденсаторы 0,33 и 0,1мкФ (по одному на каждые две микросхемы памяти). В цепи питания +5В рекомендуется устанавливать конденсаторы емкостью 0,1мкФ на каждые восемь микросхем памяти. Дополнительно на плате целесообразно установить электролитические конденсаторы емкостью 4,7мкФ в цепи питания +12В. Особо следует обратить внимание на то. что при выполнении монтажа (в том числе и печатного) проводники, связывающие одноименные выводы микросхем памяти, должны иметь минимальную длину.

F000 210000 LXI H, ADR ;3АПИСАТЬ АДРЕС ЯЧЕЙКИ ПАМЯТИ F003 3E55 MVI A, 55H ; ЗАДАТЬ КОНСТАНТУ ДЛЯ ЗАПИСИ В ПАМЯТЬ F005 77 ЦИКЛ: MOV M, A ;ЗАПИСАТЬ КОНСТАНТУ В ПАМЯТЬ F006 46 MOV В, М ;ЧИТАТЬ ИЗ ЯЧЕЙКИ ПАМЯТИ F007 2F СМA ;ИЗМЕНИТЬ КОНСТАНТУ F008 C305F0 JMP ЦИКЛ ; ПОВТОРИТЬ ЗАПИСЬ-ЧТЕНИЯ Е000 ADR: EQU 0000Н ; ОПРЕДЕЛЕНИЕ АДРЕСА ЯЧЕЙКИ ДИНАМИЧЕСКОЙ ПАМЯТИ

Рис.4

Отладку модуля динамического ОЗУ целесообразно выполнять на уже действующей микро-ЭВМ. При этом микропроцессор должен выполнять программу поочередной записи и считывания произвольного байта данных в одну из ячеек динамического ОЗУ (рис.4). Для контроля работоспособности модуля динамического ОЗУ используется осциллограф, синхронизируемый сигналом «Синхро», выведенным на панель технического пульта. При этом на его тумблерном регистре А0-А15 должен быть установлен адрес ячейки памяти динамического ОЗУ, к которой происходит обращение. Анализ состояния сигналов в характерных точках динамического ОЗУ и сравнение с временной диаграммой, представленной на рис.3, позволит выявить неисправности и устранить их.

Убедившись в правильной записи и считывании информации в одну из ячеек динамической памяти следует проверить работу всего модуля динамического ОЗУ с помощью теста, содержащегося в программе «монитор», с которой мы познакомим Вас в следующей статье.

Г. ЗЕЛЕНКО, В. ПАНОВ, С. ПОПОВ

Отсканировано с журнала Радио № 10 1983 г.

Отредактировано Лесных Ю. И. 1999 г.