Ириша/Модуль контроллера НГМД RTV*001.89 ТО

| Данный материал защищён авторскими правами!

Использование материала заявлено как добросовестное, исключительно для образовательных некоммерческих целей. Источник: http://oldpc.su/pc/Irisha/irisha.html |

ПЭВМ "ИРИША-М" МОДУЛЬ КОНТРОЛЛЕРА НГМД «RTV*001.89» (Техническое описание)

АННОТАЦИЯ

Настоящий паспорт, объединённый с техническим описанием и инструкцией по эксплуатации, является документом, удостоверяющим гарантированные изготовителем основные параметры и технические характеристики модуля КНГМД «RTV*001.89».

Кроме того, настоящее руководство позволяет ознакомиться с устройством и принципом работы модуля КНГМД и устанавливает правила его эксплуатации, соблюдение которых обеспечивает постоянную готовность модуля к работе.

1. Назначение и основные технические характеристики модуля контроллера НГМД «RTV*001.89»

1.1. Модуль контроллера накопителей на гибких магнитных дисках (НГМД) «RTV*001.89» предназначен для оснащения ПЭВМ «ИРША» или её модификаций накопителями на гибких магнитных дисках.

1.2. Модуль позволяет работать с одно- или двухсторонними механизмами НГМД, имеющими стандартный интерфейс SHUGART. Одновременно контроллер может обслуживать до 2-х накопителей 133 мм и 75 мм формата, обеспечивающих двойную плотность записи (MFM).

1.3. Модуль позволяет расширить объем ОЗУ базовой модели ПЭВМ на 128-512 К байт в зависимости от типа установленных микросхем динамической памяти (К565РУ5, К565РУ71, К565РУ72, К565РУ7 в различных комбинациях).

1.4. Модуль содержит 3 розетки для установки микросхем ПЗУ типа К573РФ4 (К573РФ6) или К573РФ7. Допускается также применение микросхем ПЗУ иностранного производства: I2764, I2728 или I27256. Общий объем постоянной памяти модуля может изменяться от 8 до 96 К байт.

1.5. Модуль занимает 26 адресов в адресном пространстве ПЭВМ. Доступ процессора и памяти модуля осуществляется через два «окна» по 16 К каждое, в общем адресном пространстве процессора под контролем схемы управления расширением памяти.

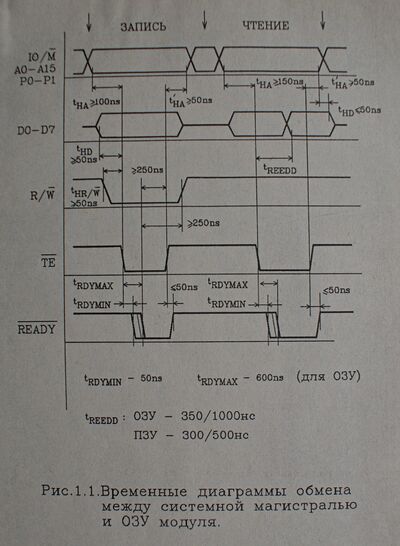

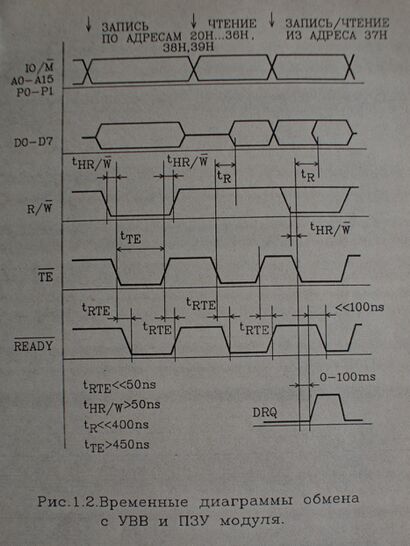

1.6. Временные диаграммы обмена информацией с модулем через системную магистраль приведены на рис. 1.1, 1.2.

1.7. Питание модуля осуществляется от двух источников питающих напряжений +5 В (1 А) и +12 В (100 мА), без учета тока потребления механизмами НГМД.

1.8. Конструктивно модуль контроллера представляет собой печатную плату размером 230×150×23 мм. Модуль снабжен устройством его монтажа в системный блок ПЭВМ. На задней панели модуля находится разъем (Х2: вилка СН053-60-23) для подключения механизмов НГМД. Назначение его сигналов приведено в табл. 1.1.

| Контакт | Сигнал | Назначение | Примечание |

|---|---|---|---|

| 4-56 чётные | ОВ | Общий вывод | |

| 3 | MOT.ON1 | Включение двигателя B | к НГМД |

| 7 | INDEX | Индекс | от НГМД |

| 9 | DR.SEL0 | Выбор дисковода А | к НГМД |

| 11 | DR.SEL1 | Выбор дисковода В | к НГМД |

| 15 | MOT.ON0 | Включение двигателя А | к НГМД |

| 17 | DIRECTION | Направление перем. гол. | к НГМД |

| 19 | STEP | Шаг перемещения гол. | к НГМД |

| 21 | WR.DATA | Данные для записи | к НГМД |

| 23 | WR.EN | Разрешение записи | к НГМД |

| 25 | TRACK0 | Дорожка 00 | к НГМД |

| 27 | WR.PROT. | Защита записи | от НГМД |

| 29 | RAW.READ | Данные чтения | от НГМД |

| 31 | SIDE SEL. | Выбор рабочей стороны | от НГМД |

| 33 | READY | Готовность | от НГМД |

| 35 | FAULT RES. | к НГМД | |

| 37 | FAULT | от НГМД | |

| 39 | TWO SIDES | от НГМД | |

| 58, 60 | +12B | Питание двигателя НГМД | к НГМД |

| 59 | +5B | Питание схемы НГМД | к НГМД |

| 1, 22, 5, 13, 41-55 неч. | Не используются |

2. Порядок установки модуля контроллера в ПЭВМ и работа с ним

2.1. Для монтажа модуля контроллера «RTV*001.89» в ПЭВМ необходимо вынуть его из упаковки, проверить правильность установки перемычек и микросхем ПЗУ, а затем установить модуль в системный блок ПЭВМ на любое свободное место, зафиксировав его винтами.

2.2. Заводом-изготовителем модуль поставляется настроенным с помощью перемычек на работу со 133 мм НГМД с двойной плотностью записи. Перемычки выбора типа микросхем памяти ПЗУ должны быть настроены на работу с микросхемами К573РФ4 или К573РФ6 или их зарубежным аналогом I2764. Число рабочих сторон и дорожеек на диске от типа поставляемого дисковода и указывается в сертификате на панели модуля.

2.3. Схема расположения перемычек на модуле показана на рис. 2.1. Они показаны в таком положении, в каком должны находиться после выпуска и настройки модуля изготовителем. В розетке Х6 должна быть установлена микросхема D52 (К573РФ4 или К573РФ6)с "прошитой" в нее программной ядра операционной системы *RTV*CP/M 20.

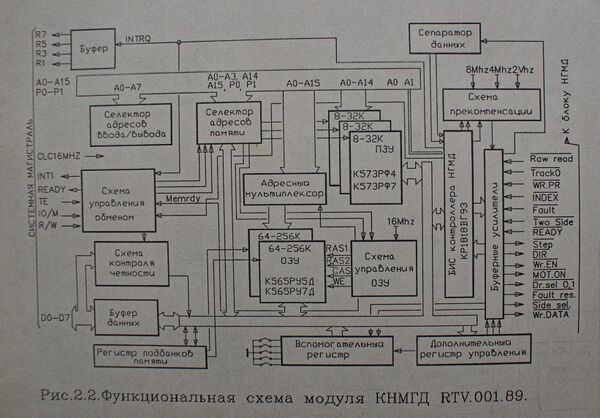

2.4. Для разбора порядка работы с модулем контроллера НГМД рассмотрим его внутреннюю организацию, показанную на функциональной схеме, которая приведена на рис. 2.2.

2.5. Модуль содержит в своем составе интерфейсный узел с расширенным ПЗУ, узел ОЗУ и узел собственно контроллера НГМД. Со стороны процессора модуль предстален как набор на 26 регистров в области адресов ввода-вывода системной магистрали (20Н-39Н) и как один или несколько банков памяти протяженностью до 64 К байт. Назначение адресов ввода-вывода приведено в таблице 2.1.

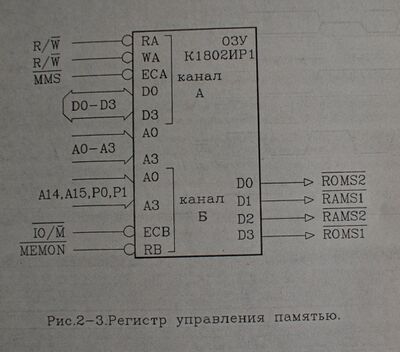

2.6. Селектор адресов памяти выполнен на базе БИС 2-х входового ОЗУ, представляющего собой с точки зрения программиста, регистровый файл из 16-ти четырехбитных регистров (рабочие адреса - 20Н - 2FH). Лог. "0" в любом из битов означает включение в работу одного из банков ОЗУ или ПЗУ. Естественно, ситуация, при которой в любом из регистров содержится более одного логического нуля, является ошибочной и должна быть исключена при работе с модулем. Номер каждого из регистров отвечает за определенный сегмент памяти системной магистрали. Так: регистр с адресом 20Н отвечает за страницу памяти системной магистрали в нулевой странице, начиная с адреса 0000Н до 3FFFH. Упрощенная схема регистра показана на рис. 2.3.

Если требуется включить в эту область ОЗУ или ПЗУ, то в соответствующий бит регистра с этим номером должна быть занесена информация с нулем в одном из битов включения памяти. В табл. 2.1 приведено соответствие номеров регистров с адресами памяти системной магистрали.

| Адрес | Тип операции | Назначение | Примечание |

|---|---|---|---|

| 20Н | Запись/чтение | Рег. 0 (00000Н) | Файл управления ОЗУ |

| 21Н | Рег. 1 (04000Н) | ||

| 22Н | Рег. 2 (08000Н) | ||

| 23Н | Рег. 3 (0С000Н) | ||

| 24Н | Рег. 4 (10000Н) | ||

| 25Н | Рег. 5 (14000Н) | ||

| 26Н | Рег. 6 (18000Н) | ||

| 27Н | Рег. 7 (1С000Н) | ||

| 28Н | Рег. 8 (20000Н) | ||

| 29Н | Рег. 9 (24000Н) | ||

| 2АН | Рег. 10 (28000Н) | ||

| 2ВН | Рег. 11 (2С000Н) | ||

| 2СН | Рег. 12 (30000Н) | ||

| 2DН | Рег. 13 (34000Н) | ||

| 2EН | Рег. 14 (38000Н) | ||

| 2FН | Рег. 15 (3С000Н) | ||

| Регистры управления НГМД | |||

| 30Н | Запись | Регистр команд | БИС КНГМД КР1810ВГ93 |

| Чтение | Регистр статуса | ||

| 31Н | Запись/чтение | Регистр номера трека | |

| 32Н | Регистр номера сектора | ||

| 33Н | Регистр данных. Обмен без схемы автосинхронизации | ||

| 34Н | Запись | То же, что в 30Н | |

| Чтение | То же, что в 30Н | ||

| 35Н | Запись/чтение | То же, что и 31Н | |

| 36Н | То же, что и 32Н | ||

| 37Н | Регистр данных. Схема автосинхронизации включена | ||

| Служебные регистры | |||

| 38Н | Запись | Дополнительный регистр управления модулем | |

| Чтение | Вспомогательный регистр состояния модуля | ||

| 39Н | Запись | Регистр выбора подбанка ОЗУ | |

| Чтение | Регистр состояния триггера контроля ошибки чтения | ||

2.7. При включении машины состояние регистрового файла неопределено и информация в нем должна быть сформирована стартовой программой инициализации. Чтобы не было ложных включений памяти при "холодном" старте, специальная схема блокирует работу памяти модуля до первого обращения к дополнительному регистру управления с адресом 38Н. Программа начального старта должна сначала записать в файл управления необходимую информацию, а затем включить память модуля в работу, записав байт управления в регистр с адресом 38Н. Информация в регистровой файл может как записываться, так считываться из него.

2.8. При использовании модуля в составе ПЭВМ "ИРША-М" с операционной системой СР/М 2.2 память модуля размещается в первой странице с адресом 10000Н до 1FFFFH. Поскольку размер этой страницы равен 64 К байт, для работы с полным объемом памяти используется внутреннее переключение банков путем перезаписи содержимого файла управления.

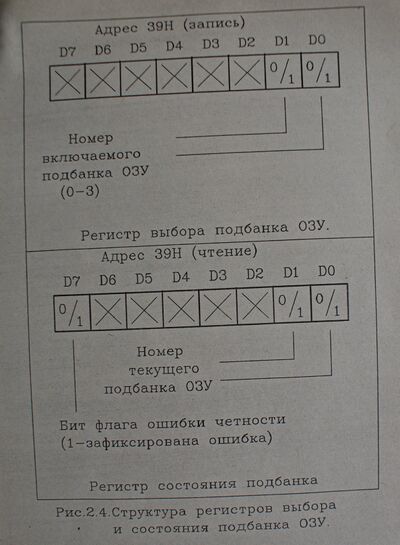

2.9. Для работы с ОЗУ емкостью до 512 Кбайт модуль содержит дополнительный регистр - регистр выбора подбанка (адрес - 39Н), при помощи которого внутри выбранного банка памяти организуются 4 подбанка размером 64 К байт. Указанный регистр доступен как для записи, так и для чтения.

2.10. Модуль контролирует информацию, записанную в ОЗУ по четности в каждой байте. При обнаружении ошибки включается триггер ошибки памяти, состояние этого триггера может быть считано из регистра с адресом 39Н (бит D7). Сброс триггера осуществляется при выполнении операции записи в регистр выбора подбанка, имеющий такой же адрес (39Н). Структура этого регистра показана на рис. 2.4.

2.11. Управление механизмом НГМД осуществляется БИС КНГМД. Работа с этим БИС осуществляется через 8 регистров, (рабочие адреса - 30Н-37Н), причем 6 из них имеют попарно одинаковые функции (30Н и 34Н; 31Н и 35Н; 32 и 36Н). Назначение регистров БИС КНГМД показано в табл. 2.1. Разница между регистрами с адресом 33Н и 37Н заключается в том, что при обращении к адресу 37Н запускается в работу система автосинхронизации обмена данными по получению сигналов DRQ и INTRQ от БИС КНГМД. Более подробно ознакомиться с назначением регистров можно в описании БИС КНГМД, приведённом в приложении А настоящего описания.

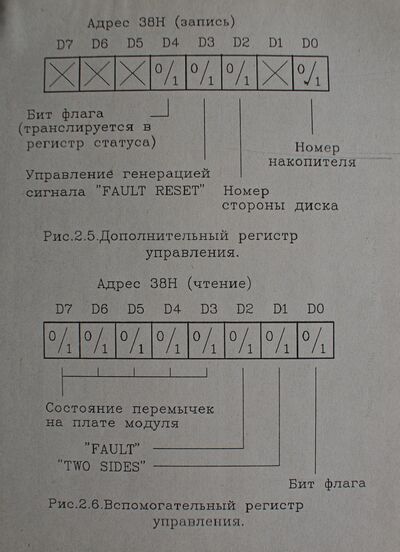

2.12. Кроме регистров БИС КНГМД, модуль имеет дополнительный регистр управления и вспомогательный регистр статуса. Их структура показана на рис. 2.5 и рис. 2.6. Через дополнительный регистр управления могут программироваться номер рабочего накопителя, номер стороны диска и некоторые другие функции.

2.13. В настоящем техническом описании не рассматриваются вопросы о способах и форматах записи на магнитный диск, а также организация работы операционной системы СР/М с контроллером. С этими вопросами пользователь может ознакомиться самостоятельно в специальной литературе.

3. Устройство и работа модуля

3.1. В модуле контроллера «RTV*001.89» можно выделить три основные части:

- узел контроллера НГМД;

- узел оперативной памяти;

- интерфейсная часть с дополнительным ПЗУ.

Информационное взаимодействие узлов между собой осуществляется через внутреннюю магистраль.

3.2 Узел контроллера НГМД

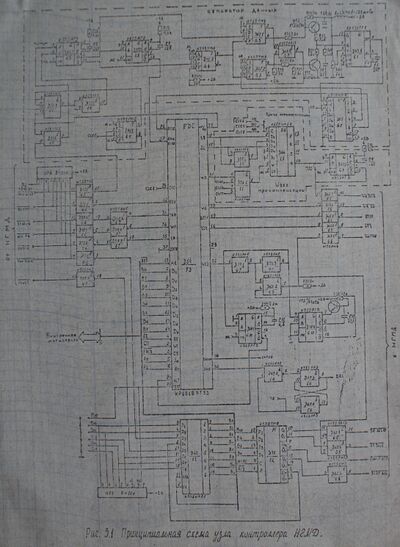

3.2.1. Узел контроллера НГМД выполнен на базе БИС КР1818ВГ93 (аналог микросхемы WD1793 фирмы Western Digital). Упрощённая схема узла приведена на рис. 3.1.

3.2.2. БИС КР1818ВГ93 содержит все необходимое для управления работой маханизмами накопителей и цепи, выполняющие преобразование потока байтов данных из ЭВМ в соответствующую последовательность битов для записи на диск, а также цепи обратного преобразования. БИС позволяет работать как с одинарной (FM), так и с двойной плотностью записи (MFM), но в данной конкретной реализации БИС КНГМД используется только в режиме с двойной плотностью записи (MFM). Однако, для работы БИС требуются внешние схемы сепаратора данных и прекомпенсации, цепи выбора накопителя и рабочей стороны диска.

3.2.3. Выход сигналов на интерфейс дисковых накопителей осуществляется через буферные усилители на мощных формирователях с открытым коллектором D62 и D68. Приём сигналов с дискового интерфейса производится через буферные микросхемы D58 и D59. Сигнал READY подаётся непосредственно на одноименный вход БИС (вывод 32). Сигнал чтения данных RAW.READ поступает на вход сепаратора данных. Состояние линии FAULT и TWO SIDES транслируется на входы вспомогательного регистра состояния и может быть проанализировано процессором по адресу 38H (биты D2, D1; см. рис. 2.6.).

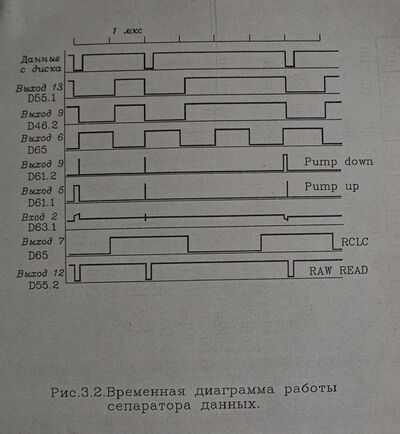

3.2.4. Схема сепаратора данных (далее сепаратор данных) выполнена на микросхемах D46, D55-D57 и D61-D63. Сепаратор данных вырабатывает сигнал синхронизации чтения данных RCLC, подаваемый на соответствующий вход БИС КНГМД (вход 26). Фронты этого сигнала располагаются между импульсами данных, считываемых с диска.

Выходном формирователь собран на одновибраторе D55.2, запускающемся отрицательным фронтом импульсов входного потока данных. Он вырабатывает импульсы длительностью около 1 мкс, необходимые для работы фазового компаратора, который собран на микросхемах D46-2, D61, D62-3. Фазовый компаратор сравнивает частоту и фазу сигнала входного потока данных с сигналом генератора, управляемого напряжением (ГУН), и по их разнице вырабатывает соответствующий сигнал управления. ГУН выполнен на микросхеме КР531ГГ1 (D63). Средняя частота ГУН равна 4 МГц. Выходной сигнал ГУН подается на делитель частоты (микросхема D65), с выводов которого снимаются сигналы 500 кГц для фазового компаратора и 250 кГц для подачи на вход RCLC.

При отсутствии обращения к диску (на выходе 33 БИС КР1818ВГ93 - высокий уровень) на вход сепаратора данных подается сигнала опорной частотью 500 кГц, устанавливающий частоту ГУН вблизи заданного значения.

Переменный резистор R26 служит для установки средней частоты ГУН. Средняя частота 4 МГц должна вырабатываться при напряжении на входе 3 микросхемы ГУН около 3.3 В.

Рис. 3.2 поясняет работу схемы сепаратора данных.

3.2.5. Схема прекомпенсации работает при записи информации на диск. Она выполнена на сдвиговом регистре D66 и элементах D56.1 и D57.1. Управление работой схемы осуществляется самой БИС КНГМД с помощью сигналов SR (выход 18) и SL (выход 17). При высоком уровне сигнала SR положение информационного импульса в выходном потоке задерживается в зависимости от положения перемычек П20, П21 и П22 на 125-250 или 500 нс, соответственно. При высоком уровне на выходе SL дополнительный импульс выдается на аналогичное время раньше. Если оба сигнала неактивны, то изменение положения импульса не производится.

На выходе схемы прекомпенсации установлен выходной формирователь D67.2, фиксирующий длительность импульсов записи в районе 250-300 нс независимо от времени прекомпенсации. Если время прекомпенсации устанавливается равным 250 нс, то выходной формирователь может не устанавливаться. В этом случае перемычка П23 должна быть замкнута.

3.2.6. БИС КНГМД вырабатывает сигнал для включения двигателя накопителя HLD (выход 28). Этот сигнал запускает одновибратор задержки D70-1, блокирующий через ввод HLT (вывод 23) БИС отработку алгоритма выполнения команды на время разгона двигателя. Двигатель включается сразу же при получении команды, но одновибратором D70-2 удерживается во включенном состояния еще 2-3 сек. Если за этот промежуток времени обращения к диску не было, то его двигатель выключается. В противном случае - одновибратор перезапускается и двигатель остается во включенном состояния. В запущенном состоянии одновибратор D70-2 блокирует одновибратор задержки D70.1 на время разгона двигателя, что обеспечивает максимальную скорость работы с диском. Таким образом, при частых обращениях к диску двигатель его механизма постоянно включен и никаких дополнительных задержек не возникает. Кроме того, указанная схема уменьшает число разгонов двигателя, при которых потребляется повышенный ток.

3.2.7. Выбор накопителя и выбор рабочей стороны диска производится через дополнительный регистр управления D71 (адрес обращения 38Н - см. рис. 2.5). Поскольку многие типы накопителей не имеют возможности индикации состояния, когда двигатель накопителя включён, а индицируют только выбор накопителя, то соответствующие сигналы выбора стробируются на выходных формирователях D62 сигналом включения мотора MOT.ON. Таким образом, сигналы выбора накопителя активны только при обращении к диску.

3.2.8. Контроллер «RTV*001.89» имеет ряд отличий от аналогичного модуля контроллера «RTV*070.87» в котором описываемый узел выполнен на базе БИС WD2793 импортного производства. Контроллер «RTV*001.89» в отличие от контроллера «RTV*070.87», работающего со всеми типами дисков, может обслуживать только два накопителя на 133 мм или 75 мм дисках. Он работает только с двойной плотностью записи на диск (MFM). Однако, указанные ограничения, не сказываются на эксплуатационных характеристиках стандартных комплектов ПЭВМ "ИРИША-М".

3.3. Узел ОЗУ модуля

3.3.1. Модуль КНГМД «RTV*001.89» содержит от 128 до 512 К байт оперативной памяти (ОЗУ), обычно используемой для организации электронного диска. Это ОЗУ выполнено на БИС динамической памяти К565РУ5Д (ёмкость 64 К бит), К565РУ71Д или К565РУ72Д (ёмкость 128 К бит) или К565РУ7Д (ёмкость 256 К бит). Возможно также применение и более быстродействующих микросхем памяти серии К565 с последними буквами "Г", "В", или "Б". В зависимости от типа устанавливаемых микросхем будет изменяться и общий объем ОЗУ моделя. С точки зрения программиста это ОЗУ представляет несколько банков памяти, которые могут включаться на любое из мест адресного пространства системной магистрали. Принципиальная схема узла ОЗУ приведена на рис. 3.3.

3.3.2. Микросхемы динамической памяти используют принцип мультиплексирования входного адреса, который передаётся в два приема: сначала передаётся 8-ми или 9-ти разрядный адрес строки, а затем - адрес столбца той же разрядности. Девятибитные адреса используются при применении памяти К565РУ7Д емкостью 256 К бит. Для реализации механизма мультиплексной передачи требуются два вспомогательных стробирующих сигнала: RAS (Row address strobe) и CAS (Column address strobe). Временные соотношения между сменой частей адреса и стробирующих сигналов достаточно жестко детерминированы.

Особенность динамической памяти является то, что её содержимое необходимо периодически регенерировать. Этот процесс реализуется либо выполнением 128 циклов чтения за 1 или 2 мс с перебором всех адресов столбцов, либо выполнением такого же числа циклов, но без подачи сигнала CAS. Время регенерации определеяется быстродействием микросхем примененной памяти. Для микросхем с последней буквой "Д" эта время составляет 1 мс, для всех остальных типов оно равно 2 мс. Регенерация можно производить лавинно, когда последовательно выполняются все циклы с исключением возможности доступа к памяти со стороны внешних устройств или распределенно, когда циклы регенерации вставляются между циклами обращения к памяти. В последнем случае, учитывая, что процессор не обращается к памяти в каждом возможном его цикле, прозрачность доступа может быть обеспечена максимально возможной. Среднее время между циклами регенерации во втором случае должно быть около 8 мкс для микросхем с 1 мс временем регенерации и около 16 мкс для остальных типов микросхем. В описываемом модуле используется более прогрессивный второй принцип регенерации. Переключение времени регенерации производится перестановкой перемычек П13 и П12.

3.3.3. Указанные особенности БИС динамической памяти требуют для их работы специальной схемы обрамления, задающей временные соотношения между сигналами синхронизации и управления. Обычно такую схему называют контроллером ОЗУ. Контроллер ОЗУ, кроме указанной выше функции, осуществляет арбитраж между запросами на регенерацию и обмен информацией с внешней магистралью.

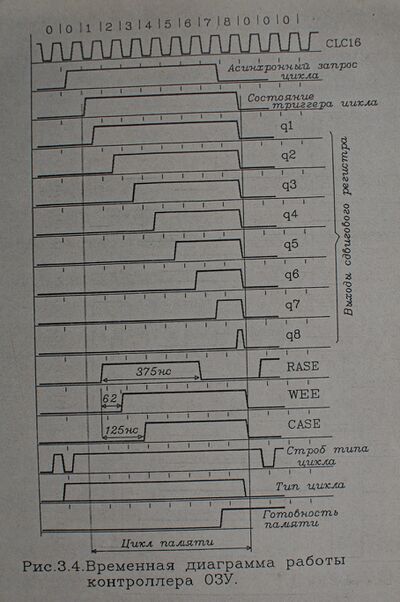

3.3.4. Контроллер ОЗУ включает в себя четыре триггера управления (микросхемы D37 и D39), сдвиговый регистр (микросхемы D35 и D36), таймер регенерации D47 и некоторую логику обрамления. Он работает следующим образом: при отсутствии обращений триггер запроса находится в неактивном состоянии, а его низкий выходной уровень блокирует по входу «Сброс» работу сдвигового регистра D35 и D36, задающего временные сдвиги между сигналами синхронизации. Запросы цикла памяти поступают либо от триггера запроса (сигнал MEM), либо от таймера регенерации (сигнал RFSH). При получении какого-либо запроса по заднему фронту тактирующего сигнала CLC16M активируется триггер запроса, снимается сигнал «Сброс» со сдвигового регистра и начинается выполнение цикла памяти. Одновременно триггер типа цикла D37-2 фиксирует, какой именно цикл должен выполняться: цикл памяти или цикл регенерации. Во время исполнения цикла памяти сигнал синхронизации на триггер типа цикла не подается, и таким образом изменение его состояния в этот период блокировано. После снятия блокирующего сигнала со сдвигового регистра в него по каждому положительному фронту тактирующего сигнала CLC16M начинает «вдвигаться» логическая единица. По мере заполнения регистра единицами формируются необходимые сигналы управления и синхронизации. После восьми тактирующих импульсов сигнал с выхода сдвигового регистра сбрасывает триггер запроса, обнуляет сдвиговый регистр, и цикл памяти завершается. Временная диаграмма, иллюстрирующая этот процесс, приведена на рис. 3.4.

Запрос регенерации RFSH имеет более низкий приоритет по сравнению с запросом со стороны процессора, поэтому при одновременном поступлении обоих запросов сначала будет выполняться цикл памяти. Если какой-либо запрос поступает во время выполнения цикла, то арбитраж производится только по завершении текущего цикла памяти.

В циклах регенерации с помощью микросхем D48 и D50 формирование сигналов CAS и WE запрещается. Кроме того, в циклах указанного выше типа сигнал RAS вырабатывается для обоих банков памяти одновременно. Это означает, что регенерация информации в обоих банках также выполняется одновременно. При обмене информацией с ОЗУ модуля сигнал RAS формируется только для рабочего банка, и, таким образом, осуществляется их селекция.

3.3.5. В узел ОЗУ входит счётчик D45, вырабатывающий сигналы опорных частот для контроллера ОЗУ и узла контроллера НГМД. На этот счётчик подаётся сигнал опорной частоты 16 МГц с системной магистрали ПЭВМ.

3.3.6. Запросы на обращение к памяти поступают с системной магистрали асинхронно, поэтому для организации обмена данными с ней требуются ещё два триггера D39: триггер запроса и триггер готовности. Триггер запроса D39-1 фиксирует требование на обмен информацией с памятью (активен высокий уровень сигнала MEM) и удерживает его до того момента, когда запрос будет удовлетворён. Этот триггер сбрасывается за 62 нс до момента завершения соответствующего цикла памяти. Одновременно со сбросом триггера запроса взводится триггер готовности D39-2, вырабатывающий сигнал MRDY интерфейсной части модуля и управляющий выходным буферным усилителем данных. В интерфейсной части из сигнала готовности памяти MRDY формируется сигнал готовности RDY, подаваемый на системную магистраль. Триггер готовности сбрасывается, когда сигнал разрешения обмена данными по системной магистрали TE становится неактивным, т.е. по завершению цикла обмена.

3.3.7. Адресный мультиплексор модуля выполнен на микросхемах D41, D42 и D48-3, D48-4, D44-4. Две первые имеют выход с тремя состояниями, который активируется только при выполнении циклов обмена с системной магистралью. Остальные микросхемы необходимы только в том случае, если в модуль установлены микросхемы динамической памяти с информационной ёмкостью более 64 К бит. Они мультиплексируют 9-й разряд адреса. На вход этого разряда мультиплексора поступает информация с регистра выбора подбанка памяти.

3.3.8. Узел регенерации вырабатывает адреса памяти при выполнении регенерации содержимого памяти. Он состоит из 8-ми разрядного счётчика D49 и выходного буферного регистра D51 с тремя состояниями на выходе. На время выполнения цикла регенерации информация защёлкивается в регистре и выдаётся на линии адреса микросхем памяти.

3.3.9. Регистр выбора подбанка памяти выполнен на микросхеме D12. Он служит для увеличения объёма рабочей памяти свыше 128 К байт за счёт введения в пределах этого адресного пространства ещё 4-х подбанков. Адрес регистра подбанка памяти — 39Н. Информация из этого регистра может быть прочитана по тому же адресу. В седьмом бите при этом будет передаваться информация о состоянии бита ошибки по паритету. Данные во внутреннюю магистраль передаются через буферный формирователь D13 с тремя состояниями на выходе.

3.3.10. Поскольку цикл обращения к памяти имеет фиксированную длительность, то при выполнении операций чтения данные на выходе микросхем памяти будут появляться лишь на короткий промежуток времени. Регистр D11 позволяет запомнить считанные данные и сохранить их на шине данных неограниченное время. На время действия сигнала MRDY выходы этого регистра переводятся в третье состояние, освобождая шину данных для приёма информации из памяти. По окончании действия сигнала MRDY (цикл чтения окончен) считанная информация защёлкивается в регистре и выдаётся на шину данных.

3.3.11. ОЗУ модуля имеет схему контроля правильности записанной информации. Каждый записываемый байт сопровождается специальным битом, хранимым в отдельном разряде ОЗУ. Поэтому разрядность ОЗУ равна девяти. При считывании информации производится контроль её правильности с использованием бита чётности. Если обнаруживается ошибка, то взводится соответствующий триггер в схеме контроля паритета (чётности). Эта схема состоит из специализированной ИС D4 (КП531ИП5), логики D3.1, D5.1, D5.4 и D10.2 и триггера ошибки паритета D14-2. Состояние последнего через формирователь с тремя состояниями на выходе D13-3 может быть передано во внутреннюю магистраль и проанализировано процессором. Адрес чтения такой же как и адрес регистра выбора подбанка памяти — 39Н. Информация передаётся в бите D7 считываемого байта. Логическая единица в этом бите указывает на то, что была обнаружена ошибка. Сброс триггера производится при выполнении записи в регистр выбора подбанка.

3.3.12. По сравнению с разработанным ранее модулем *RTV*070.87 модуль *RTV*001.89 допускает увеличение объёма памяти до 512 К байт. Поскольку адресация такого большого объёма только средствами, содержащимися в модуле *RTV*070.87 невозможна, то в новый модуль введён дополнительный регистр выбора подбанка памяти. В программном отношении эти модули снизу вверх совместимы. Т.е., программы, написанные для работы с модулем *RTV*070.87, будут работать и с модулем *RTV*001.89, но не всегда наоборот.

3.4. Интерфейсная часть модуля

3.4.1. Интерфейсная часть модуля отвечает за взаимодействие с системной магистралью ПЭВМ. Она состоит из селектора адресов устройств ввода-вывода, селектора адресов памяти и схемы синхронизации обмена. Кроме того, она содержит буферный двунаправленный формирователь, через который осуществляется обмен между шинами данных системной и внутренней магистралей. Он выполнен на микросхеме КР580ВА86 (D1). В состав интерфейсной части входит также ПЗУ, в котором обычно хранится ядро операционной системы и некоторые наиболее часто употребляемые программы. Упрощённая схема узла приведена на рис. 3.5.

3.4.2. Селектор адресов ввода-вывода выделяет область рабочих регистров модуля и вырабатывает необходимые сигналы управления для остальных его узлов. Селектор выполнен на ПЗУ К556РТ4 (D7). Он выделяет адреса в диапазоне от 20Н до 39Н. При обращении по любому из этих адресов на выходе 9 микросхемы D7 устанавливается низкий уровень (активен сигнал IDS), и через элементы D16-3, D16.2, D2.4 выдаётся сигнал на включение буферного формирователя данных D1 и на генерацию в системную магистраль сигнала готовности READY посредством элементов D16.3, D6.4 и D40.3. На выходе 10 D7 низкий уровень устанавливается при обращении к группе адресов 20–2FН, относящихся к селектору адресов памяти. Аналогично, на выходе 11 ПЗУ выделяется группа адресов 30–37Н, относящаяся к БИС КНГМД. На выходе 12 низкий уровень возникает при обращении к дополнительным регистрам модуля. Логика D9, D15 и D3 служит для окончательной селекции и генерации управляющих сигналов и стробов, поскольку младший разряд адреса на ПЗУ не поступает.

3.4.3. При обращении к адресу 37Н сигнал IDS и, соответственно, сигнал готовности READY вырабатываются только в том случае, если хотя бы один из сигналов: DRQ либо INTRQ, поступающих на вход ПЗУ, установлен высоким уровнем. Таким способом достигается автосинхронизация при обмене данными с БИС КНГМД при чтении или записи сектора. По своим функциям адрес 33Н аналогичен адресу 37Н, но автосинхронизация не производится.

3.4.4. Селектор адресов памяти выполнен на основе БИС двухвходового ОЗУ D8 (КР1802ИР1). Это ОЗУ имеет организацию 16×4 бит. Канал А этой БИС подключён к внутренней шине данных (младшие биты) модуля. 16 ячеек этого ОЗУ по каналу А адресуются как регистры ввода-вывода. Информация, используемая затем в канале В, заносится в ОЗУ через канал А.

В качестве адресов канала В используются 4 старшие разряда адресной шины системной магистрали. Этот канал работает только в режиме считывания. Низкий уровень на выходных линиях канала В позиционно управляет выборкой одного из двух банков ПЗУ или ОЗУ. Естественно, ситуация при которой более одного выхода находятся в низком уровне является запрещённой, так как при этом возникнут столкновения на шине данных. При обращении к ПЗУ сигнал готовности формируется через те же элементы, как и в случае с группой внешних устройств без задержек. При обращении к ОЗУ сигнал готовности формируется элементом D40-3 только после выполнения соответствующего цикла памяти.

3.4.5. При включении питания содержимое ОЗУ управления памятью неопределено D8, поэтому оно может быть включено в работу только после занесения в него соответствующей информации. Обычно, эта операция осуществляется программой инициализации модуля. Блокировка работы селектора адресов памяти выполняется соответствующим триггером D14.1. Он сбрасывается при получении модулем сигнала RESET с системной магистрали и его выходной сигнал MEMON становится неактивным, блокируя работу селектора. Активация триггера происходит при выполнении операции записи в дополнительный регистр управления диском.

3.4.6. Модуль имеет 3 розетки для установки микросхем ПЗУ. Общая ёмкость ПЗУ модуля определяется типом применённых микросхем и их количеством и может варьироваться в пределах от 8-ми до 96 К байт. Селектор адресов модуля позволяет работать с двумя банками ПЗУ. Минимальный размер банка составляет 16 К байт, но дальнейшая селекция до 8 К байт проводится только в пределах одного банка. Тип применяемых микросхем задаётся с помощью перемычек П6 – П11 одновременно для всех розеток модуля. На рис. 3.5 показано их расположение для ПЗУ различных типов.

4. Меры предосторожности при работе с модулем контроллера НГМД

4.1. Модуль контроллера НГМД представляет собой сложное электронное устройство, в котором использованы интегральные микросхемы, изготовленные по МОП-технологии. Поэтому при транспортировке, установке в системный блок ПЭВМ, эксплуатации и ремонте модуля следует обеспечивать необходимые условия, исключающие воздействие на него статического электричества.

4.2. Транспортировка модуля должна производиться в специальной упаковке, защищающей его элементы от механических и электрических воздействий. Контакты разъёма X1, предназначенного для подключения модуля к системной магистрали, должны быть закорочены транспортной перемычкой-заглушкой.

4.3. К эксплуатации модуля допускаются лица, изучившие настоящее описание. Регулировка и ремонт модуля производится лицами, прошедшими специальную подготовку на заводе-изготовителе.

4.4. Все монтажные и ремонтные работы: установка модуля в системный блок ПЭВМ, подключение механизмов НГМД, замена вышедших из строя микросхем, установка перемычек и микросхем ПЗУ, производятся только при полном отсутствии питающих напряжений.

4.5. При эксплуатации, ремонте и транспортировке следует не допускать механических повреждений модуля.

4.6. Следует оберегать контакты разъёмов, особенно розеток (X3 – X6) для установки БИС КНГМД и ПЗУ, от попадания на них пыли и грязи, что может привести к снижению надёжности работы модуля. При очистке от загрязнений использовать растворители, не повреждающие материал платы и не смывающие маркировочные надписи с деталей, например, этиловый спирт.

4.7. При эксплуатации, транспортировке и хранении недопустимо прямое попадание воды на детали модуля. В случае, если это произошло, следует удалить воду и просушить модуль перед включением в работу в течении 1–2 часов до полного высыхания.

5. Проверка модуля

5.1. Изготовителем модуль контроллера поставляется настроенным с помощью перемычек на работу со 133 мм механизмами НГМД с двойной плотностью записи на диск, с установленной микросхемой D52 (К573РФ4, К573РФ6 или I2764) в розетке X6 с "зашитой" в неё программой ядра операционной системы *RTV*CP/M 20.

5.2. Проверка работоспособности модуля в условиях потребителя производится путём оценки реакции ПЭВМ и самого модуля КНГМД на команды, подаваемые с клавиатуры.

5.2.1. При включении питания ПЭВМ во время отработки программы "холодного старта" на экране монитора должно появиться сообщение, загружаемое из ПЗУ модуля процессора. Если при этом машина "зависает", необходимо проверить правильность установки микросхем резидентного ПЗУ на модуле процессора и его селектора адреса. Эти ПЗУ должны позволять работать с модулем КНГМД *RTV*001.89 (BOOT7 или DDT3, CONOUT3 и селектор адреса МА). Проверить надёжность их установки в розетках и правильность установки перемычек на плате модуля процессора. Если указанные действия не приведут к восстановлению работоспособности ПЭВМ, следует обратиться к полной проверке ПЭВМ.

5.2.1. При выборе варианта дисковой загрузки программа ядра операционной системы, "зашитая" в ПЗУ модуля КНМД, производит определение объёма и тестирование памяти, установленной на плате КНГМД, и выводит сообщение на экран монитора; ставит промпт о загрузке операционной системы или выдаёт сообщение об ошибке. Если этого не происходит, следует убедиться в отсутствии механических повреждений на плате модуля, проверить правильность установки перемычек в соответствии с рис. 2.1 настоящего описания, надёжность установки микросхемы ПЗУ в розетку X6. Если указанные действия не приведут к восстановлению работоспособности модуля, его следует отправить для ремонта изготовителю.

5.3. Более полное тестирование модуля может быть произведено специальной тестовой программой, которая загружается в ПЭВМ либо с диска (если это возможно), либо с магнитофонной ленты. Эта программа производит диагностику модуля КНГМД с точностью до узла. Для работы с программой теста необходимо пользоваться её описанием.

5.4. При групповых поставках возможна комплектация ПЭВМ дополнительной платой ПЗУ с "зашитой" тестовой программой.

5.5. При передаче технической документации в состав комплекта может входить описание стенда по наладке и проверке модуля котроллера НГМД.

ПРИЛОЖЕНИЕ 1

ПРИЛОЖЕНИЕ 2. Рекомендации по монтажу модуля КНГМД

Монтаж модуля контроллера НГМД можно начинать после изготовления печатной платы по фотошаблону 1893. Изготовленная плата не должна иметь разрывов проводников и коротких замыканий проводников между собой и на шины питания. Перед запайкой деталей необходимо установить перемычки, соединив одноимённые контакты, маркированные на плате цифрами 1 и 1.....8, проводником (см. рис. 2.1).

Подобрать комплектующие изделия в соответствии с перечнем элементов, приведённым в разделе 6 настоящего описания. Микросхему ПЗУ (D7) запрограммировать по таблице, приведённой в приложении 1 (карта "прошивки" FDCSA1.) Установку микросхем производить в соответствии с монтажной схемой, приведённой на рис. Пр2.1. Желательно соблюдать следующий порядок установки комплектующих изделий:

— сначала запаять резисторы, транзисторы, резисторные сборки, конденсаторы и микросхемы, за исключением микросхем памяти D17–D34, после чего следует тщательно отмыть плату модуля от остатков флюса.

— Запаять разъёмы X1, X2 и розетки X4–X6 для установки микросхем ПЗУ D52–D54 и БИС КНГМД (D64). Отмыть места пайки, избегая попадания промывочной жидкости в розетки, так как это приводит к значительному снижению качества контактов при установке микросхем.

— запаять микросхемы памяти, соблюдая меры предосторожности от воздействия статического электричества; удалить остатки флюса.

— в розетку X6 установить микросхему ППЗУ (К573РФ4 (РФ6) или их зарубежный аналог I2764 с запрограммированным в неё ядром операционной системы и имеющей карту "прошивки" *RTV*CP/M 20.

Ещё раз проверить установку комплектующих изделий согласно рис. Пр2.1, убедиться внешним осмотром в отсутствии коротких замыканий на плате и провести наладку модуля.

Дополнительная информация для пользователей ОС "ИРИША"

Версия BIOS – 20 для модуля КНГМД на МС К1818ВГ93.

Версия операционной системы CP/M для ПЭВМ "ИРИША" номер версии BIOS – 20 предназначена для программной поддержки модуля контроллера накопителей на гибких дисках *RTV*001.89. Программа размещена в МС ПЗУ типа К573РФ4 (или I2764). Программа размещена в розетку на плате контроллера, которая устанавливается согласно техническому описанию модуля.

Версия 20 программно совместима с предыдущими версиями BIOS. Формат файлов и алгоритм работы с накопителями на гибких магнитных дисках, расположение и назначение стартовых конфигурационных перемычек полностью соответствует описанию BIOS версии 10. Более подробная информация приводится в дополнительном материале по версии 10.

Для программного изменения конфигурации системы можно использовать программу CONFIG версия 10. Форматирование дисков выполняется с помощью программы FORMAT версия 20. Программы форматирования ранних версий не будут работать с модулем *RTV*001.89.

Операционная система версии 20 не будет работать при установке её в модуль КНГМД *RTV*071.86.

Основное отличие версии 20 от предыдущих заключается в способности программно поддерживать расширенную память модуля *RTV*001.89. При этом объём квазидиска в зависимости от типа установленных микросхем может изменяться от 128 до 512 Кбайт. При старте операционная система автоматически определяет объём имеющейся памяти и соответственно конфигурирует системные параметры квазидиска.

Старт операционной системы

Если в стартовом меню ПЭВМ выбирается диск, то управление передаётся программе ОС. Прежде всего программа определяет, является ли данный старт первым после включения ПЭВМ в работу. Для этого программа тестирует 5 специфических байт, расположенных в зоне входного вектора BIOS. После первого включения ПЭВМ в этих ячейках находится случайная информация, что является признаком "холодного" старта. Если же операционная система была ранее загружена, и начальный старт был вызван нажатием клавиши сброса без выключения питания, то по этим адресам находится код 0С3Н.

Поскольку версия 20 автоматически распознаёт ситуации "холодного" старта и рестарта, то, в отличие от предыдущих версий, никакого запроса на очистку квазидиска не выводится. Если система зарегистрировала необходимость холодного старта, то проводится начальный тест памяти, определяются исправные банки памяти, которые затем объединяются в квазидиск. Тип установленных МС памяти значения не имеет. Более того, если отдельные участки памяти неисправны, то соответствующие сегменты ОЗУ размером 16 Кбайт будут исключены из общего распределения памяти и не включаются в квазидиск.

Во время тестирования памяти ОС выводит на экран дисплея символ II на каждый тестируемый трек.

Результаты тестирования и объём квазидиска, зафиксированный ОС, выводятся на экран в сообщении:

RAM – disk tracks:XX

где XX – число исправных сегментов (треков) размером 16 Кбайт каждый, включённых в пространство квазидиска. Объём квазидиска в килобайтах вычисляется путём умножения числа зафиксированных системой треков на 16.

В действительности число исправных сегментов памяти равно XX+1, однако 1 сегмент ОС резервирует для системных нужд (в нём размещается буфер сектора НГМД и т.д.) и не включает его в состав квазидиска.

Иногда после начального теста может появляться сообщение об ошибке:

Fatal error

Это сообщение обусловлено одной из двух причин:

а). число исправных сегментов меньше 2-х.

б). среди исправных сегментов нет ни одного, подходящего для использования его в системных целях (в силу особенностей физического распределения памяти только некоторые треки пригодны для системного использования).

В любом случае дальнейшая работа операционной системы невозможна, и после появления этой ошибки ПЭВМ останавливается. Если такая ошибка возникла, попробуйте выключить ПЭВМ и, включив её снова, ещё раз запустить ОС. При дальнейшем появлении такой ошибки замените неисправные микросхемы памяти или обратитесь к поставщику ПЭВМ для устранения неисправности.

В ситуации повторного старта без выключения питания тест памяти и реконфигурация квазидиска не производится. Модуль BIOS не перегружается из ПЗУ, поэтому ОС считает, что действительна конфигурация, установленная ранее. При этом все изменения конфигурации, сделанные с помощью программы CONFIG (изменение принтера, форматы НГМД и т.д.), в отличие от предыдущих версий сохраняются.

Естественно, что при этом информация, записанная в квазидиске также сохраняется.

Попытка перезапустить ОС после сброса с клавиатуры при условии, что тест памяти после холодного старта диагностировал фатальную ошибку, приводит к непредсказуемым результатам.

Новые сообщения об ошибках

Операционная система версии BIOS – 20 поддерживает аппаратно реализованный в модуле *RTV*001.89 механизм контроля исправности памяти по дополнительному биту чётности. Это обеспечивает пользователю дополнительную защиту информации при работе с квазидиском, а также при чтении с НГМД.

В случае возникновения такой ошибки операционная система выводит сообщение:

Parity error

Флаг ошибки передаётся также модулю BDOS, который сообщает далее на каком диске произошёл сбой.

Контроль чётности не даёт абсолютной гарантии правильности считанной информации, однако существенно уменьшает вероятность искажений. Тем не менее, при установке микросхем памяти обязательно необходимо проверить их исправность с помощью тестовой программы, для чего обратитесь к поставщику ПЭВМ.