Агат/ЯБ3.089.026 ТО Ячейка процессора, памяти и интерфейса

| Данный материал защищён авторскими правами!

Использование материала заявлено как добросовестное, исключительно для образовательных некоммерческих целей. |

1. Введение

Настоящее техническое описание предназначено для изучения состава, назначения и работы ячейки процессора памяти и интерфейса ЯБ3.089.026.

При изучении данного ТО следует дополнительно руководствоваться следующими документами:

- ФЗ.038.650-01 Э3 - Блок системный. Схема электрическая принципиальная.

- ФЗ.038.648 ТО - Блок клавиатуры. Техническое описание.

- ФЗ.032.002 ТО5 - Машина вычислительная электронная персональная "АГАТ" исполнение 9. Описание аппаратных средств

2. Назначение

Ячейка процессора памяти и интерфейса (далее для краткости просто ячейка), является основным функциональным узлом персональной электронной вычислительной машины "АГАТ" исполнение 9, практически представляет собой двухрежимную дополненную вычислительную машину с открытой архитектурой и реализует следующие функции:

- программную обработку цифровой информации;

- хранение информации и программ в запоминающем устройстве;

- обеспечение управления режимами хранения информации;

- обеспечение вывода информации на цветное и черно-белое видеоконтрольное устройство;

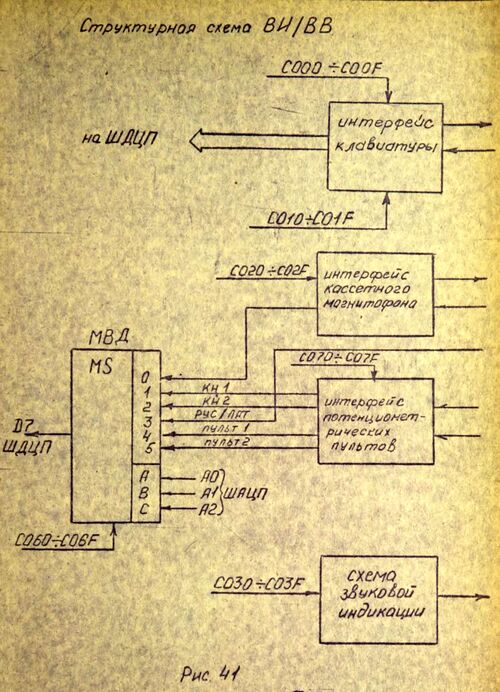

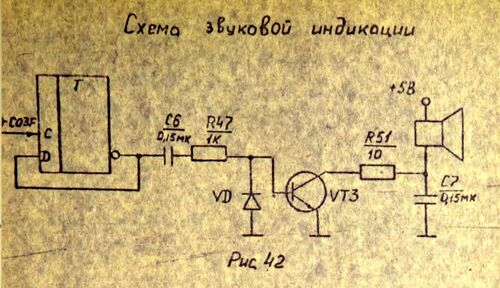

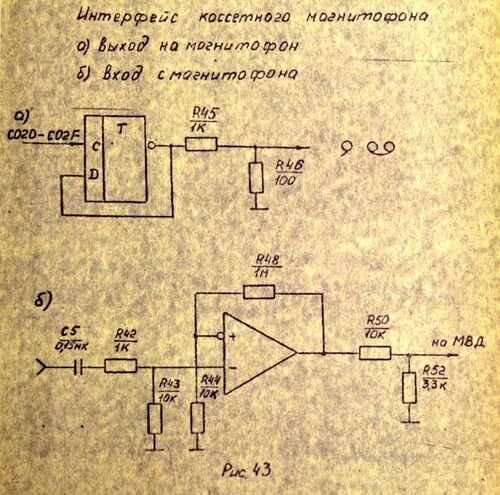

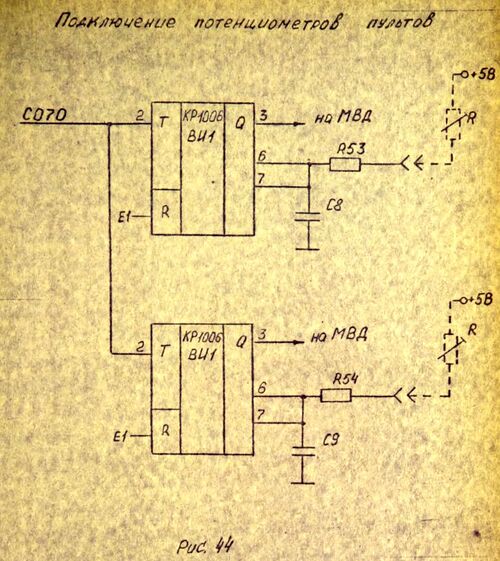

- обеспечение ввода/вывода информации на магнитофон, звуковой индикации, ввода данных с клавиатуры и с потенциометрических пультов.

На ячейке конструктивно реализован в виде 6-ти 60-контактных разъемов внутренний интерфейс ПЭВМ, обеспечивающий широкие возможности для расширения функций ПЭВМ за счет установки в эти разъемы дополнительных модулей и ячеек.

Ячейка предназначена для эксплуатации в нормальных климатических условиях при температуре (25±10)°С, относительной влажности (60±15)%, атмосферном давлении 86-106 кПа (653-806 мм.рт.ст.).

3. Технические данные

3.1. Габаритные размеры ячейки 330х270х25 мм. Масса 700 г.

3.2. Максимальный ток потребления ячейки по цепи +5В — 3 А, по цепям +12 и -12В — по 0,005 А.

3.3. Ячейка нормально функционирует при колебаниях питающих напряжений в пределах 5% по цепи +5В и 10% по цепям +12В и -12В.

3.4. Основные характеристики:

3.4.1. Центральный процессор СМ630Р (аналог МСS6502)

3.4.2. Тактовая частота — 1.021 МГц.

3.4.3. Адресуемая память — 64 Кбайт (16 разрядов адреса).

3.4.4. Обрабатываемое слово данных — 1 байт (8 разрядов).

3.4.5. Емкость ПЗУ — 2 Кбайта (с возможностью расширения до 12).

3.4.6. Емкость оперативной памяти — 128 Кбайт.

3.4.7. Время обращения к памяти — не более 400 нс.

3.4.8. Время регенерации — не более 2 мс.

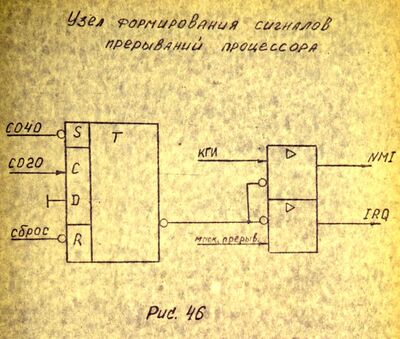

3.4.9. Число прерываний — 2;

3.4.10. Прямой доступ к памяти — имеется;

3.4.11. Режим работы дисплейного контроллера — режим "Агат" и режим "Apple".

Вывод информации на экран ВКУ в режиме "Агат":

- графический монохромный высокого разрешения 256х256 точек;

- графический монохромный с двойной плотностью 512х256 точек;

- графический цветной 256х256, 4 цвета;

- графический цветной среднего разрешения 128х128 блоков, 8 цветов;

- текстовый 32 строки, по 32 цветных символа (8 цветов) или 32 строки по 64 символа (монохромное изображение).

Вывод информации в режиме "Apple":

- графический 280х192, 6 цветов;

- алфавитно-цифровой 24 строки по 40 цветных символов, 8 цветов,

- комбинированный графика 280х160 точек и 4 строки текста.

3.4.12. Цветной графический режим 256х256, монохромные графические режимы и все текстовые режимы реализованы с 4-я цветными палитрами;

3.4.13. Подключение видеоконтрольного устройства:

- цветного — через RGB разъем

- черно-белого — через видео-выход.

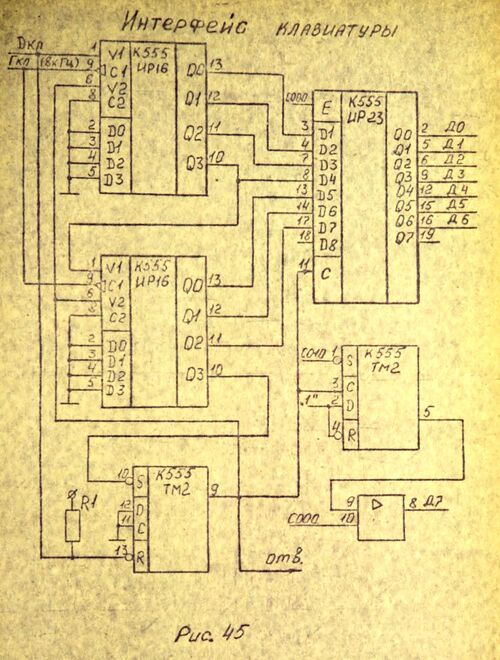

3.4.14. Обмен с клавиатурой последовательный, код обмена КОИ-8 по ГОСТ 13052-74.

3.4.15. Обмен с накопителем на магнитной ленте — частотно-модулированный, скорость обмена 500 бод.

4. Устройство и работа ячейки

4.1. Структурная организация ячейки

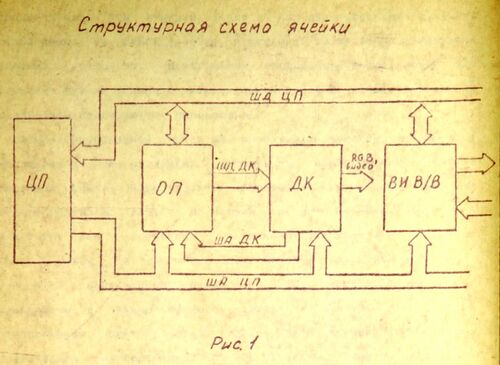

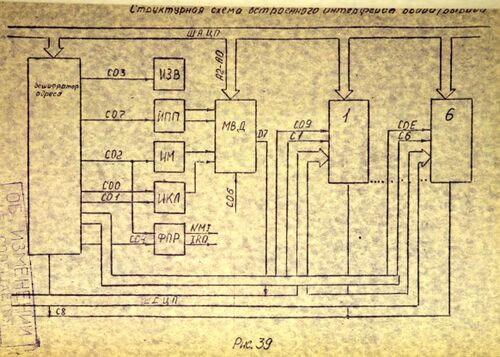

Ячейка процессора, памяти и интерфейса сосредотачивает в себе все функциональные узлы, необходимые для реализации минимальной конфигурации персональной ЭВМ с "открытой архитектурой". Практически это одноплатная микро-ЭВМ, имеющая соответствующие средства для расширения функциональных возможностей и содержащаяя лишь те узлы, которые являются обязательными и жизненно необходимыми для обеспечения работы персональной ЭВМ. Общая структурная схема ячейки, представленная на рис.1, объединяет следующие основные функциональные узлы:

- центрального процессора (ЦП);

- оперативной памяти (ОП);

- дисплейного контроллера (ДК);

- интерфейса ввода/вывода (ИВ/В).

Узел центрального процессора включает непосредственно микропроцессор, который управляет работой всех узлов ПЭВМ, обеспечивает чтение информации из памяти, ее обработку, запись результатов обратно в память. В узел ЦП дополнительно входят схема синхронизации и схема управления режимами работы ПЭВМ. Схема синхронизации формирует все тактовые сигналы, необходимые для работы центрального процессора, памяти, схем управления. Схема управления обеспечивает возможность работы ПЭВМ как в режиме "Агат", так и в режиме "Apple".

Узел оперативной памяти объединяет схемы управления доступом к памяти и оперативное запоминающее устройство емкостью 128К байт.

Дисплейный контроллер обеспечивает считывание информации из оперативной памяти, преобразует ее в соответствии с требуемым режимом отображения, формирует изображение на экране.

Интерфейс ввода/вывода непосредственно выполняет функции ввода/вывода. Эти функции делятся на две категории: функции, выполняемые на самой ячейке, и функции, выполняемые с модулями внешних устройств. Центральный процессор поддерживает эти функции путем обмена с интерфейсом через 4096 ячеек, выделенных в адресном пространстве процессора.

Обмен информацией между ЦП, оперативной памятью, интерфейсом ввода/вывода и модулями расширения обеспечивается единой системой шин - магистралью, образующей внутренний системный интерфейс ПЭВМ "Агат". В каждой операции обмена информацией участвуют два устройства - активное (задатчик) и пассивное (исполнитель). К активным устройствам, инициирующим обмен, относятся центральный процессор или внешние устройства, работающие в режиме прямого доступа к памяти. На интерфейс одновременно может работать только одно активное устройство. Оперативная и постоянная память всегда являются пассивными устройствами.

Функционально сигналы внутреннего интерфейса разделяются на три типа шин: шину адреса (16 линий), шину данных (8 линий) и шину управления и синхронизации (16 линий). По шине данных ЦП (ШД ЦП), обслуживающей 8 двунаправленных линий с тремя состояниями, происходит байтовый обмен данных между ЦП и памятью, а также прием и передача данных через интерфейс ввода/вывода. Шина адреса ЦП (ША ЦП) обеспечивает передачу от ЦП к другим устройствам 16-разрядного кода адреса. При организации прямого доступа к памяти (ПДП) адрес задается контроллером внешних устройств, установленных в разъемы ячейки. В связи с этим ША ЦП выполнена двунаправленной с тремя состояниями. Шина управления и синхронизации объединяет сигналы 14 МГц, 7 МГц, 2 МГц, ФО, Ф1, R/W, ПМ, НМI, IRQ, RES, RDY, БЛОЗУб БЛПЗУ, БЛВ/В, I/OSTB.

Линии шины управления и синхронизации осуществляют передачу сигналов для управления всей системой и синхронизацию всех передач данных. Конструктивно внутренний системный интерфейс реализован в виде 6 60-контактных разъемов (X1-X6), пронумерованных от края платы к ее середине.

Оперативная память связана с ДК, так же как и с ЦП: шиной адреса (ША ДК) и шиной данных (ШД ДК). По шине адреса от дисплейного контроллера к ОП передается 16-разрядный код адреса, сформированный в ДК, по ШД ДК из ОП в дисплейный контроллер поступают 16-разрядные коды данных, которые после соответствующей обработки выводятся на экран ВКУ. Следует отметить, что ДК только счтьывает информацию из оперативной памяти, и поэтому ША ДК и ШД ДК являются однонаправленными. Таким образом, к информации, хранящейся в ОП, имеют доступ два пользователя: центральный процессор и дисплейный контроллер. При этом каждый из них предъявляет исключительные права на приоритет доступа к ОП, так как для нормальной работы ПЭВМ в ней необходимо непрерывно поддерживать одновременное и независимое протекание двух процессов: функционирование центрального процессора, работающего по программе, и отображение информации на экране дисплейным контроллером. Оба процесса требуют непрерывной подкачки информации из оперативной памяти, в противном случае происходит или замедление работы центрального процессора, или нарушение временных процессов формирования изображения на экране. Чтобы обеспечить оба процесса непрерывным потоком информации, оперативная память должна гарантировать обслуживание двух пользователей: и ЦП, и ДК.

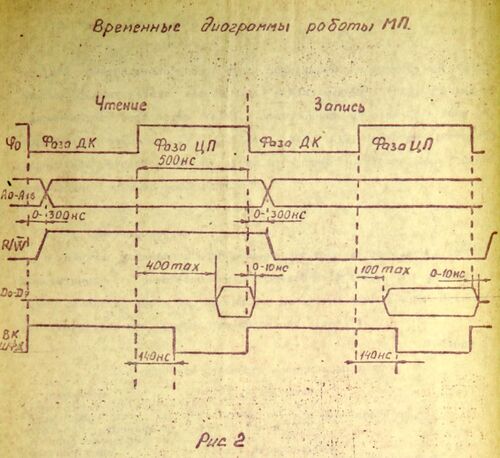

Существует несколько способов организации работы ОП на двух пользователей. В ПЭВМ "Агат" применен один из самых простых способов, известный как способ разделения фаз основной тактовой частоты. В основе способа лежит отличительная особенность используемого микропроцессора производить обмен информацией по шине данных только в течение действия высокого уровня тактовых импульсов Ф0 (1.021 МГц), синхронизирующих работу центрального процессора. При низком же уровне импульсов Ф0 микропроцессор осуществляет внутренние переключения и не пользуется шиной данных, а следовательно и оперативной памятью. Благодаря этому возможно разделение периода импульсов основной тактовой частоты микропроцессора Ф0 на две равные части (фазы): фазу процессора и фазу ДК (рис.2). ЦП получает доступ к оперативной памяти в течение действия высокого уровня импульсов Ф0 (фаза процессора), а на время действия отрицательного уровня импульсов Ф0 к ОП получает доступ дисплейный контроллер (фаза ДК). Такой способ исключает возникновение конфликтных ситуаций и позволяет использовать ЦП с максимально возможным быстродействием без нарушения процесса формирования изображения.

4.2. Узел центрального процессора

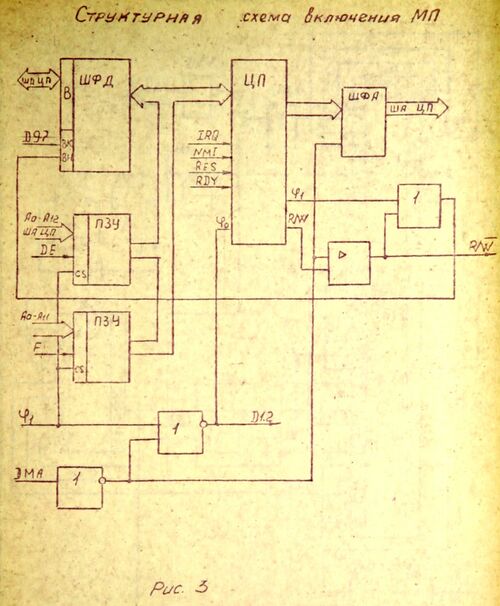

Узел центрального процессора объединяет микропроцессор (Д15), линии формирователи адреса (Д17 и Д18) и данных (Д4), постоянное запоминающее устройство (ПЗУ), построенное на элементах Д5 и Д6, логические элементы Д1, Д7, Д12, Д13, Д19, обеспечивающие его нормальное функционирование (рис.3), схему синхронизации и схему управления режимами работы ПЭВМ.

4.2.1. Микропроцессор

В ячейке устанавливается восьмиразрядный микропроцессор СМ630Р, совместимый с семейством микропроцессоров МСS6502Х, используемых в ПЭВМ семейства Apple II, Правец 8 и некоторых других ПЭВМ. Основные характеристики микропроцессора приведены в табл.1.

Таблица 1. Основные параметры микропроцессора Параметр Значение прерывания 2 — маскируемое и немаскируемое начальная установка 1 — по линии RESET адресное пространство 64К адресов (65536) адресная шина 16 бит, параллельная информационная шина 8 бит, параллельная двунаправленная количество команд 56 режимов адресации 13 напряжение питания + 5 В рассеиваемая мощность 250 мВт тактовая частота 1.021 МГц

Для синхронизации работы микропроцессора (МП) используется сигнал основной тактовой частоты Ф0, подаваемой на вход 3. Информационная шина (шина данных) используется микропроцессором только в течение периода времени, когда сигнал Ф0 имеет высокий уровень.

При низком уровне Ф0 микропроцессор не использует информационную шину, так как выполняет внутренние операции, одновременно осуществляя переустановку кода на адресной шине (рис.2).

Установка МП в начальное состояние при первом или повторном запуске ПЭВМ осуществляется сигналом RES (Х1-Х6.А21). По спаду уровня этого сигнала (вход Д15.40) микропроцессор останавливается. При установлении высокого уровня на линии RES микропроцессор начинает выполнять микропрограмму повторного запуска. Для выполнения микропрограммы запуска сигнал на линии RES должен находиться на низком уровне не менее 8 мкс. Система автостарта, подключенная к кнопке "СБР" на клавиатуре удерживает RES=0 после включения питания на время, достаточное для стабилизации всех входных напряжений и синхросигналов и выполнения микропрограммы запуска.

Сигнал RDY (готовность) позволяет приостанавливать работу микропроцессора. Установка сигнала RDY в низкий уровень останавливает микропроцессор в момент действия Ф1 (Ф0=0), при этом адресная шина сохраняет адрес текущей ячейки, содержимого которой выбирается.

Сигналы IRQ и NMI являются соответственно сигналами запроса прерывания и немаскируемого прерывания. При низком уровне сигнала IRQ и программном разрешении прерываний микропроцессор по окончании выполнения текущей команды переходит к подпрограмме обработки маскируемого прерывания. По спаду сигнала NMI независимо от внутреннего состояния микропроцессора начинается окончание текущей команды цикл прерывания, передавая управление соответствующей подпрограмме обработки.

Все линии управления RDY, DMA, RES, IRQ, NMI, идущие к микропроцессору, при отсутствии активных сигналов поддерживаются на высоком уровне с помощью резисторов 3,3 кОм, подключенных к цепи +5 В.

Сигнал R/W (выход 34) указывает на режим работы МП с памятью (чтение/запись). В режиме чтения данных из памяти на этой линии МП поддерживает высокий уровень, на время записи уровень становится низким.

4.2.2. Адресное пространство ПЭВМ

Общее число адресов, доступных для прямого обращения микропроцессора, определяется числом линий шины адреса и составляет 64К (65384) адресов (от 0000 до FFFF в шестрнадцатеричной системе счисления). Особенности функционирования данного типа микропроцессора, а также соображения по обеспечению совместимости предопредеделили следующее распределение адресного пространства МП (рис.6):

Адресное поле МП

+-------------------------------+

0000 | |

| |

| |

| |

| ОП |

| (48 Кбайт) |

| |

BFFF | |

+---------------+---------------+

C000 | |

| В/В |

| (2 Кбайт) |

C7FF |-------------------------------+

C800 | |

| ПЗУ В/В |

| (2 Кбайт) |

CFFF |-------------------------------+

D000 | |

| |

| ПЗУ |

| (12 Кбайт) |

FFFF | |

+-------------------------------+

Рис. 6

- адреса 0000-BFFF (48К) выделены для обращений к оперативной памяти, используемой для хранения программы и данных;

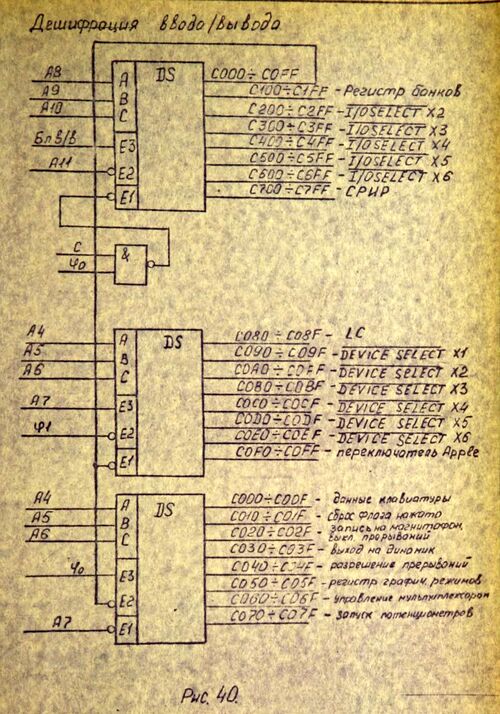

- адреса C000-C7FF (2К) выделены под интерфейс ввода/вывода. Часть из этих адресов используется непосредственно в ячейке для переключения режимов работы ЭВМ;

- адреса C800-CFFF (2К) отводятся для ПЗУ ввода/вывода, т.е. для ПЗУ, устанавливаемых на модулях расширения с возможностью доступа к ним через внутренний системный интерфейс;

- адреса D000-FFFF (12К) - область постоянной памяти, использование которой возможно как в режиме стандартного ПЗУ, так и в режиме псевдо-ПЗУ (см. 4.3.2.).

4.2.3. Шинные формирователи адреса и данных

Для увеличения нагрузочной способности линий ШД ЦП и ША ЦП пропускаются через шинные формирователи КР580ВА86 (Д4, Д17, Д18) с повышенной нагрузочной способностью (до 32 мА). С помощью логических элементов (Д13.1, Д12.1, Д1.1, Д7.1, Д19.1, Д12.2) осуществлено управление шинными формирователями. Строб включения шинного формирователя ШД ЦП (вход Д4.9) формируется при отключенном ПЗУ (ВКПЗУ=0) с задержкой на два такта 14МГц (280 нс) относительно окончания сигнала Ф0=1 (рис.2). Если ЦП обращается непосредственно к ПЗУ (ВКПЗУ=1), то шинный формирователь данных Д4 устанавливается в третье состояние.

Во время работы микропроцессора шинные формирователи адреса Д17 и Д18 включены на выдачу адреса микропроцессором. При обращении к ячейке в режиме прямого доступа к памяти к линии управления DMA (X1-X6.Б23) устанавливается нижний уровень, блокируя выдачу сигналов шины адреса, шины данных и сигнала R/W, переводом их в высокоимпедансное состояние и прерывая подачу сигнала Ф0 на микропроцессор, что вызывает его остановку (рис.3).

Непосредственно к информационным входам микропроцессора подключены выходы ПЗУ (микросхемы Д5 и Д6). В ПЗУ Д6 записана программа "Монитор", обеспечивающая старт ПЭВМ по включению питания и включающая подпрограммы поддержки базовых устройств ввода/вывода и диалога с пользователем. Чтение выходов Д6 разрешено при Ф0=1 и высоком уровне сигнала F (при ВКПЗУ=1 на адресной шине установлен один из адресов F000-FFFF). Микросхема Д5 не устанавливается и предназначена для возможных дальнейших расширений.

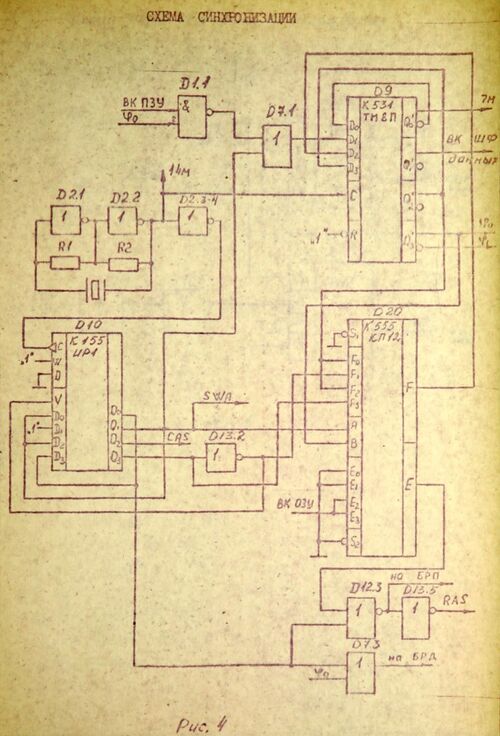

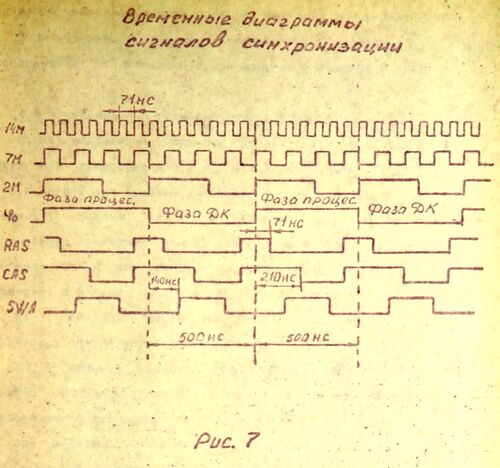

4.2.4. Схема синхронизации

Схема синхронизации (рис. 4) включает задающий генератор с тактовой частотой 14.3 МГц, собранный на кварцевом резонаторе BQ1 и схеме КH531ЛА3 (элемент Д2), формирователи сигналов синхронизации (элементы Д9, Д10, Д??) и три инвертора Д13.2–Д13.4. Временные диаграммы формируемых тактовых сигналов представлены на рис.7. Время установления сигналов синхронизации после стабилизации напряжения питания составляет несколько тактов сигнала 14 МГц.

Тактовые сигналы 14МГц, 7МГц, 2МГц, Ф0, Ф1 относятся к сигналам управления и выведены на разъемы X1-X6 ячейки для возможного использования внешними устройствами. Тактовые сигналы RAS, CAS и SWA на разъем не выводятся и используются для работы с оперативной памятью.

Сигнал 14МГц является исходным. Из него получаются все остальные сигналы синхронизации. Промежуточный сигнал синхронизации 7МГц используется в схеме генерации видеосигнала в ДК при работе ПЭВМ в режиме "Apple".

Сигнал Ф0 — сигнал синхронизации системы для фаз 0 (тактовая частота 1.021 МГц), является задающим для центрального процессора. При Ф0 равном логическому "0" (фаза ДК) разрешен доступ ДК к памяти, при высоком уровне сигнала (фаза ЦП) память доступна для ЦП. Сигнал Ф1 — сигнал синхронизации системы для фазы 1 (дополнение к Ф0). Обмен ЦП и ДК с оперативной памятью предусматривают жесткую двухтактную синхронизацию неперекрывающимися импульсами Ф0 и Ф1, поэтому указанные сигналы формируются на инверсных друг другу выходах Д9.15 и Д9.14.

Сигнал RAS и CAS предназначены для обеспечения адресации ОЗУ ячейки, построенного на микросхемах динамической памяти КР565РУ5.

Сигнал SWA используется для переключения адресов, поступающих на входы микросхем памяти после их фиксации по сигналу RAS.

Дополнительные элементы комбинационной логики Д7.3, Д12.3 обеспечивают отключение ОЗУ при запрете обращения к нему ЦП.

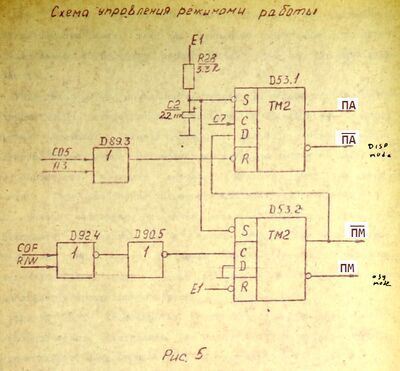

4.2.5. Управление режимами работы ПЭВМ

Примечание: В исходном документе названия сигналов ПМ и ПА перепутаны!

Схема управления режимами работы ПЭВМ (СУУР) построена на двух R-S триггерах Д53.1 и Д53.2 и комбинационной логике Д89.3, Д90.5 и Д92.4 и предназначена для обеспечения работы ПЭВМ в двух режимах: режиме "Агат" и режиме "Apple" (рис.5).

Функции управления режимами работы ПЭВМ выполняют два формируемых СУУР сигнала ПМ и ПА ПА и ПМ, причем первый сигнал управляет оперативной памятью, а второй — работой дисплейного контроллера.

- ПМ — признак машины

ПА — признак "Apple"(вывод Д53.8). Высокий уровень сигнала переводит оперативную память на работу в режиме "Apple".

- ПА — признак "Apple"

ПМ — признак машины. Высокий уровень сигнала переводит ДК в режим отображения информации ПЭВМ "Агат"; при ПА=0ПМ=0отображение информации будет осуществляться в режимах "Apple".

При включении питания ПЭВМ входы триггеров Д53.4 и Д53.10 с помощью R-C цепочки (R28 и С2) удерживаются на низком уровне на время, достаточное для стабилизации питающих напряжений, и тем самым обеспечивают начальную установку ПЭВМ в режим "Агат" (ПМ=0 и ПА=1 ПА=0 и ПМ=1).

Переключение режимов работы осуществляется с помощью адресных обращений к СУУР по адресам из области адресов ввода/вывода.

Принятые в ячейке схемотехнические решения обеспечивают переход ПЭВМ в режим "Apple" (ПМ=1, ПА=0 ПА=1, ПМ=0) без обратного выхода в режим "Агат". Эти меры предприняты для предотвращения случайного переключения в режим "Агат" программами, написанными для ПЭВМ семейства "Apple". В режиме "Apple" ПЭВМ программно совместима с персональными машинами Apple-II, "Правец". Выход ПЭВМ в режим "Apple" осуществляется в два приёма.

Сперва по операции записи по любому адресу из диапазона C0F0–C0FF в этот режим переводится работа с памятью (сигнал ПМ=1 ПА=1). Значение записываемого байта информации несущественно, так как управление регистром осуществляется только адресом.

По этой команде на тактовом входе триггера Д53.2 формируется импульс отрицательной полярности, по заднему фронту которого выход Д53.9 установится в низкий уровень. На втором этапе в режим "Apple" переводится ДК. Для этого достаточно обратиться к СУУР по одному из адресов C050–C057 или C700–C7FF с помощью операций чтения (или записи). В обоих случаях на выходе триггера Д53.5 (сигнал ПА ПМ) установится низкий уровень.

При работе памяти ПЭВМ в режиме "Агат" (ПМ=0 ПА=0) ДК в зависимости от уровня сигнала ПА ПМ может отображать информацию как в режимах "Агат", так и в режимах "Apple".

При высоком уровне сигнала ПА ПМ программно и аппаратно совместима со своими предыдущими моделями и имеет два новых режима отображения информации (высокоразрешающая монохромная графика 512×256 точек и цветная графика 256×256 точек, 4 цвета). Переключение ДК в этот режим производится операциями обращения ЦП по адресам из диапазона C700–C7FF. В этом случае на старших 8 разрядах адреса A15–A8 ША ЦП устанавливается код C7 (1100 0111), обеспечивающий формирование на тактовом входе Д53.3 импульса отрицательной полярности, по заднему фронту которого в триггер (выход Д53.5) записывается 1 (если ПМ=1 ПА=1 то запишется 0) и ДК переводится в режим "Агат".

При обращении к СУУР по одному из адресов C050–C057 триггер будет сброшен (установится ПА=0 ПМ=0) и ДК переводится в режим "Apple".

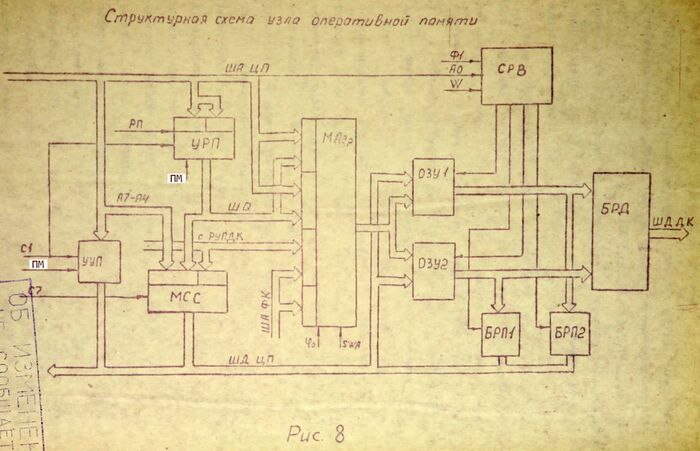

4.3. Организация оперативной памяти

По функциональным признакам в оперативной памяти (ОП) можно выделить (рис.8) устройство распределения памяти, узел управления памятью и модуль ОП, включающий непосредственно элементы памяти, мультиплексоры адреса и буферные регистры данных ЦП и ДК.

При обмене информацией с оперативной памятью микропроцессор не может прямо адресоваться ко всей памяти, так как объем оперативного запоминающего устройства (ОЗУ), установленного на ячейке (128К байт), в 2 раза превышает адресное пространство МП.

Чтобы обеспечить микропроцессору доступ ко всему объему ОЗУ, на ячейке реализована архитектура с гибким распределением памяти, по построению близкая к концепции виртуальной памяти. Это достигается введением специального устройства распределения памяти, содержащего таблицу соответствия между зонами адресного пространства МП (сегментами) и оперативной памятью, разделенной на банки. Хранение таблицы в специальных регистрах позволяет микропроцессору с ограниченным адресным пространством (64К) произвольно обращаться к любому банку ОЗУ, расширяя тем самым память, доступную ЦП до 128К байт (и выше при установке ячеек дополнительной памяти).

Узел управления памятью реализует разделение адресного пространства микропроцессора на области ОЗУ, ввода/вывода и ПЗУ (рис.4), определяя правила доступа к ОП и ПЗУ в зависимости от адреса, формируемого микропроцессором, и от сигналов блокировки памяти, формируемых внешними устройствами (например, ячейками дополнительной памяти).

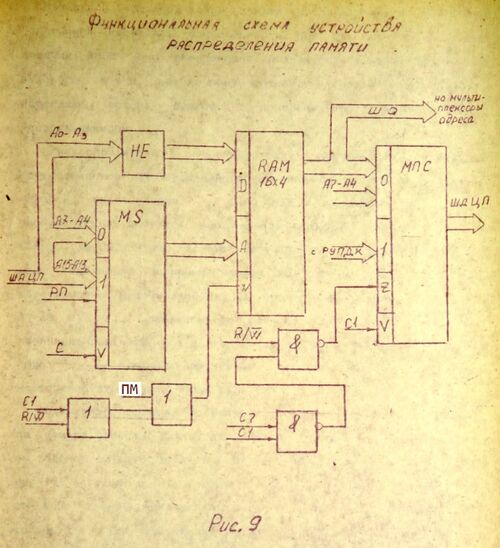

4.3.1. Распределение оперативной памяти

Устройство распределения памяти (УРП) построено на мультиплексоре К555КП11 (Д11), микросхеме статического ОЗУ 16×4 КР531РУ8 (Д21) и 4-х элементах НЕ (Д16.1–Д16.4, рис.9). Назначение УРП, как указывалось выше, заключается в расширении шины адреса до 17 разрядов с целью обеспечения доступа ЦП к любой части ОЗУ.

Такая организация памяти достигнута следующими средствами. Всё адресное пространство ЦП разбивается на восемь адресных сегментов (зон) по 8К байт адресов: адреса 0000–1FFF соответствуют нулевому сегменту, адреса 2000–3FFF — первому и т.д. ОЗУ ячейки ёмкостью 128К делится на 16 эквивалентных друг другу банков памяти по 8К байт в каждом. Непосредственно на память выведены 13 младших разрядов шины адреса (A12–A0), обеспечивающие адресацию 8К ячеек ОЗУ. Оставшиеся старшие три разряда шины адреса (A15–A13), определяющие номер адресного сегмента, через мультиплексор Д11 подключены к адресным входам статического ОЗУ (Д21), хранящего в шестнадцати 4-разрядных регистрах номера банков ОЗУ.

При обращении к оперативной памяти (любой адрес, кроме адресов из C000–CFFF) эти три разряда адреса выбирают один из первых 8 регистров статического ОЗУ, находящегося в режиме чтения. Номер выбранного регистра равен номеру сегмента адресного пространства ЦП. В результате на выходах статического ОЗУ (выводы 5, 7, 9, 11) формируется код номера банка (старшие четыре разряда адреса ОЗУ ячейки), подключаемого к текущему адресному сегменту.

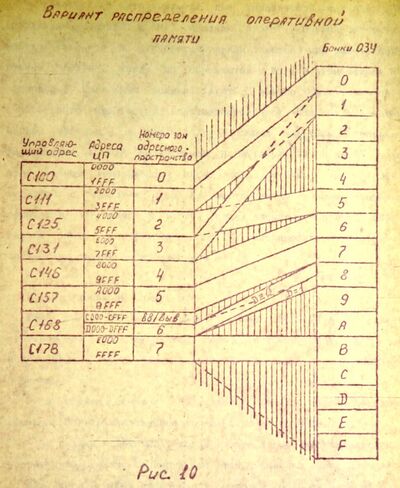

При таком способе адресации любые 8 из 16 банков ОЗУ могут быть подключены к 8 адресным сегментам ЦП по 8К байт адресов в каждом, а соответствие между их номерами задается в первых восьми регистрах статического ОЗУ. Пример варианта распределения памяти показан на рис.10.

Начальное распределение памяти устанавливается программой "Системный монитор", записанной в ПЗУ Д6, сразу по включении питания ПЭВМ. Оно обеспечивает подключение к нулевому сегменту нулевого банка, к первому сегменту первого банка и т. д. Последние восемь банков с номерами от 8 до F остаются неподключенными.

Перераспределение соответствия банков и сегментов осуществляется ЦП обращением по специальным адресам, отведённым в области ввода/вывода — C100–C1FF. Изменения в таблицу распределения вносятся выполнением операции записи по адресу C1mn, где m — номер сегмента (m=0–7), а n — номер банка (n=0–F). При выполнении операции записи по адресу C1mn происходит переключение мультиплексора Д11 на передачу кода m (разряды A4–A6 ША ЦП), определяющего регистр, в который будет записан проинвертированный код n в качестве нового содержимого. Инверсия кода n необходима вследствие наличия инверсных выходов у микросхемы статического ОЗУ КР531РУ8.

Содержимое таблицы распределения памяти может быть прочитано по тем же адресам. Для этого ЦП должен выполнить операцию чтения по адресу соответствующего сегмента — C1mX, где X обозначает любой из 16 адресов 0–F. В результате выполнения такой операции в ЦП по шине данных поступит код mn, т.е. номер банка n занимающего сегмент m.

Для считывания текущего распределения предназначен мультиплексор передачи состояний (МПС), состоящий из двух микросхем К555КП11 (Д22, Д23). В случае обращения ЦП по адресу C1mX (т.е. при выполнении операции чтения по любому из адресов C1m0–C1mF) МПС обеспечивает передачу на шину данных кода номера сегмента m (на разряды D4–D6 ШД ЦП) и содержимого регистра, указывающего код номера банка, подключенного на данный сегмент (на разряды D0–D3).

В работе УУП используются два управляющих сигнала: "РП" (разделение памяти) и "ПМ" (признак машины) "ПА" (признак "Apple"). Первый практически всегда равен 0 и становится равным 1 только при работе ПЭВМ в режиме "Apple", когда ЦП обращается к ПЗУ. В этом случае ПЗУ, содержащее программы режима "Агат", должно быть отключено, а вместо него процессору подставляется тот банк ОЗУ, в который перед переходом в режим "Apple" были загружены программы, размещаемые в ПЗУ эмулируемой ПЭВМ (Apple II, Правец). Номера этих банков записываются перед переходом в режим "Apple" в регистры с номерами E и F, соответствующие номерам адресных сегментов ПЗУ плюс 8. Второй сигнал блокирует запись в D21 при работе ПЭВМ в режиме "Apple" (блокировка осуществляется логическим сложением на элементе D7.4).

4.3.2. Управление памятью

Как было указано ранее, адреса D000–FFFF в адресном пространстве ЦП отводятся под системное ПЗУ. На ячейке использование этой части адресного пространства возможно в двух режимах:

- в режиме обычного ПЗУ, когда на эти адреса подключено реальное ПЗУ, реализованное на микросхемах D5 и D6;

- в режиме псевдо-ПЗУ, когда на эти адреса подключается часть оперативной памяти, блокируя при этом чтение из микросхем ПЗУ.

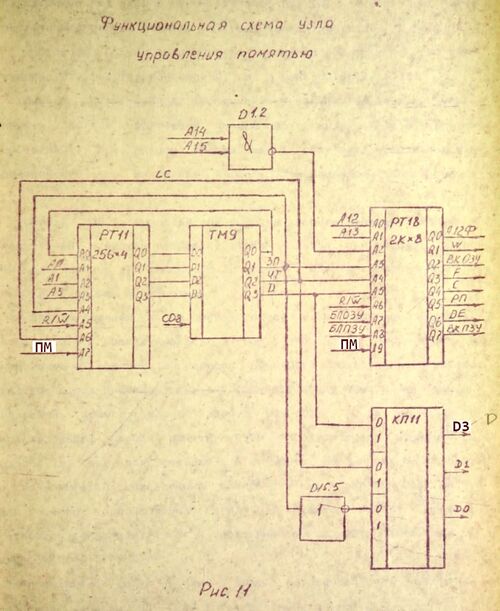

Для того, чтобы обеспечить переход области адресов ПЗУ из режима в режим, а также для обеспечения разделения адресного пространства на соответствующие зоны, на ячейке имеется специальный узел управления памятью (УУП, рис. 11), выполненный на двух микросхемах ПЗУ (D3 и D14), триггерах К555ТМ9 (D8) и элементах логики (D1.2, D24.1).

На элементах Д3 и Д6 выполнено специальное устройство управления состоянием псевдо‑ПЗУ, известное в ПЭВМ Apple как “Language Card” (LC), обеспечивающее, по желанию пользователя, подключение на адреса D000‑FFFF либо ПЗУ (Д5 или Д6), либо части оперативной памяти (память LC), работающей как псевдо-ПЗУ.

Состояние LC характеризуется тремя параметрами: состоянием чтения (ЧТ), состоянием записи (ЗП) и номером банка D (D).

Сигнал “ЧТ” (выход Д8.12) высоким уровнем разрешает чтение памяти LC и запрещает чтение ПЗУ (выход Д5 в третьем состоянии). При низком уровне сигнала разрешено чтение ПЗУ, заменяющего его в режиме "Apple" ОЗУ, и запрещено чтение памяти LC.

Сигнал “ЗП” (выход Д8.10) высоким уровнем запрещает запись в память LC и низким разрешает. Таким образом, при высоком уровне сигнала память LC работает в режиме ПЗУ, и запись по адресам D000‑FFFF вообще невозможна.

При обращении к ОП через адреса 6 сегмента (рис. 10) есть особенность, заключающаяся в том, что из‑за постоянного и неизменного наличия в адресах C000‑CFFF области ввода/вывода доступ к подключенному к этому сегменту банку памяти емкостью 8К разрешен только через адреса D000‑DFFF. С целью полного использования всей памяти ПЭВМ предусмотрена возможность разделить банк, подключенный к 6 сегменту, на две части по 4К байт с возможностью подключения каждой из них к адресам D000‑DFFF. Для этого используется сигнал “D” (выход Д8.15), уровень которого показывает, какая половина банка ОЗУ подключена к адресам D000‑DFFF.

Управление LC в режиме “Агат” осуществляется операциями записи по адресам C080‑C08F в соответствии с табл. 2.

Таблица 2

--------------------------------------------------------------------

операции | вырабатываемые сигналы | режимы работы

записи по |-------------------------------------------------------

адресу | D | ЧТ | ЗП | ПЗУ | память LC

------------|---------|--------|-------|-------|--------------------

С080/С088 | 0/1 | 1 | 1 | откл. | чтение разрешено

| | | | | запись запрещена

--------------------------------------------------------------------

С081/С089 | 0/1 | 0 | 0 | вкл. | чтение запрещено

| | | | | запись разрешена

--------------------------------------------------------------------

С082/С08А | 0/1 | 1 | 0 | откл. | чтение разрешено

| | | | | запись запрещена

--------------------------------------------------------------------

С083/С08В | 0/1 | 1 | 0 | откл. | чтение разрешено

| | | | | запись разрешена

--------------------------------------------------------------------

В режиме "Apple" управление LC осуществляется аналогично, но только выполнением операции чтения ЦП по адресам С080–С08F в соответствии с табл.3.

Таблица 3

----------------------------------------------------------------------

операции | вырабатываемые сигналы | режимы работы

чтения по |---------------------------------------------------------

адресу | D | ЧТ | ЗП | ПЗУ | память LC

------------|----------|--------|--------|--------|-------------------

С080/С088 | 0/1 | 1 | 1 | откл. | чтение разрешено

| | | | | запись запрещена

----------------------------------------------------------------------

С081+С081 | 0/1 | 0 | 0 | вкл. | чтение запрещено

/C089+C089 | | | | | запись разрешена

----------------------------------------------------------------------

С082/С08А | 0/1 | 0 | 1 | вкл. | чтение запрещено

| | | | | запись запрещена

----------------------------------------------------------------------

С083+С083 | 0/1 | 1 | 0 | откл. | чтение разрешено

/С08В+С08В | | | | | запись разрешена

----------------------------------------------------------------------

Примечание: обозначения вида С083+С083 предполагают обязательное двукратное выполнение операции чтения по адресу С083.

Операции чтения LC (в режиме "Apple" одновременно с изменением ее состояния) позволяют получить на шине данных ее подавляющее состояние. Для этого в LC используется мультиплексор Д54 и элемент Д16.6, обеспечивающий выдачу сигнала ЗП в шину данных инверсным кодом.

Непосредственное формирование сигналов управления осуществляется в ПЗУ Д14, на входы которого подаются старшие разряды шины адреса, сигналы состояния LC, R/W, блокировки ОЗУ (БЛОЗУ), блокировки ПЗУ (БЛПЗУ) и признак машины (ПМ) признак "Apple" (ПА).

Сигналы БЛОЗУ и БЛПЗУ имеют обычно высокий уровень. Низкий уровень сигнала БЛОЗУ означает, что внешнее устройство, например ячейка дополнительной памяти, установило блокировку ОЗУ и при обращении к нему по адресу 0000–BFFF. Аналогично БЛПЗУ значит, что ПЗУ и ОЗУ частично отключаются при адресных обращениях к адресам постоянной памяти.

Выходы Д14 определяются через входные сигналы по формулам:

A12Ф = A12 & AD + AD & D & (1 - ЧТ & ЗП)

W = 1 - R/W & (БЛОЗУ & АОЗУ + БЛПЗУ & АПЗУ & ЗП)

ВКОЗУ = (1 - БЛОЗУ & АОЗУ) & (1 - БЛПЗУ & АПЗУ & (R/W & (ПМ + ПМ & ЧТ) + R/W & ЗП))

F = 1 - БЛПЗУ & AF & ПМ & R/W & ЧТ

C = A15 & A14 & A13 & A12

РП = ПМ & АПЗУ & R/W & ЧТ

DE = 1 - БЛПЗУ & ADE & ПМ & R/W & ЧТ

ВКПЗУ = 1 - БДПЗУ & АПЗУ & ПМ & R/W & ЧТ

где

АОЗУ = A15 & A14

АПЗУ = A15 & A14 & (1 - A13 & A12)

AF = A15 & A14 & A13 & A12

AD = A15 & A14 & A13 & A12

ADE = A15 & A14 & (A13 & A12 + A13 & A12)

Примечание: знаки + и & обозначают соответственно логическое сложение и умножение, а 1-х обозначает дополнение x до 1.

Назначение выходных сигналов следующее:

A12Ф — модифицированный 12-й разряд адреса, используемый в качестве 12-го разряда адресного входа ОЗУ ячеек. A12Ф совпадает с A12 шины адреса при обращении ЦП по любым адресам кроме D000–DFFF. В противном случае A12Ф совпадает с номером банка D, заданного в LC.

W — разрешение записи в ОЗУ ячейки (активный уровень низкий). Разрешает запись в ОЗУ при операциях записи (R/W=0) по адресам 0000–BFFF, если нет блокировки ОЗУ, или по адресам D000–FFFF, если нет блокировки ПЗУ и разрешена запись в память LC.

ВКOЗУ — выбор ОЗУ (активный уровень низкий). Высокий уровень сигнала блокирует формирование строба выборки строк (RAS) микросхем памяти и устанавливает в третье состояние буферные регистры памяти Д47–Д48. ВКОЗУ=0 при обращении ЦП по адресам 0000–BFFF, если нет блокировки ОЗУ, или при обращении ЦП по адресам D000–FFFF, если нет блокировки ПЗУ и LC разрешает работу (ЦП выполняет операцию чтения при ЧТ=1 или операцию записи при ЗП=0). При чтении в режиме "Apple" ВКОЗУ=0 независимо от состояния сигнала ЧТ.

F — сигнал разрешения выборки ПЗУ D6 (активный уровень низкий). Разрешает выборку ПЗУ при операциях чтения по адресам F000–FFFF, если нет блокировки ПЗУ и запрещено чтение памяти LC. В режиме "Apple" выборка ПЗУ запрещена независимо от состояния LC.

C — признак обращения ЦП к адресам ввода/вывода (активный уровень высокий). С помощью элементов D24.1–3 этот сигнал стробируется по фазе тактового сигнала Ф0 (для формирования сигналов управления вводом/выводом) и из него выделяется строб ПЗУ ввода/вывода (I/O STB), совпадающий с низким уровнем сигнала Ф1 при наличии на адресной шине кода адреса в диапазоне С800–CFFF.

РП — признак разделения памяти (активный уровень высокий). Формируется только при работе ПЗВМ в режиме "Apple", когда ЦП читает по адресам D000–FFFF, а LC запрещает чтение ОЗУ (ЧТ=0). В этом режиме узел управления подставляет ЦП вместо ПЗУ дополнительный банк ОЗУ, номер которого записан в Д21 и соответствует номеру сегмента адресного пространства +8 (см. п. 4.3.1). Режим разделения памяти введен для обеспечения загрузки системного программного обеспечения перед Apple-II.

DE — сигнал разрешения выборки ПЗУ D5 (активный уровень низкий). Аналогичен сигналу "F", но действует при операциях чтения по адресам D000–EFFF.

ВКПЗУ — сигнал разрешения выборки ПЗУ (Д5 или Д6). Низким уровнем запрещает работу шинного формирователя данных Д4, переводя его выходы в третье состояние. Одновременно, в зависимости от адреса на адресных шинах, формируется сигнал "F" или DE. Сигнал формируется только в режиме "Агага" при операциях чтения по адресам D000–FFFF, если нет блокировки ПЗУ (БЛПЗУ=1) и запрещено чтение памяти LC.

Цикл управления памятью в каждом такте формирует все управляющие сигналы сразу после установления кода адреса на ША ЦП в течение Ф0=0 (рис.2). Это позволяет сформировать на мультиплексорах адреса ОЗУ (элементы Д28-Д29) все адреса до начала процессорной фазы (фазы Ф0=1) и тем самым подготовить ОЗУ к процессу чтения/записи данных.

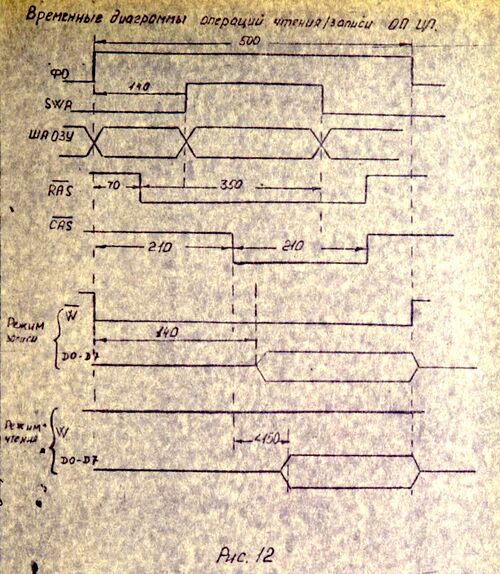

4.3.3. Операции чтения/записи

Доступ ЦП к ОЗУ ячейки осуществляется во время положительной фазы сигнала Ф0 (рис.12). Эта фаза (фаза процессора) переключает мультиплексоры адреса Д25–Д29 в режим передачи ОЗУ адресов, поступивших от ЦП (A1–A12), узла распределения памяти (Q0-Q3) и узла управления (A12Ф). При этом к ША ОЗУ подключаются разряды A8–A11, A12Ф, Q0–Q2, передающие младшие 8 разрядов адреса ОЗУ (код номера строки ячейки, выбираемой на микросхемы памяти Д31–Д46). По зпднему фронту сигнала RAS эти 8 разрядов адреса запоминаются во внутреннем адресном регистре микросхем. После этого, по сигналу переключения адреса SWA (входы Д25.14–Д29.14) к шине адреса ОЗУ подключаются остальные 8 разрядов адреса, задающие код номера столбца, и по заднему фронту сигнала CAS также вписываются во внутренние регистры адреса микросхем памяти. На этом адресная часть цикла обращения к памяти заканчивается.

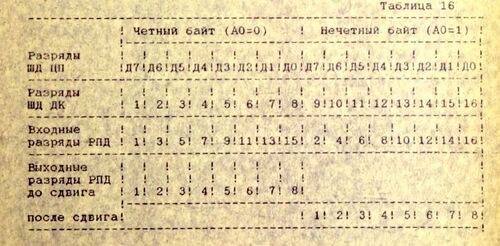

В операциях чтения ОЗУ высокий уровень сигнала "W", подаваемый со входа Д30.2 на Д14.10, обеспечивает работу микросхем Д31–Д46 на выдачу информации. Через время, равное времени выборки адреса, на их выходах устанавливается код, соответствующий содержимому адресуемой ячейки ОЗУ и через буферные регистры Д47, Д48 (БРП1 и БРП2), передается в шину данных ЦП. Управление выдачей информации с буферных регистров осуществляется с помощью дешифратора Д30, обеспечивающего по значению младшего разряда адреса A0 разрешение выдачи только одному из них. При A0=0 выдача разрешена первому регистру (Д47) и при A0=1 - второму. При наличии высокого уровня стробирующего сигнала на входе C, регистр, которому разрешена выдача информации на виду данных, находится в "прозрачном" режиме, когда состояние выходов регистра полностью определяется состоянием его входов.

По спаду стробирующего сигнала в регистре фиксируется его состояние, что гарантирует выдачу на ШД ЦП считанного из ОЗУ кода до окончания фазы процессора. На этом операция чтения заканчивается. При выполнении операции записи узел управления памяти устанавливает на входе Д30.2 низкий уровень сигнала "W", который переводит один из массивов ОЗУ (первый для A0=0 и второй для A0=1) в режим записи. Запись байта данных, поступающего с ШД ЦП, производится по низкому уровню сигнала CAS в соответствующий массив ОЗУ. При этом буферные регистры остаются отключенными, и их выходы находятся в третьем состоянии.

4.3.4. Обращение ДК к памяти

ОЗУ обеспечивает двух пользователей: системную магистраль (ЦП и активные внешние устройства) и дисплейный контроллер. Обслуживание осуществляется попеременно на основе способа разделения фазы, предусматривающего разделение периода импульсов основной тактовой частоты (сигнал Ф0) на две равные части — фазу процессора и фазу ДК. Дисплейный контроллер получает доступ к ОЗУ во время фазы Ф0=0. На это время все микросхемы памяти переводятся в режим считывания, а буферные регистры Д47 и Д48 отключаются. Фаза ДК переключает мультиплексоры адреса на адреса, поступающие от ДК. Сначала к ША ОЗУ подключаются 8 разрядов ША ДК, соответствующие сигналу RAS. После этого к шине ОЗУ по сигналу переключения адресов SWA подключаются остальные 8 разрядов адреса ША ДК и записываются во внутренний адресный регистр микросхем памяти по заднему фронту сигнала CAS. Через время, равное времени выборки относительно сигнала CAS, два байта информации из адресуемых ячеек обоих массивов ОЗУ поступают на 16-разрядный буферный регистр данных, выполненный на двух микросхемах К555ИР23 (Д49 и Д50), и запоминаются на выходах по фронту сигнала RAS.

На этом цикл обращения дисплейного контроллера к ОЗУ заканчивается. Временные диаграммы чтения памяти дисплейным контроллером аналогичны диаграммам, приведенным на рис. 12.

4.3.5. Регенерация памяти

Используемые в ячейке микросхемы динамической памяти требуют 128 циклов регенерации, осуществляемой перебором младших семи разрядов адреса ША ОЗУ по сигналу RAS. Время регенерации должно превышать 2 мс. Особенности работы ДК при формировании изображений на экране видеоконтрольного устройства позволяют совместить регенерацию памяти с обращением ДК к ОЗУ. Это позволяет избежать использования для организации регенерации каких-либо специальных аппаратных и временных затрат.

4.4. Дисплейный контроллер

4.4.1. Общие принципы работы ДК

Процесс формирования изображения дисплейным контроллером основывается на развертке (или как его еще называют растровом телевизионном) принципе развертки изображения, что предопределяет жесткую последовательность работы всех функциональных узлов ДК. Поэтому, прежде чем перейти к описанию работы ДК, необходимо напомнить основные положения растрового принципа развертки:

- изображение на экране складывается из последовательности отдельных кадров, следующих с частотой кадровой развертки равной 50 Гц (построчной развертка), что есть время развертки одного кадра составляет 20 мс;

- каждый кадр изображения образуется из отдельных строк с последовательностью развертки слева направо сверху вниз;

- частота строчной развертки составляет 15625 Гц, то есть время развертки одной строки 64 мкс;

- изображение формируется на экране в течение прямого хода луча по строке и по кадру; на время обратного хода луча, в течение которого происходит возврат луча в исходное положение, изображение гасится;

- изображение формируется по мере продвижения луча (лучей) по строке - засветкой в нужный момент требуемых точек экрана заданным цветом.

Исходя из этих положений, можно сформулировать основные задачи возлагаемые на ДК.

- формирование строчной и кадровых синхроимпульсов требуемой частоты и длительности для обеспечения синхронизации с ВКУ.

- последовательное формирование адресов для обращения в нужную область памяти экрана по мере развертки изображения;

- преобразование информации, поступающей из памяти, в вид, способный непосредственно управлять лучами ВКУ в соответствии с требуемым режимом отображения информации;

- гашение изображения на время обратного хода луча по строке и по кадру, то есть формирование рабочего поля экрана в соответствии с требуемым форматом.

Процесс формирования изображения дисплейным контроллером определяется также и особенностями каждого из требуемых режимов отображения информации, которые наряду с основными параметрами определяют, где, и в каком порядке в памяти экрана хранится информация об изображении, каким образом считанная из памяти информация трансформируется в изображение, как задается цветовая окраска изображения.

4.4.2. Режимы отображения информации на экране.

Содержимое любой части оперативной памяти (исключения будут оговорены отдельно) может быть отображено на экране ВКУ в одном из 9 возможных режимов отображения. Размер отображаемой области ОП (памяти экрана) зависит от режима отображения. Основные характеристики режимов приведены в табл.4.

Таблица 4 ┌───────┬────────────────┬─────────────┬────────────┬─────────────┬────────────┐ │ Режим │ Режим │ Формат │ Размер │ Число цве- │ Объем │ │ работы│ отображения │ изображения │ элемента │ ов/палитр │ видео- │ │ ДК ПВМ│ │ (элементов │ разложения │ элемента │ ОЗУ │ │ │ │ разложения) │ (точек) │ разложения │ (байт) │ ├───────┼────────────────┼─────────────┼────────────┼─────────────┼────────────┤ │ "Агат"│ Графический │ 512x256 │ 1x1 │ 2/4 │ 16 K │ │ │ МГДП │ │ │ │ │ │ │ Графический │ 256x256 │ 1x1 │ 2/4 │ 8 K │ │ │ МГВР │ │ │ │ │ │ │ Графический │ 256x256 │ 1x1 │ 4/4 │ 16 K │ │ │ ЦГВР │ │ │ │ │ │ │ Графический │ 128x128 │ 2x2 │ 16 │ 8 K │ │ │ ЦГCР │ │ │ │ │ │ │ Текстовый │ 32х32 │ знакоместо │ 8/4 │ 2 K │ │ │ Т32 │ знакоместа │ 7x8 │ │ │ │ │ │ │ символ 5х7 │ │ │ │ │ Текстовый │ 64х32 │ знакоместо │ 2/4 │ 2 K │ │ │ Т64 │ знакоместа │ 7x8 │ │ │ │ │ │ │ символ 5х7 │ │ │ ├───────┼────────────────┼─────────────┼────────────┼─────────────┼────────────┤ │"Apple"│ Графический │ 280x192 │ 1x1 │ 6 с огра- │ 7.5 K │ │ │ HGR │ │ │ ничениями │ │ │ │ Текстовый │ 40х24 │ знакоместо │ 2/4 │ 1 K │ │ │ Т40 │ знакоместа │ 7x8 │ │ │ │ │ │ │ символ 5х7 │ │ │ │ │ Смешанный │ 280x160 │ │ │ │ │ │ графика HGR и │ точек, │ │ │ │ │ │ 4 строки │ 40х4 │ │ │ │ │ │ текста │ знакоместа │ │ │ │ └───────┴────────────────┴─────────────┴────────────┴─────────────┴────────────┘

4.4.3. Отображение информации в режиме "Agat"

4.4.3.1 Цветные графические режимы

Дисплейный контроллер в режиме "Агат" имеет два цветных графических режима: среднего (ЦГСР) и высокого (ЦВГР) разрешения.

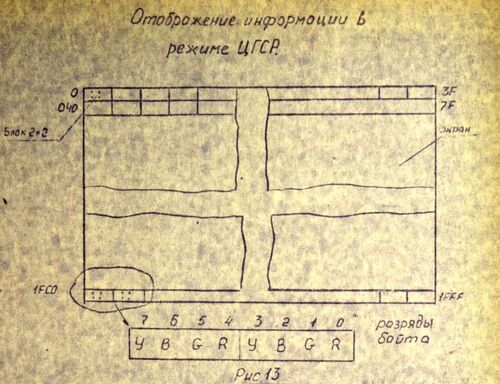

Режим ЦГСР иногда называют псевдографическим, так как элементом разложения в этом режиме является не точка, а некоторая совокупность точек, размером 2x2, засвечиваемая на экране одним цветом и получившая название блок (pixel).

Формат изображений на экране: 128 строк по 128 блоков в строке. В этом случае каждый байт в памяти экрана разделяется на две тетрады, которые содержат код цвета соответствующего блока. Старшая тетрада первого байта экранной строки (разряды 4-7) содержит код цвета блока, расположенного с левого края экрана. Младшая тетрада (разряды 0-3) содержит код цвета следующего по строке блока и т. д. Для отображения одной строки блока требуется 64 байта. Выборка информации из памяти экрана строго последовательна: первые 64 байта хранят информацию для первой строки блоков, вторые 64 байта - для второй строки и т. д. Для отображения одного полного кадра требуется памяти экрана общим объемом 8 Кбайт (рис. 13). Четыре разряда для кодирования цвета цвета позволяют иметь для каждого блока 16 различных цветов. Возможные цвета и их кодировка приводятся в табл.5.

Таблица 5 ┌───────────────┬───────────┬───────────────┬─────────────┐ │ Код цвета │ Цвет │ Код цвета │ Цвет │ ├───────────┬───┼───────────┼───────────┬───┼─────────────┤ │ 0000 │ 0 │ черный │ 1000 │ 8 │ черный │ │ 0001 │ 1 │ красный │ 1001 │ 9 │ коричневый │ │ 0010 │ 2 │ салатовый │ 1010 │ A │ зеленый │ │ 0011 │ 3 │ желтый │ 1011 │ B │ хаки │ │ 0100 │ 4 │ синий │ 1100 │ C │ темно-синий │ │ 0101 │ 5 │ сиреневый │ 1101 │ D │ фиолетовый │ │ 0110 │ 6 │ голубой │ 1110 │ E │ бирюзовый │ │ 0111 │ 7 │ белый │ 1111 │ F │ серый │ └───────────┴───┴───────────┴───────────┴───┴─────────────┘

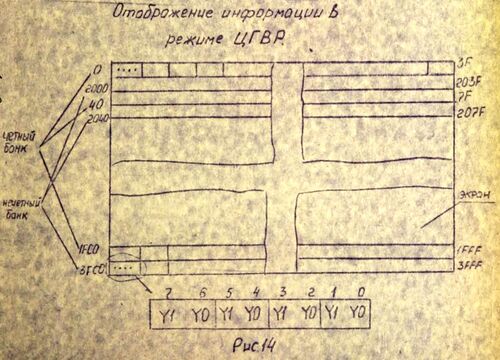

Цветной графический режим высокого разрешения обеспечивает отображение в пределах рабочего поля экрана 65534 точек в виде матрицы из 256 рядов по 256 точек в ряду (рис. 14). Каждой точке изображения на экране соответствуют два бита в памяти экрана. Каждый байт в памяти экрана хранит 2-разрядные коды для засветки 4-х точек. Старшие два разряда (6, 7) первого байта экранной строки задают код цвета точки, расположенной с левого края экрана. Разряды 4 и 5 задают код цвета следующей точки и т. д. Для отображения одной строки требуется 64 байта.

Для отображения одного полного кадра требуется 16К байт памяти экрана, которая разделяется на две равные части, соответствующие двум соседним банкам физической оперативной памяти. Банк с четным номером (0, 2 и т.д.) обеспечивает хранение четных строк развертки, а банк с нечетным номером (1, 3 и т.д.) нечетных строк.

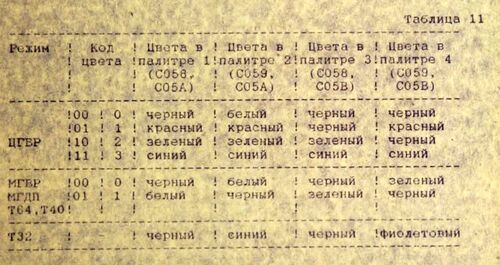

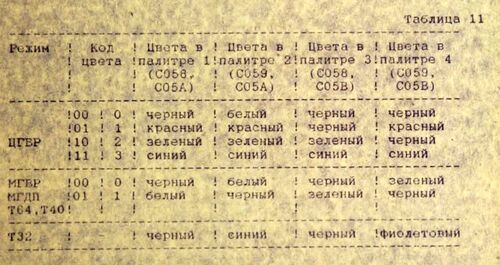

Два разряда кода цвета дают возможность засвечивать точки в 4-х цветах. Соответствие цветов отображаемых на экране точек кодам цвета в памяти экрана (палитра) можно программно изменять. Всего имеется четыре палитры. Цвет точки, в зависимости от палитры приведен в табл.11.

4.4.3.2. Монохромные графические режимы

Монохромных графических режимов также два: монохромный графический режим высокого разрешения (МГВР) и монохромный графический режим удвоенной плотности (МГДП).

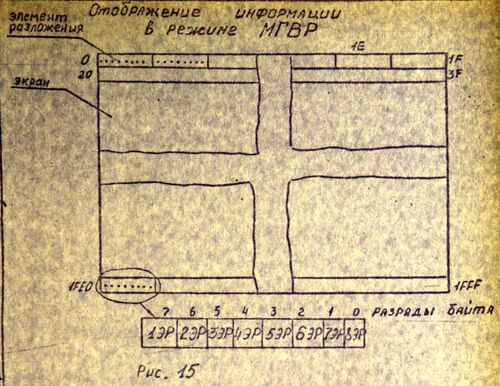

Режим МГВР имеет такой же формат изображения, что и цветной графический режим высокого разрешения 256х256. Но в этом режиме, в отличие от режима ЦГВР, каждой точке экрана соответствует не два бита в памяти экрана, а всего лишь один. "1" высвечивает соответствующую точку цветом, указанным в табл.11, а "0" гасит ее (выводит в цвете фона). Соответственно вдвое уменьшается и объем памяти экрана: для отображения одной экранной строки требуется 32 байта, и 8 Кбайт на один полный кадр. Старший разряд (7) первого байта экранной строки отображается с левого края экрана, следующим отображается шестой разряд и т.д. За последним разрядом (0) первого байта отображается старший разряд следующего байта и так до нулевого арзряда последнего 32-го байта строки (рис.15). Состояние каждого бита в памяти экрана определяет цвет засветки точки на экране в зависимости от палитры в соответствии с табл.11.

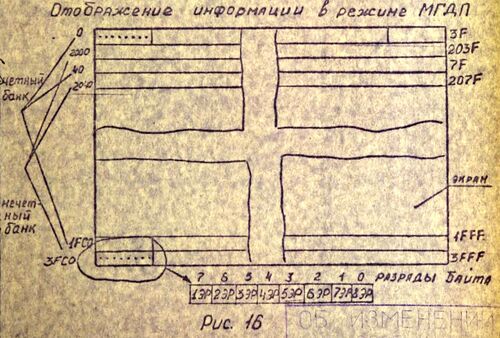

В монохромном графическом режиме удвоенной плотности (МГП), в отличие от режима МГВР, формат изображения по горизонтали имеет удвоенное число точек — 512 (рис.16). Соответственно вдвое увеличивается и объем памяти экрана: до 64 байт на строку и до 16К байт на полный кадр. Также как и в режиме ЦГВР память экрана делится на две равные части, соответствующие банкам оперативной памяти: банк с четным номером обеспечивает хранение четных экранных строк, а банк с нечетным номером — нечетных строк. Цвет засветки точек также зависит от палитры в соответствии с табл. 11.

4.4.3.3. Текстовые режимы.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 00 | ▃ | ▅ | ▇ | ⋁ | ┐ | ∀ | ∃ | ← | ╭ | ╮ | ╯ | ╰ | ⬐ | ─ | │ | |

| 10 | ┌ | ┬ | ┐ | ├ | ┼ | → | ↗ | ↙ | ↖ | ↑ | ↓ | ─ | ┤ | └ | ┴ | ┘ |

| 20 | α | β | γ | ε | λ | μ | π | ρ | τ | φ | ψ | ω | ∑ | Δ | ÷ | |

| 30 | ⁰ | ¹ | ² | ³ | ⁴ | ⁵ | ⁶ | ⁷ | ⁸ | ⁹ | ⁻ | ≡ | ≤ | ≠ | ≥ | ± |

| 40 | ` | a | b | c | d | e | f | g | h | i | j | k | l | m | n | o |

| 50 | p | q | r | s | t | u | v | w | x | y | z | { | ¦ | } | ~ | |

| 60 | ю | а | б | ц | д | е | ф | г | х | и | й | к | л | м | н | о |

| 70 | п | я | р | с | т | у | ж | в | ь | ы | з | ш | э | щ | ч | ъ |

| 80 | @ | A | B | C | D | E | F | G | H | I | J | K | L | M | N | O |

| 90 | P | Q | R | S | T | U | V | W | X | Y | Z | [ | \ | ] | ^ | _ |

| A0 | ! | " | # | ¤ | % | & | ' | ( | ) | * | + | , | - | . | / | |

| B0 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | : | ; | < | = | > | ? |

| C0 | @ | A | B | C | D | E | F | G | H | I | J | K | L | M | N | O |

| D0 | P | Q | R | S | T | U | V | W | X | Y | Z | [ | \ | ] | ^ | _ |

| E0 | Ю | А | Б | Ц | Д | Е | Ф | Г | Х | И | Й | К | Л | М | Н | О |

| F0 | П | Я | Р | С | Т | У | Ж | В | Ь | Ы | З | Ш | Э | Щ | Ч | Ъ |

Работа ДК в этих режимах основывается на традиционном знакоместном методе формирования изображения с использованием ПЗУ знакогенератора. В этих режимах все рабочее поле экрана разбивается на знакоместа размером 7х8 (8 строк по 7 точек в строке). На каждом знакоместе может быть расположен либо один алфавитно-цифровой символ, размер которого составляет обычно 5х7 точек, либо графический символ размером равным размеру знакоместа (7х8). Полиграммы (точечные матрицы) символов хранятся в ПЗУ знакогенератора. В памяти экрана хранится только коды тех символов, вывод которых предполагается на соответствующих знакоместах. Набор и количество возможных символов определяется объемом ПЗУ знакогенератора и числом разрядов, используемых для задания кода различных символов. Набор символов и их коды приводятся в табл. 6.

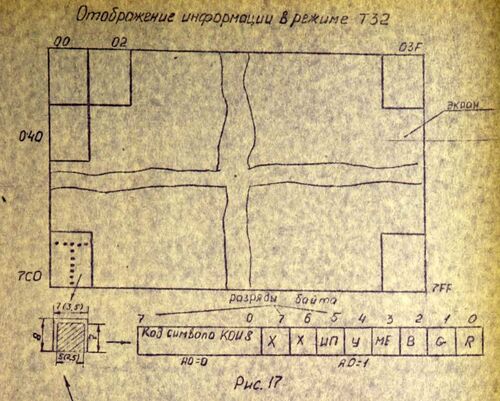

В цветном текстовом режиме (Т32) каждому знакоместу экрана соответствуют 2 байта в памяти экрана (рис.17). На экране при этом располагается 1024 знакоместа (32 строки по 32 символа). Первый (четный) байт, когда A0=0, содержит код символа, по КОИ-8, который должен быть выведен на данном знакоместе. Второй (нечетный) байт, когда A0=1, содержит следующую управляющую информацию:

- R,G,B (0-й, 1-й и 2-й биты) — разряд кода цвета символа. Четыре палитры позволяют менять цвет фона в соответствии с табл.11.

- ИП (5-й бит) — разряд инверсии подсвета, задает режим вывода символа на экран: нормальный или инверсный. Нормальный символ выводится на темном фоне тем цветом, код которого задан в разрядах цвета. Инверсный символ выводится черным на фоне цветного знакоместа, цвет которого задан теми же разрядами цвета.

- ME (3-й бит) — разряд мерцания, задает режим мерцания, в результате символ отображается поочередно то инверсным, то нормальным с частотой переключени 5 Гц.

Режим отображения символа на экране в зависимости от состояния этих разрядов приведены в табл.7

Таблица 7 ┌───────────────┬─────────────────────────┐ │Код разрядов │Вывод символа на экран │ │ИП │МЕ │ │ ├─────┼─────────┴─────────────────────────┤ │0 │ 0 │Инверсный │ │0 │ 1 │Мерцающий │ │1 │ 0 │Нормальный │ │1 │ 1 │Нормальный │ └─────┴───────────────────────────────────┘

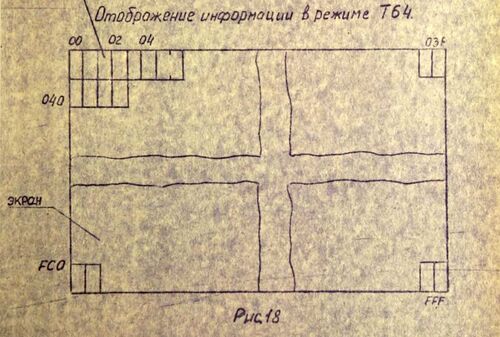

В монохромном текстовом режиме (T64) на экран выводится 2048 символов (32 строки по 64 символа). При этом соотношение между размерами точки символа и символа остается прежним, а точка изображения на экране имеет вдвое меньший размер по строке (рис.18). Это достигается увеличением тактовой частоты вывода символов до 10.5 мГц. Каждому знакоместу на экране соответствует один байт в памяти экрана (код КОИ-8 выводимого символа). Цвет выводимых символов определяется палитрой по табл.11.

4.4.4. Отображение информации в режиме "Apple"

4.4.4.1. Расположение памяти экрана в адресном поле ЦП.

Память экрана в режиме ПЭВМ Apple II состоит из 2-х частей, занимающих каждая свою отдельную фиксированную зону в адресном пространстве. Первая часть представляет собой память экрана для отображения информации в текстовом режиме. В адресном пространстве ШП она занимает адреса 400-BFF:

- 400-7FF первая страница;

- 800-BFF вторая страница.

Вторая часть обеспечивает хранение информации для отображения в режиме HGR и также объединяет 2 страницы:

- 2000-3FFF первая страница;

- 4000-5FFF вторая страница.

Любая из страниц может быть использована для отображения одного полного кадра изображения. При этом часть памяти из адресного пространства каждой страницы не используется для целей отображения: из общего объема памяти в 8К байт для каждой страницы используется в качестве памяти экрана только 7.5К байт.

4.4.4.2. Графический режим высокого разрешения.

Этот режим можно было бы отнести к традиционным методам побитовой (позменной) графики, если бы не его специфические особенности. Эти особенности настолько существенны, что можно выделить этот режим в самостоятельную разновидность методов побитовой графики: метод побитовой графики с цветовыми ограничениями. Так как этот метод впервые был использован в ПЭВМ Apple II, то его также можно было бы назвать методом Apple II.

Суть данного метода состоит в том, что цвет отображаемой точки изображения зависит не только от информации, хранящейся в памяти экрана, но и от нескольких дополнительных факторов:

- от местоположения точки на экране (четная или нечетная колонка);

- от кода одного невысвечиваемого бита для каждой группы из 7-ми точек;

- от засветки соседних точек справа и слева.

Основное преимущество такого метода заключается в экономии памяти экрана. Легко подсчитать, что для отображения изображения традиционным методом побитовой графики форматом 280x192 с 6-ю цветами на точку необходимо 20К байт памяти экрана.

Это более чем в 2,5 раза больше объема памяти, требуемого по методу Apple II.

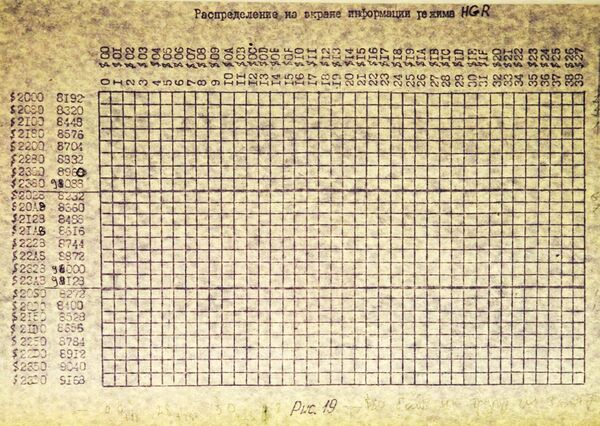

4.4.4.2.1 Хранение информации в памяти

Для режима HGR порядок расположения на экране информации, хранимой в памяти иллюстрируется на рис.19. Отображаемая страница памяти экрана (первая или вторая) разбивается на 8 областей по 1К байт каждая. Первая область обеспечивает хранение информации для 24-х строк изображения, вторая область содержит информацию для следующих 24-х строк и т.д. В пределах первой области (адреса 2000-23FF) информация располагается следующим образом:

- первые 40 байт задают первую телевизионную строку (адреса 2000-2027);

- вторые 40 байт задают 65-ую строку (2028-204F);

- следующие 40 байт задают 129-ую строку (2050-2077);

- 8 байт не используется для целей отображения (2078-207F);

- 40 байт - 9-ая строка (2080-20A7);

- 40 байт - 73-я строка (20A8-20CF);

- 40 байт - 137-ая строка (20D0-20F7);

- 8 байт не используются для отображения (20F8-20FF) и т.д.

В пределах следующей области (адреса 2400-27FF) хранится информация о следующих 24 строках изображения:

- 40 байт задают 2-ую строку (2400-2427);

- 40 байт - 66-ая строка (2428-244F);

- 40 байт - 130-ая строка (2450-2477);

- 8 байт не используются (2478-247F);

- 40 байт - 10-ая строка (2480-24A7);

- 40 байт - 74-ая строка (24A8-24CF);

- 40 байт - 138-ая строка (24D0-24F7);

- 8 байт не используются (24F8-24FF) и т.д.

Чтобы получить адрес любого отображаемого на экране байта, необходимо сложить следующие адреса (см. рис.19):

- адрес строки в пределах младшей области памяти экрана - адресах 2000-23F7 задающих строки 1,9,17,25,33 и т.д.

- адрес байта в пределах адресов строки — 40 байт (00-27);

- адрес области памяти экрана в соответствии с табл.8.

таблица 8 ┌────────────────┬───────────────────────────────────────────────────────┐ │Адрес области │ Строки, задаваемые в пределах данной │ │памяти экрана │ области экрана │ ├────────────────┼───────────────────────────────────────────────────────┤ │0000 │ 1,9,17,25,33,41,49,57,65,73,81,89,97,105, │ │ │ 113,121,129,137,145,153,161,169,177,185 │ ├────────────────┼───────────────────────────────────────────────────────┤ │0400 │ 2,10,18,26,34,42,50,58,66,74,82,90,98,106, │ │ │ 114,122,130,138,146,154,162,170,178,186 │ ├────────────────┼───────────────────────────────────────────────────────┤ │0800 │ 3,11,19,27,35,43,51,59,67,75,83,91,99,107, │ │ │ 115,123,131,139,147,155,163,171,179,187 │ ├────────────────┼───────────────────────────────────────────────────────┤ │0C00 │ 4,12,20,28,36,44,52,60,68,76,84,92,100,108, │ │ │ 116,124,132,140,148,156,164,172,180,188 │ ├────────────────┼───────────────────────────────────────────────────────┤ │1000 │ 5,13,21,29,37,45,53,61,69,77,85,93,101,109, │ │ │ 117,125,133,141,149,157,165,173,181,189 │ ├────────────────┼───────────────────────────────────────────────────────┤ │1400 │ 6,14,22,30,38,46,54,62,70,78,86,94,102,110, │ │ │ 118,126,134,142,150,158,166,174,182,190 │ ├────────────────┼───────────────────────────────────────────────────────┤ │1800 │ 7,15,23,31,39,47,55,63,71,79,87,95,103,111, │ │ │ 119,127,135,143,151,159,167,175,183,191 │ ├────────────────┼───────────────────────────────────────────────────────┤ │1C00 │ 8,16,24,32,40,48,56,64,72,80,88,96,104,112, │ │ │ 120,128,136,144,152,160,168,176,184,192 │ └────────────────┴───────────────────────────────────────────────────────┘

4.4.4.2.2. Представление информации на экране

1) Одной точке на экране соответствует один бит в памяти экрана.

2) Из каждого байта памяти на экране отображается 7 бит. Восьмой (старший) бит используется для выбора цвета точек данного байта и на экране не отображается.

3) Для отображения одной телевизионной строки используется последовательное расположение в памяти 40 байт. Младший бит из первого байта каждого телевизионной строки отображается на левом краю экрана, следующим отображается второй бит, за ним третий и т.д. После седьмого бита первого байта отображается первый бит из следующего байта строки и т.д.

4.4.4.2.3. Цветовая окраска изображения

1) Точки, заданные в памяти логическим "0", будут всегда черными, независимо от их расположения и состояния неотображаемого бита.

2) Любые две точки, расположенные рядом на экране и заданные в памяти логической "1", всегда высвечиваются на экране, как белые, даже если соответствующие им биты содержатся в разных байтах.

3) Точки в четных колонках (0,2,4...278) экрана могут быть черными, фиолетовыми или синими.

4) Точки в нечетных колонках (1,3,5...279) могут быть черными, зелеными или красными.

5) Цвет точек, заданных в памяти логической "1" определяется состоянием неотображаемого бита данного байта и расположением точки в колонках. Точки, расположенные в четных колонках, будут синими, если неотображаемый бит байта равен "0", и фиолетовыми, если неотображаемый бит байта равен "1". Соответственно для нечетных колонок точки будут красными при "0" и зелеными при "1" в неотображаемом бите.

4.4.4.3. Текстовый режим.

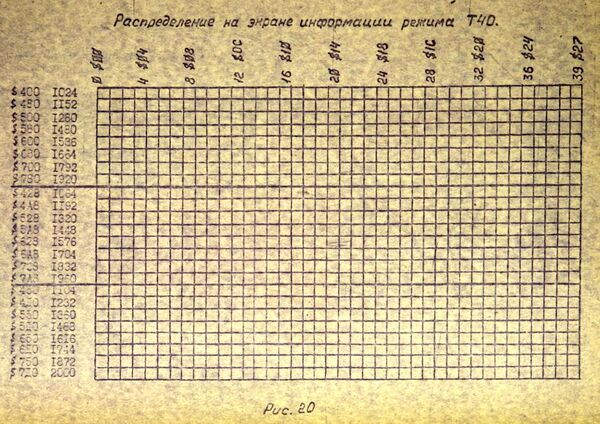

В текстовом режиме "Apple" (T40) на экран выводится 24 строки по 40 символов. В пределах одной страницы информация из памяти экрана располагается следующим образом (рис.20):

- первые 40 байт задают первую строку символов (адреса 400-427);

- вторые 40 байт задают 9-ую строку символов (428-44F);

- следующие 40 байт задают 17-ую строку символов (450-477);

- 8 байт не используются (478-47F);

- 40 байт - 2-ая строка (480-4A7);

- 40 байт - 10-ая строка (4A8-4CF);

- 40 байт - 18-ая строка (4D0-4F7);

- 8 байт не используются (4F8-4FF).

В этом режиме ЛК используется тот же самый знакоместный метод, что и в текстовых режимах Т32 и Т64, при котором каждому байту в памяти экрана соответствует одно знакоместо на экране. Изображение на экране формируется с использованием того же ПЗУ знакогенератора. Но в отличии от текстовых режимов "Агат", в этом режиме разряды ИП и МЕ, задающие режим мерцания и инверсии символа, указываются вместе с кодом символа в одном байте. В младших разрядах байта указывается код символа, а в двух старших коды ИП и МЕ.

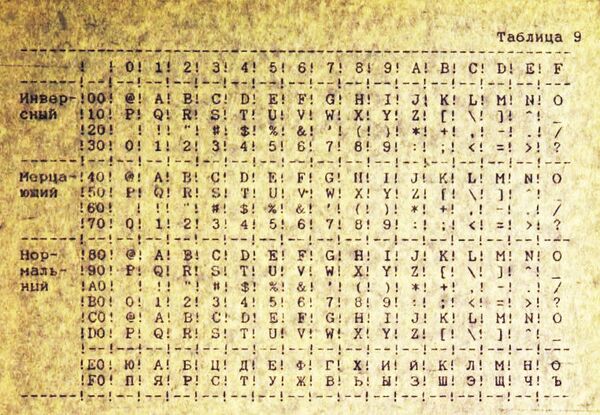

Набор и количество возможных отображаемых символов приводится в табл.9.

Режим вывода символов задаётся двумя старшими разрядами в каждом байте памяти экрана: ИП (7 разряд) и МЕ (6 разряд). В зависимости от состояния этих разрядов возможен один из трёх режимов отображения символа на экране, соответствующих табл. 7. Цвет символа (или соответственно фона) задаётся указанием палитры и в соответствии с табл. 11.

Символы русского алфавита выводятся только в нормальном режиме.

4.4.4. Смешанный режим.

В смешанном режиме изображение на экране разделяется на две части. Формирование изображения в верхней части осуществляется в графическом режиме. В нижней части выводятся 4 полных строки текста. Процесс развертки изображения в пределах каждой части происходит в соответствии с правилами вывода изображений соответствующего режима. Формат графической части составляет 280x160 точек.

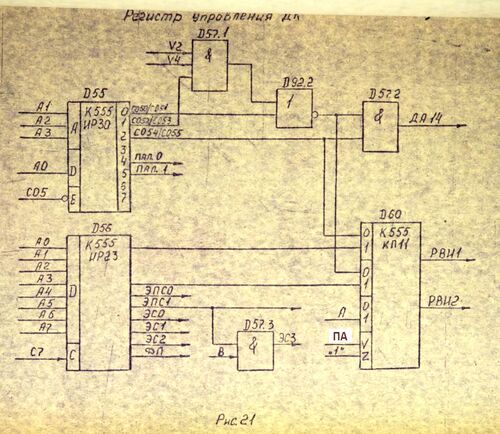

4.4.5. Регистр управления ДК

Регистр управления ДК (РУПДК) выполняет функции управления режимами вывода и информации на экран ВКУ в режимах "Агат" и "Apple" (рис.21). РУПДК включает 8-разрядный регистр хранения с адресацией К555ИРЗО (Д55), 8-разрядный буферный регистр с импульсным управлением К555ИР23 (Д56), мультиплексор 2х1 К555КП11 (Д60) и элементы Д57 и Д92.2. Переключение режимов работы ДК осуществляется с помощью программных переключателей C700-C7FF и C050-C05F.

4.4.5.1. Управление режимами отображения "Агат"

При обращении ЦП по одному из адресов C700-C7FF ДК переходит в один из 6 режимов отображения ПЭВМ "Агат", определяемого по младшим 8 разрядам адреса в соответствии с табл. 10.

Таблица 10 ┌───────────┬───────────────────────────────────────────┐ │ разряд ША │ Выполняемая функция │ ├───────────┼───────────────────────────────────────────┤ │ 7 │ признак удвоенной плотности (МГП или Т64) │ │ 6 │ ЭС2 │ │ 5 │ ЭС1 экранные страницы │ │ 4 │ ЭС0 │ │ 3 │ ЭПС1 (текст) или ЭСЗ (графика) │ │ 2 │ ЭПС0 (текст); в графике несущественен │ │ 1 │ РВИ2 │ │ 0 │ РВИ1 │ └───────────┴───────────────────────────────────────────┘

7 разряд выделен под признак удвоенной плотности. Он устанавливается в "1" для монохромных режимов графического 256x512 или алфавитно-цифрового Т64.

6-4 разряды определяют номер банка ОП 8К, выводимого на экран (отображаемой экранной страницы).

3-2 разряды для текстовых режимов указывают номер одной из четырех частей выбранного банка ОП, отображаемой на экран (номер экранной подстраницы); для графических режимов 2 разряд несущественен, а 3-й задает старший разряд кода номера выбираемого банка ОП.

1-ый и 0-ой разряды (РВИ2 и ОВИ1) определяют непосредственно режим вывода информации выбранной области памяти:

- 00 - цветной графический режим 256x256;

- 01 - цветной графический режим 128x128;

- 10 - текстовый режим Т32 или Т64;

- 11 - монохромная графика 256x256 или 256x512.

Примечание: В текстовых режимах отображается только первая половина ОП, вся оперативная память доступна ДК только в графических режимах.

4.4.5.2. Управление режимами отображения "Apple"

В случае обращения центрального процессора по адресам C050-C057, отведенным под программные переключатели ДК в режим "Apple", ДК может отображать информацию в одном из трех режимов: графическом 280x192, текстовом и смешанном.

Назначение программных переключателей следующее:

- C050/C051 - переключение в графический/текстовый режим.

- C052/C053 - отключение/включение смешанного режима.

- C054/C055 - включение первой/второй страницы памяти экрана.

Каждая пара программных переключателей ДК является независимой от двух других. Это означает, что использование программного переключателя в пределах данной пары (например пары C050, C051) не влияет на режим работы ДК, определяемый обращением МП по адресу программного переключателя в другой паре.

4.4.5.3. Переключение цветовой палитры

Как уже указывалось выше, в ПЭВМ возможно изменение цвета отображаемой на экран точки без изменения кода её цвета. Это достигается путем переключения цветовой палитры. Переход от палитры к палитре осуществляется обращением ЦП по адресу программных переключателей C058-C05B. Возможные цвета для каждой из 4-х палитр приводятся в табл. 11.

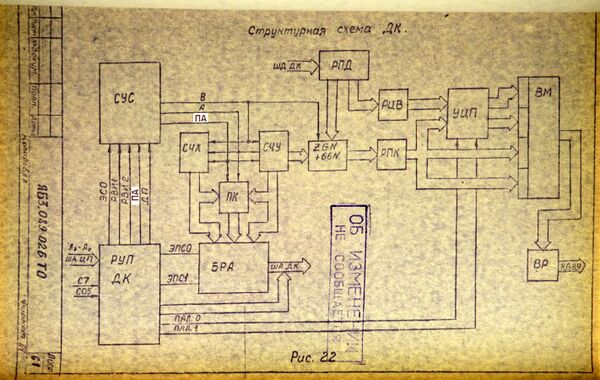

4.5. Блок-схема дисплейного контроллера

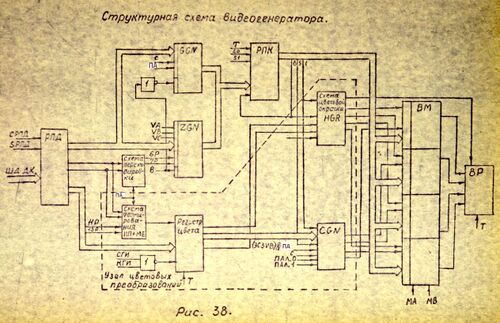

Традиционно структурная организация дисплейного контроллера предполагает его разделение на два основных функциональных блока: блок развертки изображения и видеогенератор (рис.22).

Видеогенератор обеспечивает прием информации из памяти экрана, преобразование ее в соответствии с заданным режимом отображения и выдачу преобразованной информации на выходные информационные контакты (RGBY) разъема для подключения ВКУ. Блок развертки изображения вырабатывает последовательность адресов, необходимых для опроса памяти экрана при развертке изображения, обеспечивает синхронизацию с ВКУ, вырабатывая все необходимые для этого сигналы в соответствии с растровым принципиальной развертки и осуществляет общее управление работой ДК, синхронизируя все происходящие в нем процессы.

4.5.1. Блок развертки изображения

В состав блока развертки изображения входят следующие функциональные узлы:

- счетчик строчной развертки (счетчик X),

- счетчик кадровой развертки (счетчик Y),

- преобразователь кодов (ПК),

- буферный регистр адреса (БРА),

- схема управления и синхронизации (СУС).

Основной особенностью схемотехнической реализации блока развертки изображения является использование цифровых программируемых автоматов (ЦПА). Базовой основой для построения ЦПА служит известный принцип посмтроения микропрограммируемых управляющих устройств. Составными частями такого устройства являются управляющая память (обычно ПЗУ) и регистр, с помощью которого образуется обратная связь "выход-вход" для управляющей памяти.

Для этого выходы ПЗУ подключаются ко входам регистра, выходы которого (или их часть) соответственно подключаются к адресным входам ПЗУ.

Для работы такого устройства в режиме цифрового программируемого автомата необходимо, чтобы в замкнутом контуре "ПЗУ-регистр-ПЗУ" постоянно циркулировал замкнутый цикл "адрес-данные-адрес". Рассмотрим подробнее, что происходит в процессе выполнения такого замкнутого цикла.

Данные, считанные из ПЗУ по какому-то текущему адресу, поступают на регистр и фиксируются в нем в момент прихода очередного фронта тактовых импульсов. Изменение информации в регистре инициирует процесс очередного выбора данных по адресу, указанному в регистре. По фронту следующего тактового импульса считанная из ПЗУ информация снова фиксируется в регистре, и начинается новый цикл. Необходимым условием для устойчивой работы ЦПА по такому замкнутому циклу является превышение периода тактовых импульсов над суммой времени выборки адреса ПЗУ и времени задержки регистра. При этом в ПЗУ должна быть заложена зашивка, обязывающая ЦПА к выполнению требуемых функций при определенной последовательности обхода адресов.

Такими цифровыми программируемыми автоматами в блоке развертки изображения являются три устройства: счетчик X, счетчик Y и СУС.

4.5.1.1. Счетчик строчной развертки

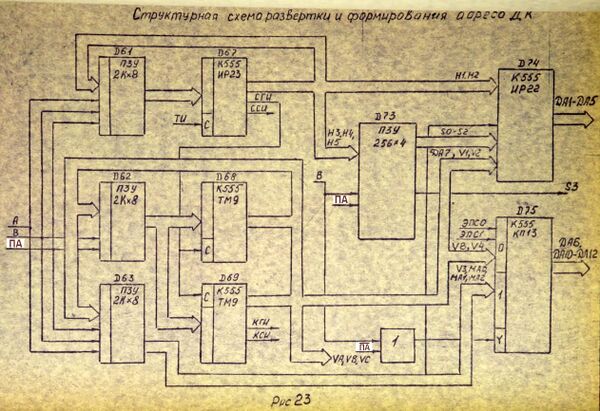

Счетчик строчной развертки (счетчик X) реализован на ПЗУ емкостью 2 Кбайт (Д61) и регистре К555ИР23 (Д67) и обеспечивает горизонтальную развертку изображения в соответствии с заданным режимом отображения (рис.23). Код, получающийся в каждом данном момент времени на выходах счетчика X, соответствует положению лучей на экранной строке.

Из 8 выходных разрядов счетчика шесть младших являются также и разрядами обратной связи, обеспечивающими функционирование ЦПА по замкнутому циклу в счетном режиме с коэффициентом пересчета, зависящим от режима отображения. Коэффициент пересчета счетчика является строго определенной величиной и задается вариантом записки ПЗУ.

Количество возможных различных вариантов записок ПЗУ зависит от числа свободных, незанятых обратными связями, адресных входов и в нашем случае равно 32 (не занято 5 адресных входов). Из них для реализации требуемых режимов отображения использовано 8 вариантов, остальные остаются незанятыми.

Внешним сигналам, определяющим задействованный вариант ПЗУ в соответствии с требуемым режимом отображения, являются адресопредставляющие для всех этих сигналов признака "Apple" (ПА) признака машины (ПМ), формируемого в регистре режимов ПЭВМ, признака графического режима В и сигнала А, вырабатываемые в СУС (см. табл. 12).

Таблица 12 ┌─────────────────┬───────────────────────┬──────────────────────┬────────────────┐ │ Входные сигналы │ Коэффициент пересчета │ Период входных │ Режим │ ├─────┬───┬───────┤ счетчика X │ импульсов │ работы │ │ ПА │ В │ А │ │ │ ДК │ ├─────┼───┼───────┼───────────────────────┼──────────────────────┼────────────────┤ │ 0 │ 0 │ 0/1 │ 64=40+24 │ 1.0 мкс │ Режимы ПЭВМ │ │ 0 │ 1 │ 0/1 │ │ │ Apple │ ├─────┼───┼───────┼───────────────────────┼──────────────────────┼────────────────┤ │ 1 │ 0 │ 0/1 │ 48=32+16 │ 1.333 мкс │ ТЗ2, Т64 │ │ 1 │ 1 │ 0 │ 42=32+10 │ 1.524 мкс │ ЦГСР,ЦГВР,МГДП │ │ 1 │ 1 │ 1 │ 21=16+5 │ 3.048 мкс │ МГВР │ └─────┴───┴───────┴───────────────────────┴──────────────────────┴────────────────┘

В таблице приводятся коэффициенты пересчета счетчика X и период тактовых пересчетных импульсов в зависимости от кодовых комбинаций этих сигналов.

Коэффициент пересчета складывается из суммы двух слагаемых: первое указывает коэффициент пересчета для прямого хода развертки строки, второе — для обратного. Значения коэффициента пересчета и периода тактовых пересчетных импульсов подобраны таким образом, чтобы обеспечить постоянный период строчной развертки (64 мкс) вне зависимости от режима отображения.

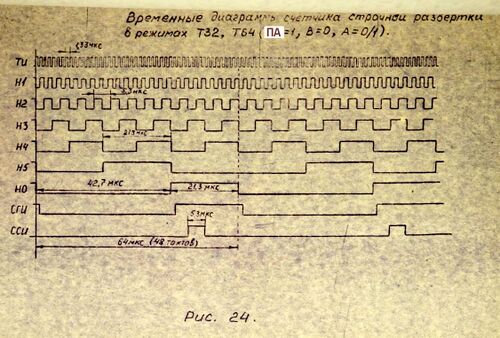

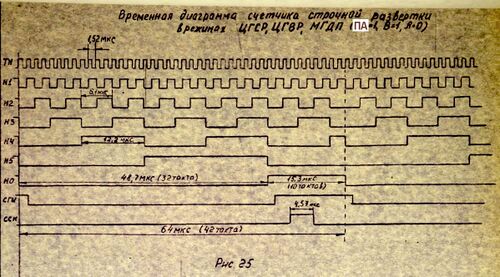

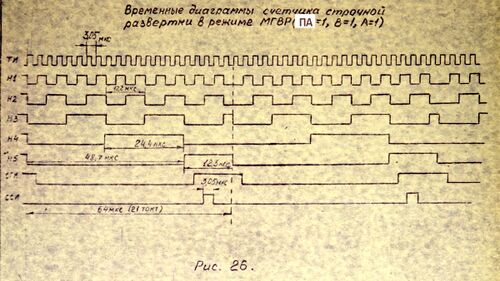

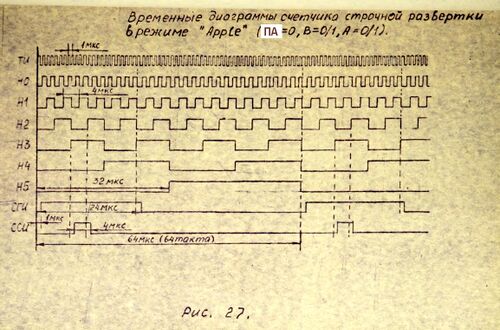

Два старших выходных разряда счетчика предназначены для формирования основных сигналов строчной синхронизации в ВКУ: строчного синхронизирующего импульса (ССИ) и строчного гасящего импульса (СГИ). Параметры этих импульсов и их взаимное расположение для различных режимов отображения показаны на рис. 24-27. Сигнал СГИ высоким уровнем выключает выдачу изображения на экране на время обратного хода и часть времени прямого хода, формируя тем самым левую и правую границы изображения на экране. Сигнал ССИ непосредственно синхронизирует развертку изображения в ВКУ.

4.5.1.2. Счетчик кадровой развертки

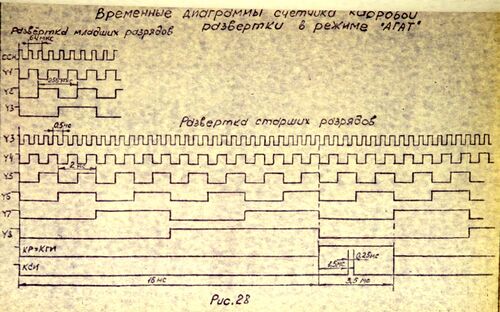

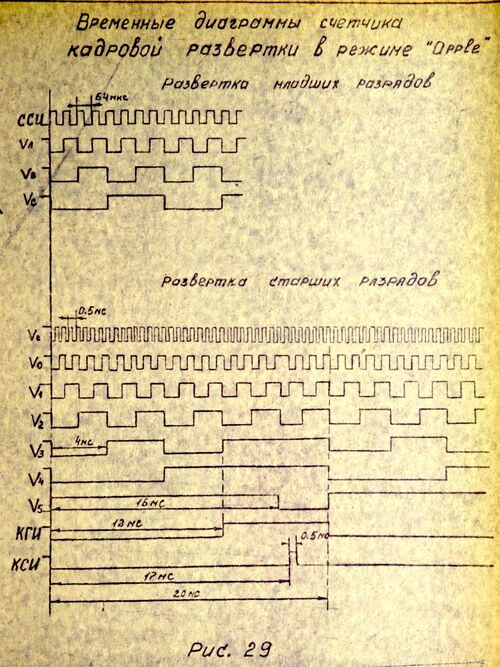

Счетчик кадровой развертки (счетчик Y, рис. 23) реализован на двух микросхемах ПЗУ емкостью 2 Кбайта (Д62, Д63) и на двух регистрах К555ТМ9 (Д68 и Д69). Счетчик обеспечивает вертикальную развертку изображения, используя в качестве входного пересчетного импульса сигнал СГИ. Основные принципы работы ЦПА счетчика Y аналогичны вышеописанным принципам работы счетчика X и заключаются в числе разрядов обратной связи (девять) и в неизменном коэффициенте пересчета, равном 12. Кроме разрядов обратного свода счетчик Y формирует кадровый синхронизирующий импульс (КСИ), кадровый гасящий импульс (КГИ), 4 адресных сигнала для обращения к памяти экрана (МАО, MA1, MA2, DA7) и специальный сигнал для организации таймерных прерываний ЦП по IRQ.

Смена режима работы ДК, что выражается в изменении состояния сигналов ПА ПМ, А и В, также вызывает изменения в работе счетчика Y, как и в счетчике X.

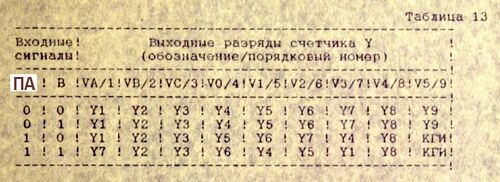

Но если в счетчике X меняется коэффициент пересчета, то в счетчике Y происходит изменение порядка старшинства разрядов (табл.13). Из таблицы видно, что при работе счетчика в режиме "Apple" (ПА=0) (ПМ=0) нумерация выходных разрядов счетчика Y соответствует расположению разрядов по старшинству (от младшего к старшему). Временные диаграммы работы счетчика представлены на рис.28,29.

4.5.1.3. Формирование адреса дисплейного контролера

Блок развертки изображения является основным устройством в дисплейном контроллере, отвечающим за обмен с оперативной памятью. Именно он формирует последовательность адресов для обращения в нужную область памяти экрана синхронно с разверткой изображения на экране. Адреса, формируемые в блоке развертки, передаются в оперативную память по ША ДК.

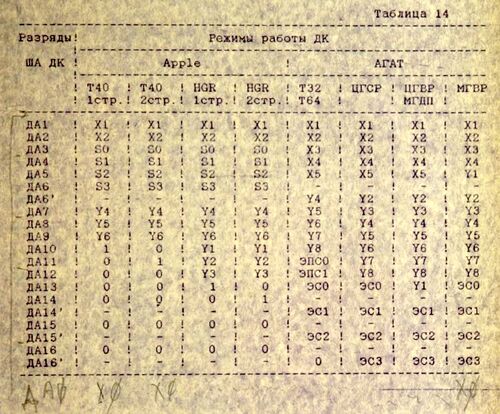

В табл. 14 приводится распределение разрядов адресной шины ДК по сигналам, вырабатываемым различными устройствами блока развертки изображения в зависимости от режимов работы ДК.

Нумерация разрядов ДА1–ДА16 совпадает с соответствующими номерами разрядов ША ЦП. Общее число разрядов ША ДК равно 20. Из них 8 разрядов являются взаимоисключающими: поступление сигналов ДА6, ДА14–ДА16 в оперативную память возможно только в режиме "Apple", а сигналов ДА6', ДА14'–ДА16' соответственно только в режиме "АГАТ". Для этого в МА оперативной памяти имеется два мультиплексора К555КП12 — Д28 и Д29, дублирующих передачу старших разрядов адреса непосредственно на микросхемы памяти.

Схема формирования адреса ДК показана на рис. 23. Большая часть разрядов (12) поступает на ША ДК с буферного регистра адресов (БРА), который состоит из двух частей: восемь разрядов передаются с помощью параллельного 8-и разрядного регистра К555ИР22 (Д74), а остальные 4 разряда еще и предварительно мультиплексируются. Для этого используется микросхема К555КП13 (Д75), которая представляет собой 4-х канальный мультиплексор с 2-х направлений на 1 с 4-х разрядным регистром на выходе. Основная задача БРА — не допустить изменений на ША ДК в течение времени приема адреса во внутренние регистры микросхем ОЗУ. Невыполнение этого условия приводит к пропаданию информации в отдельных частях оперативной памяти. Во избежание потери информации, БРА стробируется специальным сигналом, который в то время, пока адрес принимается во внутренние регистры микросхем ОЗУ, имеет уровень логического "0". Переключение стробирующего сигнала из "1" в "0" фиксирует в БРА кодовую комбинацию имеющуюся в этот момент на его входах, исключая дальнейший прием информации.

Из таблицы видно, что только у двух разрядов источник сохраняется неизменным во всех режимах, сохраняя при этом и свою суть. Это разряды ДА1 и ДА2, которые всегда поступают со счетчика X и определяются состоянием его младших разрядов X1 и X2. Остальные же разряды ША ДК (с 3 по 16), в зависимости от режима, формируются разными разрядами различных узлов блока развертки и других устройств ДК. Разряды ДА3–ДА6 формируются с помощью преобразователя кодов (ПК) из трех разрядов счетчика X (X3–X5), и двух разрядов счетчика Y (Y3 и Y4). В режиме "Apple" выходные разряды S0-S3 вырабатываются по следующим логическим формулам:

S0=X3+Y3+1, S1=X4+Y4+P0, S2=X5+Y3+P1, S3=X5+Y4+P2,

где P0, P1, P2 обозначают перенос из соответствующего разряда.

В режиме "АГАТ" выходные разряды ПК повторяют соответствующие разряды счетчиков X и Y, в соответствии с указаниями в табл.14.

4.5.1.4. Схема управления и синхронизации ДК

Работоспособность всех узлов по отдельности и дисплейного контроллера в целом зависит от корректного функционирования центрального управления дисплейного контроллера - схемы управления и синхронизации ДК (СУС). Если неправильная работа отдельных узлов ДК носит обычно локальный характер и вызывает нарушения лишь в том или ином процессе, не влияя на большинство остальных, то даже незначительные нарушения нормального функционирования СУС имеют, как правило, катастрофические последствия для работы ДК в целом.

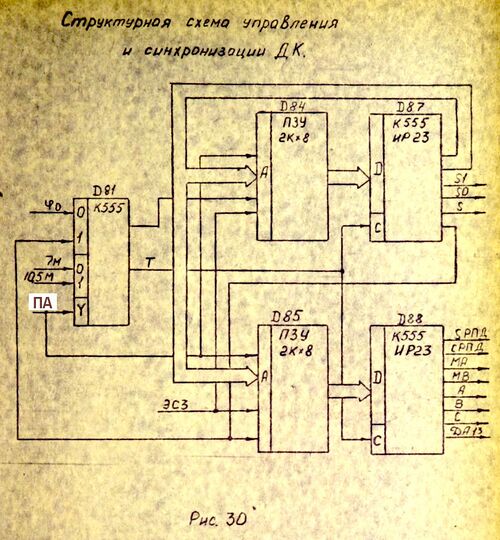

Основным отличием цифрового программируемого автомата СУС (рис. 30) является ограниченность числа разрядов обратной связи (от 4 до 5) при наличии большого числа входных (7) и выходных (11) разрядов. Такое построение СУС определяется жесткой потребностью всех процессов в течение ограниченного промежутка времени (не более 3.0 мкс).

Основными сигналами, определяющими все временные параметры выходных сигналов СУС, а также соотношением между ними, являются сигналы основных тактовых частот: в режиме "Apple" это частота 7 МГц, а в режиме "АГАТ" - частота 10,5 МГц.

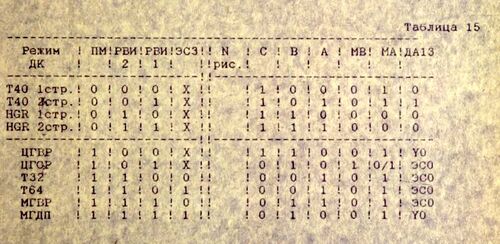

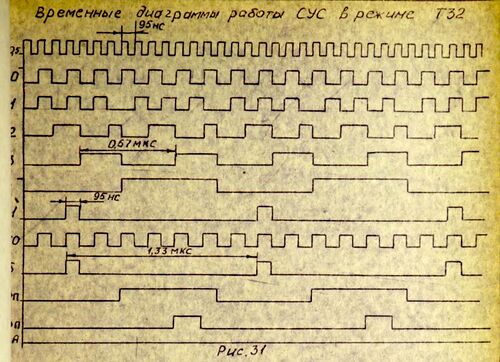

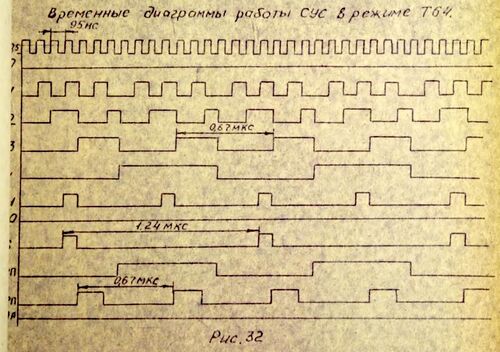

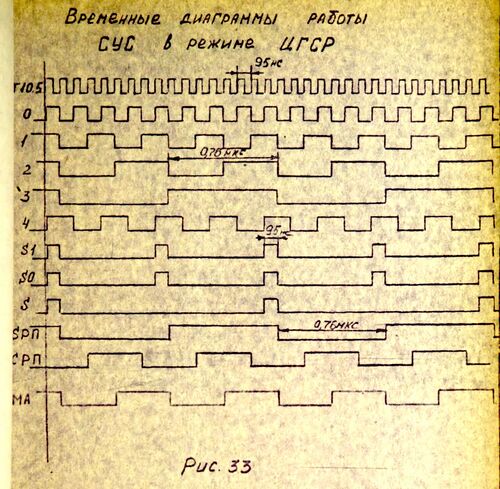

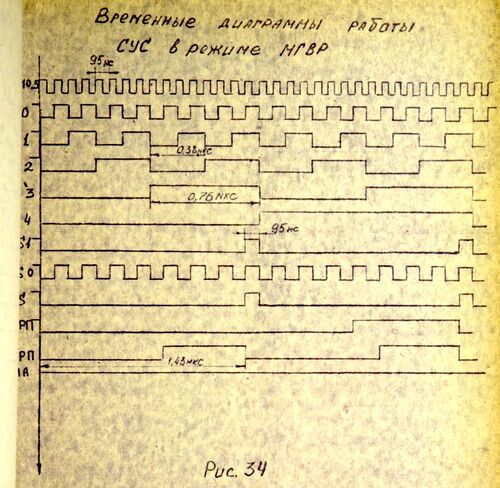

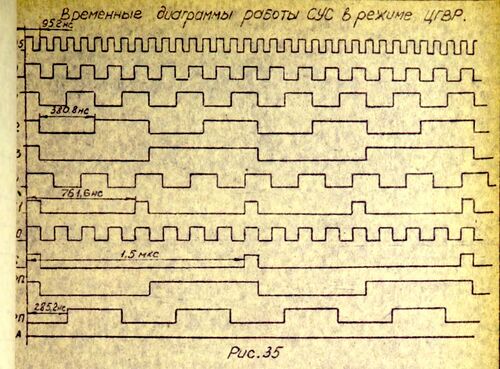

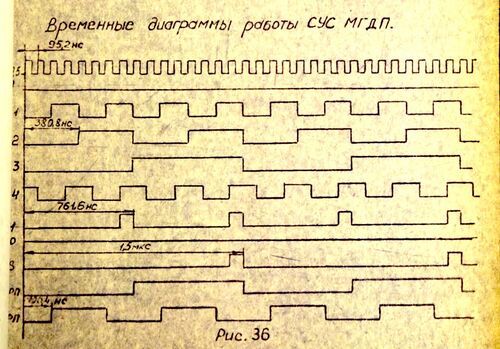

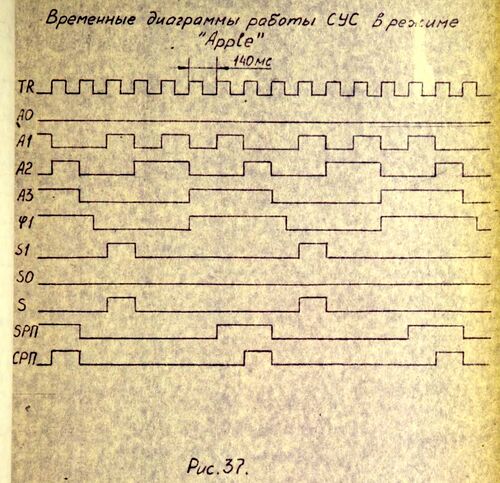

Зависимость выходных разрядов СУС MA, MB, A, B, C, ДА13 от входных РВИ1, РВИ2, ЭС0, ЭС3, V3, ПА приводится в табл.16. Временные диаграммы остальных сигналов, включая сигналы обратной связи показаны на рис.31-37.

Всего схема управления и синхронизации ДК вырабатывает 16 сигналов. Из них 5 сигналов являются сигналами обратной связи, обеспечивающими функционирование цифрового программируемого автомата СУС ДК по замкнутому циклу.

Сигналы S0 и S1 предназначены для управления регистром РПК и задают один из трех возможных режимов его работы:

- S0=0, S1=0 — регистр находится в режиме хранения,

- S0=1, S1=0 — режим сдвига информации в сторону младших разрядов по переднему фронту импульсов, поступающих на вход "С",

- S0=1, S1=1 — режим приема информации параллельным кодом с информационных входов также по переднему фронту импульсов "С".

Комбинация S0=0, S1=1 (сдвиг в сторону старших разрядов) в работе регистра не используется и ее появление вызывает нарушение формирования изображения.

Сигнал S используется для разрешения приема информации в регистре цвета.

Сигналы SРПД и СРПД предназначаются для управления регистром приема данных: по переднему фронту сигнала СРПД происходит либо прием информации с ШД ДК при наличии высокого уровня сигнала SРПД, либо сдвиг информации при наличии низкого уровня сигнала SРПД.

Сигналы управления выходным мультиплексором МА и МВ обеспечивают переключение каналов передачи информации в зависимости от режима работы ДК.