Ириша/Техническая информация

| Этот документ создан для Emuverse и распространяется на условиях лицензии CC-BY-SA-3.0. |

Процессор

Адресное пространство

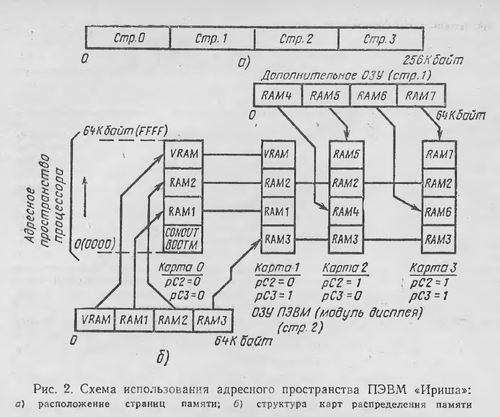

Всего доступно 4 карты распределения памяти. Полученные варианты (для стандартной прошивки ПЗУ блока управления памятью) приведены на рисунке.

После сброса устанавливается карта 0. При этом на нижние адреса подключается ПЗУ, а на верхние – нулевая подстраница памяти видеоконтроллера.

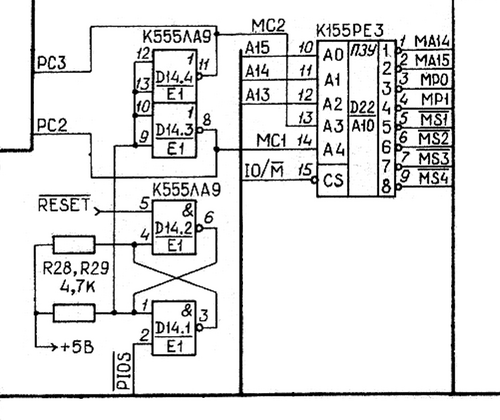

Полное адресное пространство платы процессора Ириши составляет 256 Кб, разбитое на 4 страницы по 64 Кб. Расширение адресных линий до 18 организовано с помощью двух дополнительных сигналов P0 и P1, которые выведены на шину. Эти линии управляются сигналами PC2 и PC3 регистра ВВ55 через специальное ПЗУ диспетчера памяти.

Адрес ПЗУ формируется из трех адресных линий процессора A13, A14, A15, что позволяет управлять памятью подстраницами по 8Кб, и выходами ППА PC2 и PC3. Выходы подключаются следующим образом: MA14, MA15, MP0, MP1 — на шину, MS3, MS4 — на ПЗУ BIOS (8+8 Кб), MS1, MS2 в стандартной прошивке не используются.

Сигналы MC1 и MC2 формируются схемой монтажного ИЛИ элементами с открытым коллектором. Сразу после сброса они устанавливаются в 0 специальным триггером, что выбирает карту памяти 0. После обращения к ППА триггер устанавливается в 1 и эти линии начинают контролироваться выходами ВВ55.

ОЗУ всегда находится на дополнительных платах, которые должны обрабатывать в том числе дополнительные сигналы P0 и P1. Стандартная прошивка ПЗУ диспетчера памяти подразумевает следующую конфигурацию:

- Страница 0 — ПЗУ BIOS на плате процессора. До 2-х ИС 2–8 Кб + 2–8 Кб.

- Страница 1 — расширение ОЗУ. Реализуется либо отдельной платой расширения, либо контроллером НГМД.

- Страница 2 — ОЗУ на плате видеоконтроллера. Обычно используется как основное ОЗУ компьютера.

- Страница 3 — не используется в стандартной прошивке.

Каждая страница памяти разбита на 4 подстраницы по 16 Кб. Порядок подключения подстраниц в адресное пространство процессора также задается прошивкой ПЗУ диспетчера памяти через преобразование A14, A15 — MA14, MA15.

ПЗУ BIOS на плате процессора устанавливается в две панельки, адресное пространство каждой — 8 Кб. Если устанавливаются ИС меньшей ёмкости, пространство до 8 Кб не используется.

Порты ввода-вывода

| Адрес | Вид операции | Назначение | Примечание |

|---|---|---|---|

| 00H … 03H | — | Резерв | |

| 05H | R | Регистр данных клавиатуры (дубль) | |

| 07H | R/W | Регистр управления/статуса последовательного интерфейса | |

| 0BH | W | Регистр управления | |

| 0FH | R/W | Дублирует 0DH | |

| 13H | W | Регистр управления ППА | |

| 14H | R/W | Порт расширения ROM. Чтение – получение следующего байта. Запись – сброс счетчика. | |

| 15H … 1BH | — | Резерв | |

| DAH | W | Регистр выбора видеостраницы |

Видеоконтроллер

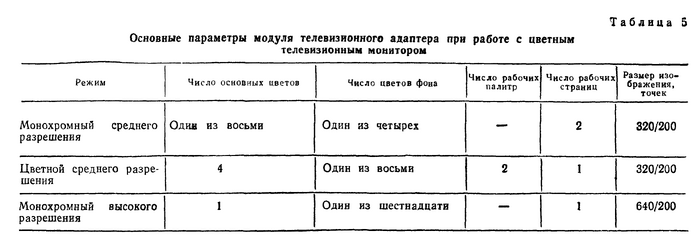

Видеоконтроллер поддерживает только графические режимы. Текстовые режимы эмулируются программным обеспечением.

Объем памяти, необходимой для режима 1 – 8000 байт (страницы выровнены по границе 8 Кб), для режимов 2 и 3 – 16000 байт.

Регистры управления видеоконтроллером

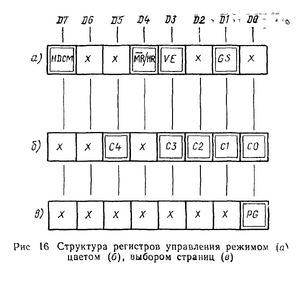

- D8H – регистр управления режимом.

- 0AH, 1AH – режим 1.

- 8AH – режим 2.

- 9AH – режим 3.

- x8H, x2H, x0H – гашение изображения.

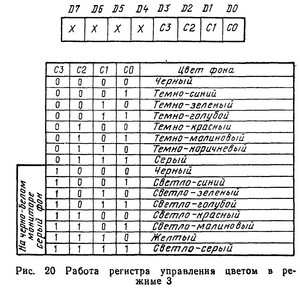

- D9H – регистр управления цветом.

- DAH – регистр выбора рабочих страниц.

Монохромные режимы

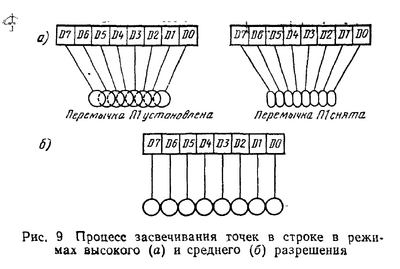

В монохромном режиме среднего разрешения каждый бит отвечает за засветку одной точки на экране.

В режиме высокого разрешения, в зависимости от установки перемычки П1, контроллер может работать аналогично режиму среднего разрешения (П1 снята), тогда в строке выводится 640 независимых точек, либо, за счет снижения разрешения (П1 установлена), яркость соседних точек усредняется (используется для бытовых телевизоров с узкой полосой пропускания).

В режиме 1 на экране отображается одна из двух экранных страниц 8000 байт (адрес начала страниц выровнен но границе 8 Кб), в левом верхнем углу находится первый байт изображения. Старший бит соответствует первой точке.

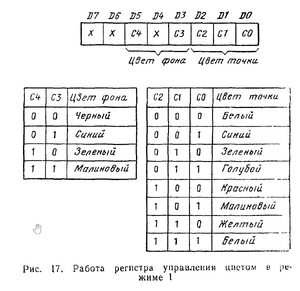

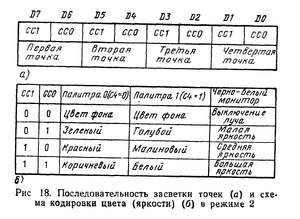

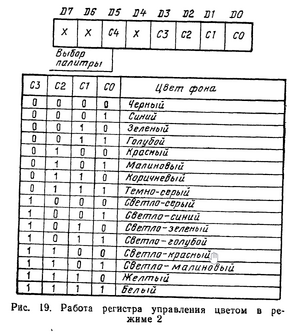

Структура регистра управления цветом показана на рисунке:

Цветной режим

В режиме 2 каждая точка может быть окрашена одним из трёх цветов из выбранной палитры (доступно 2):

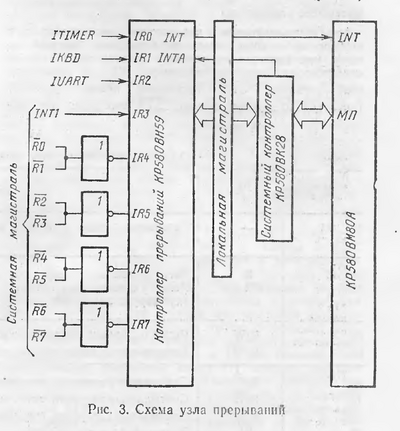

Контроллер прерываний

Наивысший приоритет имеет прерывание ITIMER от таймера ВИ53. IKBD и IUART отвечают за прием данных с клавиатура и по локальной сети.

ППА

ППА построен на основе КР580ВВ55. Порты используются следующим образом:

- Порт A: Ввод/вывод данных.

- Порт B: Только ввод.

- Порт C: Только вывод.

Выходы порта C используются для управления работой внутренних схем модуля процессора. На входе порта B установлен мультиплексор К555КП13. Управление мультиплексором осуществляется выходом PC7.

| Сигнал | Назначение | |

|---|---|---|

| PC7 = 0 | PC7 = 1 | |

| PA7 | Вход-выход ПИ 7 | Выход программного канала последовательного интерфейса |

| PB7 | Вход анализа типа дополнительной платы EX2 | Анализ готовности клавиатуры: «1» — код принят |

| PC7 | Выбор функций портов А и В | |

Клавиатура

Клавиатура записывает код нажатой клавиши в регистр К589ИР12, после чего устанавливается сигнал прерывания IKBD. После чтения регистра сигнал IKBD сбрасывается. Также, наличие кода символа в регистре можно контролировать с помощью бита PB7 ППА.

Последовательный интерфейс

Последовательный интерфейс предназначен для обмена информацией с внешними устройствами, в том числе бытовым магнитофоном. Последовательный интерфейс имеет два канала:

- Канал 1 построен на базе КР580ВВ51.

- Канал 2 реализуется программно: вывод с помощью манипуляции выходом PA7 ППА, ввод с помощью анализа состояния PB3 ППА.

Скорость обмена в Канале 1 задается с помощью программирования режимов КР580ВВ51 и канала 0 КР580ВИ53, который используется как делитель базовой частоты Ф2TTL, равной 1,7777 МГц.

Канал 2 используется для обмена с бытовым магнитофоном и поддерживает скорости до 1200 бод. Метод и формат записи соответствует стандарту MSX.

Для полноценной работы магнитофон должен поддерживать вход отключения двигателя. Программа работы с магнитофоном использует бит PA7 ППА для вывода информации, выход DTR ВВ51 для управления двигателем и вход DSR для чтения данных. Полученные байты должны читаться из регистра данных ВВ51.

Параллельный интерфейс (ПИ)

Параллельный интерфейс предназначен для подключения принтеров и других периферийных устройств. Интерфейс реализует следующие сигналы:

- P0 … P7 — двунаправленные. Подключены к каналу A ППА.

- S01, S02 — выходы, PC0 и PC1 ППА.

- S11 … S16 — входы, подключены к каналу B ППА.

В зависимости от типа подключенного устройства, конкретное назначение сигналов определяется схемой его подключения и программным обеспечением.

Таймер

В качестве таймера используется БИС К580ВИ53.

Канал 0 используется как делитель частоты для последовательного интерфейса.

Канал 1 используется для формирования временных интервалов. Опорная частота формируется делением сигнала Ф2TTL на 256, что позволяет формировать временные интервалы от 432 мкс до 9,4 сек с дискретностью 144 мкс. Выходной сигнал канала поступает на контроллер прерываний и имеет наивысший приоритет.

Канал 2 используется для генерации звука.

Синтезатор звука

Синтезатор звука состоит из двух независимых каналов:

- Канал 1 использует второй канал К580ВИ53.

- Канал 2 предназначен для синтеза шумовых сигналов и управляется битом PA4 ППА.

Разрешение работы обоих каналов управляется выводом PC5 ППА (активный – низкий).

Расширение ROM

Дополнительное ПЗУ подключается к специальному разъему на плате процессора. Размер может достигать 64 Кб. Доступ к содержимому производится через порт 14H – чтение передает следующий байт, запись сбрасывает счётчик.

Наличие дополнительно ПЗУ определяется, если при чтении 65536 байт из порта 14H, хотя бы один полученный байт будет отличаться от FFH.

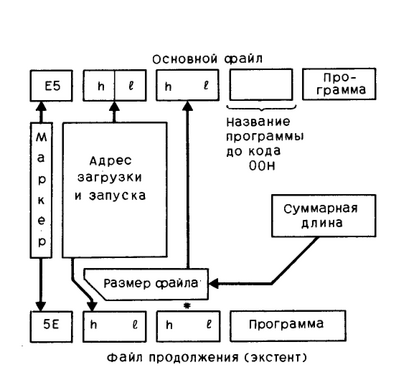

Каждый файл содержит заголовок, в котором указан адрес загрузки, длина и название. Файлы идут последовательно, выравнивания по адресам нет. Файл может состоять из основного блока и нескольких экстентов. Формат записи файла в ПЗУ следующий: