588ВУ2: различия между версиями

Nzeemin (обсуждение | вклад) Нет описания правки |

Nzeemin (обсуждение | вклад) Нет описания правки |

||

| Строка 9: | Строка 9: | ||

! Кодировка !! Применение | ! Кодировка !! Применение | ||

|- | |- | ||

| 0001 | | 0001..0004 || Управление арифметико-логическим устройством (АЛУ) [[588ВС2]]. Четыре микросхемы 0001..0004 соединяются параллельно (по выходам) и выдают информацию в АЛУ; 12-разрядный код является собственно микрокомандой для АУ; разряд 12 используется в качестве строба микрокоманды. | ||

|- | |- | ||

| 0005 || | | 0005 || Разрядами 0..6 вырабатывает сигналы разрешения прерывания, разряды 7..12 управляют системным контроллером [[588ВГ1]] | ||

|- | |- | ||

| 0006 || Управление арифметическим умножителем 16×16 [[588ВР2]] для реализации команд расширенной арифметики (MUL, DIV, ASH, ASHC) | | 0006 || Управление арифметическим умножителем 16×16 [[588ВР2]] для реализации команд расширенной арифметики (MUL, DIV, ASH, ASHC) | ||

|- | |- | ||

| 0007 || | | 0007 || Разрядами 0..6 вырабатывает сигналы разрешения прерывания, разряды 7..12 управляют системным контроллером 588ВГ1 | ||

|} | |} | ||

Версия от 00:34, 11 октября 2022

| Этот документ создан для Emuverse и распространяется на условиях лицензии CC-BY-SA-3.0. |

К588ВУ2 (КР588ВУ2, КА588ВУ2) — микросхема управляющей памяти микрокоманд из микропроцессорного комплекта 588.

Всего есть 7 типов микросхем 588ВУ2: 0001..0007, вместе они реализуют систему команд компьютера «Электроника-60» (ОСТ 11 305.909-82), за исключением команд FIS (операций с плавающей запятой).

| Кодировка | Применение |

|---|---|

| 0001..0004 | Управление арифметико-логическим устройством (АЛУ) 588ВС2. Четыре микросхемы 0001..0004 соединяются параллельно (по выходам) и выдают информацию в АЛУ; 12-разрядный код является собственно микрокомандой для АУ; разряд 12 используется в качестве строба микрокоманды. |

| 0005 | Разрядами 0..6 вырабатывает сигналы разрешения прерывания, разряды 7..12 управляют системным контроллером 588ВГ1 |

| 0006 | Управление арифметическим умножителем 16×16 588ВР2 для реализации команд расширенной арифметики (MUL, DIV, ASH, ASHC) |

| 0007 | Разрядами 0..6 вырабатывает сигналы разрешения прерывания, разряды 7..12 управляют системным контроллером 588ВГ1 |

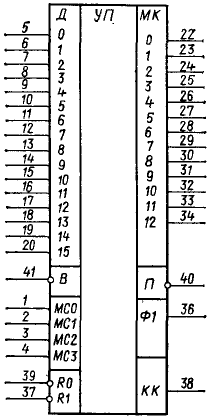

Назначение выводов

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1..4 | Магистраль состояния | 0 | МС0..МС3 | Вход |

| 5..20 | Шина команд | 0 | Д0..Д15 | Вход |

| 21 | Общий | — | GND | — |

| 22..34 | Магистраль микрокоманд | 0 | МК0..МК12 | Вход |

| 35 | Не используется | — | — | — |

| 36 | Завершение выполнения микрокоманды | — | Ф1 | Вход |

| 37 | Установка | 1 | R1 | Вход |

| 38 | Конец команды | — | КК | Вход-выход |

| 39 | Установка | 0 | R0 | Вход |

| 40 | Команда принята | — | П | Выход |

| 41 | Команда выдана | — | В | Вход |

| 42 | Напряжение питания | — | Ucc | — |

Система команд

Система команд и распределение команд по кодировкам микросхем 588ВУ2, согласно Немига/ТО#Приложение_1.

───────────────────┬───────────────┬─────────────────────┬─────────

Код команды │ Признаки │ │ Номер

──────────┬────────┼───┬───┬───┬───┤ Содержание команды │кодировки

Мнемоника │8-ричный│ N │ Z │ V │ C │ │

──────────┼────────┼───┼───┼───┼───┼─────────────────────┼─────────

CLR (A) │*050DD │ 0 │ 1 │ 0 │ 0 │Очистка │ 0001

COM (A) │*051DD │ + │ + │ 0 │ 1 │Инвертирование │ 0001

INC (A) │*052DD │ + │ + │ + │ - │Инкрементация │ 0001

DEC (A) │*053DD │ + │ + │ + │ - │Декрементация │ 0001

NEG (A) │*054DD │ + │ + │ + │ + │Дополнение │ 0001

ADC (A) │*055DD │ + │ + │ + │ + │Сложение с переносом │ 0001

SEC (A) │*056DD │ + │ + │ + │ + │Вычитание переноса │ 0001

TST (A) │*057DD │ + │ + │ 0 │ 0 │Проверка │ 0001

ROR (A) │*060DD │ + │ + │ + │ + │Сдвиг цикл.правый │ 0001

ROL (A) │*061DD │ + │ + │ + │ + │Сдвиг цикл.левый │ 0001

ASR (A) │*062DD │ + │ + │ + │ + │Сдвиг арифм.правый │ 0001

ASL (A) │*063DD │ + │ + │ + │ + │Сдвиг арифм.левый │ 0001

MOV (A,B) │*1SSDD │ + │ + │ 0 │ - │Пересылка │ 0001

CMP (A,B) │*2SSDD │ + │ + │ + │ + │Сравнение │ 0001

BIT (A,B) │*3SSDD │ + │ + │ 0 │ - │Проверка разрядов │ 0001

BIC (A,B) │*4SSDD │ + │ + │ 0 │ - │Очистка разрядов │ 0001

BIS (A,B) │*5SSDD │ + │ + │ 0 │ - │Логическое "ИЛИ" │ 0001

ADD (A,B) │06SSDD │ + │ + │ + │ + │Сложение │ 0001

SUB (A,B) │16SSDD │ + │ + │ + │ + │Вычитание │ 0001

──────────┼────────┼───┼───┼───┼───┼─────────────────────┼─────────

NOP │000240 │ │ │ │ │Нет операции │ 0002

CLC │000241 │ - │ - │ - │ 0 │Очистка "С" │ 0002

CLV │000242 │ - │ - │ 0 │ - │Очистка "V" │ 0002

CLZ │000244 │ - │ 0 │ - │ - │Очистка "Z" │ 0002

CLN │000250 │ 0 │ - │ - │ - │Очистка "N" │ 0002

SEC │000261 │ - │ - │ - │ 1 │Установка "С" │ 0002

SEV │000262 │ - │ - │ 1 │ - │Установка "V" │ 0002

SEZ │000264 │ - │ 1 │ - │ - │Установка "Z" │ 0002

SEN │000270 │ 1 │ - │ - │ - │Установка "N" │ 0002

SCC │000277 │ 1 │ 1 │ 1 │ 1 │Установка "С", "V" │ 0002

│ │ │ │ │ │ "Z", "N" │

CCC │000257 │ 0 │ 0 │ 0 │ 0 │Очистка "С", "V" │ 0002

│ │ │ │ │ │ "Z", "N" │

SWAB │0003DD │ + │ + │ 0 │ 0 │Перестановка байтов │ 0002

MARK │0064NN │ - │ - │ - │ - │Восстановление указа-│ 0002

│ │ │ │ │ │теля стека │

XOR (R,A) │074RDD │ + │ + │ 0 │ - │Исключающее "ИЛИ" │ 0002

BR (A) │0004XXX │ │Ветвление безусловное│ 0002

BNE (A) │0010XXX │ Z=0 │Ветвление, если =0 │ 0002

BEQ (A) │0014XXX │ Z=1 │Ветвление, если =0 │ 0002

BGE (A) │0020XXX │ NOV=0 │Ветвление, если >0 │ 0002

BLT (A) │0024XXX │ NOV=1 │Ветвление, если <0 │ 0002

BGT (A) │0030XXX │ ZV(NOV)?0 │Ветвление, если >0 │ 0002

BLE (A) │0034XXX │ ZV(NOV)=1 │Ветвление, если <0 │ 0002

SOB (A) │077RNN │ Z=0 │Вычитание единицы, │ 0002

│ │ │если результат =0 │ 0002

BLR (A) │1000XXX │ N=0 │Ветвление, если + │ 0002

BMI (A) │1004XXX │ N=1 │Ветвление, если - │ 0002

BHI (A) │1010XXX │ ZVC=0 │Ветвление, если > │ 0002

BLOS (A) │1014XXX │ ZVC=1 │Ветвление, если < │ 0002

BVC (A) │1020XXX │ V=0 │Ветвление, если нет │ 0002

│ │ │переполнения │ 0002

BVS (A) │1024XXX │ V=1 │Ветвление, если │ 0002

│ │ │переполнение │ 0002

BHIS (A) │1030XXX │ C=0 │Ветвление, если нет │ 0002

│ │ │переноса │

BLO (A) │1034XXX │ C=1 │Ветвление, если │ 0002

│ │ │перенос │

SXT (A) │0067DD │ - │ + │ 0 │ - │Расширение знака │ 0002

MTPS (A) │1064SS │ + │ + │ + │ + │Запись ССП │ 0002

MFPS (A) │1067DD │ - │ + │ 0 │ - │Чтение ССП │ 0002

──────────┼────────┼───┴───┴───┴───┼─────────────────────┼─────────

HALT │000000 │ │Останов │ 0004

WAIT │000001 │ │Ожидание │ 0004

RTI │000002 │ │Возврат из прерыва- │ 0004

│ │ │ния │

BPT │000003 │ │Прерыв.для отладки │ 0004

IOT │000004 │ │Прерыв.для ВВ/ВЫВ │ 0004

RESET │000005 │ │Сброс │ 0004

RTT │000006 │ │Возврат из прерыва- │ 0004

│ │ │ния │

JMP (A) │0001DD │ │Безусловный переход │ 0004

RTS (R) │00020R │ │Возврат из подпрогр. │ 0004

JSR (R,A) │0004RDD │ │Переход к подпрограм-│ 0004

│ │ │ме │

EMT │104000- │ │Командное прерывание │ 0004

│104377 │ │ │

TRAP │104400- │ │Командное прерывание │ 0004

│104777 │ │ │

──────────┼────────┼───┬───┬───┬───┼─────────────────────┼─────────

MUL (R,A) │070RSS │ + │ + │ 0 │ + │Умножение │ 0006

DIV (R,A) │071RSS │ + │ + │ + │ + │Деление │ 0006

ASH (R,A) │072RSS │ + │ + │ + │ + │Многоразрядный сдвиг │ 0006

ASHC (R,A)│073RSS │ + │ + │ + │ + │Сдвиг комбинированный│ 0006

──────────┴────────┴───┴───┴───┴───┴─────────────────────┴─────────

П р и м е ч а н и я:

1. R - восьмеричный код РОН (0-7);

SS - поле адресации операнда источника;

DD - поле адресации операнда приемника;

* - операция производится над байтом, если * = 1

над словом, если * = 0;

XXX - смещение (8 разрядов);

NN - смещение (6 разрядов).

2. В графе "признаки" указаны значения признаков N,Z и C,V

слова состояния процессора, которые устанавливаются после выполнения

процессором каждой команды. Знак "+" означает, что данный разряд ССП

будет установлен в "0" или "1" в зависимости от результата выполне-

ния команды. Знак "-" означает, что команда не оказывает воздействия

на данный разряд ССП.

3. B графе 8 указан номер кодировки микросхемы КР588ВУ2‚ отве-

чающей за выполнение соответствующей команды.