Немига/ТО: различия между версиями

< Немига

Nzeemin (обсуждение | вклад) |

Nzeemin (обсуждение | вклад) |

||

| Строка 468: | Строка 468: | ||

=== 6.1. Модуль процессора === | === 6.1. Модуль процессора === | ||

<pre> | <pre> | ||

Функционально модель процессора 6. | Функционально модель процессора 6.120.107 ЭЗ состоит: | ||

процессорное ядро; | процессорное ядро; | ||

| Строка 479: | Строка 479: | ||

мент D1 , выполняющий функции арифметико-логического устройства (АЛУ). | мент D1 , выполняющий функции арифметико-логического устройства (АЛУ). | ||

пять БИС управляющей памяти D2...D6, системный контроллер D18, два | пять БИС управляющей памяти D2...D6, системный контроллер D18, два | ||

магистральных приемопередатчика (МПП)D21, D24. | магистральных приемопередатчика (МПП) D21, D24. | ||

АЛУ предназначено для приема, хранения, обработки I6-разрядных | АЛУ предназначено для приема, хранения, обработки I6-разрядных | ||

чисел. Преобразование данных выполняется в соответствии c I2-разряд- | чисел. Преобразование данных выполняется в соответствии c I2-разряд- | ||

| Строка 511: | Строка 511: | ||

Она предназначена для управления работой процессорного ядра и | Она предназначена для управления работой процессорного ядра и | ||

сочетает в себе функции БИС блока микропрограммного управления и ПЗУ | сочетает в себе функции БИС блока микропрограммного управления и ПЗУ | ||

микрокоманд. Микросхемы с номерами кодировок | микрокоманд. Микросхемы с номерами кодировок 0001, 0002, 0004 пред- | ||

назначены для управления АЛУ, БИС УП с кодировкой 0007 - для управ- | назначены для управления АЛУ, БИС УП с кодировкой 0007 - для управ- | ||

ления системным контроллером D18, БИС с кодировкой 0006 предназ- | ления системным контроллером D18, БИС с кодировкой 0006 предназ- | ||

| Строка 522: | Строка 522: | ||

признаков. Приняв информацию, микросхема устанавливает уровень ло- | признаков. Приняв информацию, микросхема устанавливает уровень ло- | ||

гического нуля на выводе П и активный низкий уровень на выводе КК. | гического нуля на выводе П и активный низкий уровень на выводе КК. | ||

При снятии сигнала | При снятии сигнала "ЛОГИЧЕСКИЙ НОЛЬ" на выводе В снимается сигнал | ||

и на выводе П. | и на выводе П. | ||

По отрицательному фронту сигнала ФI прекращается выдача микро- | По отрицательному фронту сигнала ФI прекращается выдача микро- | ||

команды и происходит "ПОДБРОС" в высокий потенциал состояния выво- | команды и происходит "ПОДБРОС" в высокий потенциал состояния выво- | ||

дов МК (0- | дов МК (0-12). Если к этому времени сформирована следующая микроко- | ||

манда, то происходит ее запись в регистры с последующей выдачей. | манда, то происходит ее запись в регистры с последующей выдачей. | ||

Системный контроллер предназначен для связи внутреннего интер- | Системный контроллер предназначен для связи внутреннего интер- | ||

| Строка 546: | Строка 546: | ||

го высокого потенциала, установлен в режим выхода на системное ПЗУ | го высокого потенциала, установлен в режим выхода на системное ПЗУ | ||

через адрес-вектор 24. | через адрес-вектор 24. | ||

Выходы | Выходы C1, C2 управляют направлением передачи данных через ма- | ||

гистральные приемопередатчики. | гистральные приемопередатчики. | ||

Системный контроллер D18 через входы Р, Т принимает информа- | Системный контроллер D18 через входы Р, Т принимает информа- | ||

| Строка 552: | Строка 552: | ||

сора для обработки прерываний. | сора для обработки прерываний. | ||

При нажатии на кнопку "ПУСК" на передней панели на выводах | При нажатии на кнопку "ПУСК" на передней панели на выводах | ||

8, | 8, 12 микросхемы D40 формируются сигналы начального пуска, которые | ||

устанавливают микросхемы управляющей памяти и системного контролле- | устанавливают микросхемы управляющей памяти и системного контролле- | ||

ра в начальное положение и запускают микропрограмму начального пус- | ра в начальное положение и запускают микропрограмму начального пус- | ||

ка. Данная микропрограмма формирует обращение процессорного ядра к | ка. Данная микропрограмма формирует обращение процессорного ядра к | ||

ячейкам памяти с адресами | ячейкам памяти с адресами 160006 и 160010, где читает и устанавли- | ||

вает программный счетчик и слово состояния процессора соответственно. | вает программный счетчик и слово состояния процессора соответственно. | ||

В адресном пространстве процессора с адреса | В адресном пространстве процессора с адреса 160000 по 167776 | ||

занимает системное ПЗУ. Адресное пространство процессора | занимает системное ПЗУ. Адресное пространство процессора 140000-157776 | ||

зарезервировано под дополнительные 4к слов системного ПЗУ. | зарезервировано под дополнительные 4к слов системного ПЗУ. | ||

При обращении к области памяти обязательного системного ПЗУ | При обращении к области памяти обязательного системного ПЗУ | ||

контроллер запоминающего устройства D15 вырабатывает сигнал ВКО, | контроллер запоминающего устройства D15 вырабатывает сигнал ВКО, | ||

который разрешает выборку данных из ПЗУ D9, D10 . Адрес, по которо- | который разрешает выборку данных из ПЗУ D9, D10. Адрес, по которо- | ||

му ведется обращение, фиксируется в регистре D7, D8. Сигнал ОТВ фор- | му ведется обращение, фиксируется в регистре D7, D8. Сигнал ОТВ фор- | ||

мирует микросхема D15 с задержкой относительно сигнала ОБМ, опреде- | мирует микросхема D15 с задержкой относительно сигнала ОБМ, опреде- | ||

| Строка 597: | Строка 597: | ||

Последним читается регистр состояния. Время умножения < 2 мкс отсчи- | Последним читается регистр состояния. Время умножения < 2 мкс отсчи- | ||

тывается с загрузки второго операнда до чтения первого слова резуль- | тывается с загрузки второго операнда до чтения первого слова резуль- | ||

тата. При этом используются адреса | тата. При этом используются адреса 170000, 170002, 170004, которые | ||

дешифрируются селектором каналов D19. | дешифрируются селектором каналов D19. | ||

HALT-монитор является процедурой, предназначенной для управле- | HALT-монитор является процедурой, предназначенной для управле- | ||

| Строка 606: | Строка 606: | ||

двумя способами: команда HALT или запрос по линии прерывания ОСТ. | двумя способами: команда HALT или запрос по линии прерывания ОСТ. | ||

Для диспетчеризации запросов предусмотрен регистр запросов с адресом | Для диспетчеризации запросов предусмотрен регистр запросов с адресом | ||

170007. Младший байт этого регистра 170006 является регистром данных | |||

клавиатуры. Запросы обрабатываются согласно их приоритету. По окон- | клавиатуры. Запросы обрабатываются согласно их приоритету. По окон- | ||

чании обработки содержимое регистра сбрасывается. Случаи возникнове- | чании обработки содержимое регистра сбрасывается. Случаи возникнове- | ||

| Строка 612: | Строка 612: | ||

появление канального сигнала СБРОС; | появление канального сигнала СБРОС; | ||

запрос на обслуживание локальной сети; | запрос на обслуживание локальной сети; | ||

обращение к группе ячеек | обращение к группе ячеек 177560-177566, соответствующих ре- | ||

гистрам системной консоли; | гистрам системной консоли; | ||

нажатие клавиши на клавиатуре. | нажатие клавиши на клавиатуре. | ||

Выполнение команды | Выполнение команды HALT‚ также как и ввод с клавиатуры кода 0 | ||

переводит процессор в режим пультового терминала. | переводит процессор в режим пультового терминала. | ||

Использование для входа в HALT-монитор прерывания HALT объяс- | Использование для входа в HALT-монитор прерывания HALT объяс- | ||

няется тем, что это единственное прерывание, адрес вектора которого | няется тем, что это единственное прерывание, адрес вектора которого | ||

лежит в адресном пространстве системного ПЗУ. Для своих нужд HALT- | лежит в адресном пространстве системного ПЗУ. Для своих нужд HALT- | ||

монитор использует область памяти | монитор использует область памяти 177600-177776, доступ к которой | ||

разрешается сигналом подтверждения прерывания HALT. Этим достигает- | разрешается сигналом подтверждения прерывания HALT. Этим достигает- | ||

ся полная "прозрачность" процедур HALT-монитора. | ся полная "прозрачность" процедур HALT-монитора. | ||

| Строка 635: | Строка 635: | ||

высшим приоритетом, после чего содержимое регистра фиксации очища- | высшим приоритетом, после чего содержимое регистра фиксации очища- | ||

ется. Схема формирования сигнала по линии ОСТ привязывает прерыва- | ется. Схема формирования сигнала по линии ОСТ привязывает прерыва- | ||

ние к сигналу КВЗ (вывод | ние к сигналу КВЗ (вывод 11 D18, ввод команды), исключая этим вло- | ||

женные прерывания ОСТ. | женные прерывания ОСТ. | ||

</pre> | </pre> | ||

Версия от 18:19, 7 февраля 2017

КОМПЛЕКС ВЫЧИСЛИТЕЛЬНЫЙ "НЕМИГА"

КОМПЬЮТЕРЫ ПЕРСОНАЛЬНЫЕ ПК 588, ПК 588-01

ТЕХНИЧЕСКОЕ ОПИСАНИЕ И ИНСТРУКЦИЯ ПО ЭКСПЛУАТАЦИИ

1.700.005 ТО

Альбом 1

1. ВВЕДЕНИЕ

...

2. НАЗНАЧЕНИЕ

...

3. ТЕХНИЧЕСКИЕ ДАННЫЕ

...

4. СОСТАВ ПЕРСОНАЛЬНОГО КОМПЬЮТЕРА

...

5. УСТРОЙСТВО И РАБОТА ПК

Основным устройством ПК является центральный процессор, который

управляет распределением времени использования канала внешними устройст-

вами и выполняет все необходимые арифметико-логические операции для

обработки информации. Он содержит I6 быстродействующих регистров общего

назначения (РОН), 8 из них (R0...R7) программно доступны, а 8 других

используются как служебные регистры при выполнении микрокоманд.

Центральный процессор выполняет одноадресные команды, двухадресные

команды, команды расширенной арифметики, может обрабатывать как I6-раз-

рядные слова, та к и 8-разрядные байты. Возможность использования 8

методов адресации позволяет вести высокоэффективную обработку данных,

хранимых в любой ячейке памяти или в регистре.

5.1. Регистры общего назначения

Бис АЛУ содержит 16-разрядные РОН, способные выполнять различ- ные функции. Они могут служить в качестве накопительных регистров, индексных регистров, регистров автоинкрементной и автодекрементной адресации и т. д. РОН используются для выборки операндов и записи результатов при выполнении арифметико-логических операций, аналогич- но ячейкам памяти и регистрам внешних устройств. Два из 8 программно- доступных регистров общего назначения R6, R7 имеют, кроме того, спе- циальное назначение. Регистр R6 используется как указатель стека (УС) и содержит адрес последней заполненной ячейки стека. Регистр R7 слу- жит счетчиком команд (СК) и содержит адрес очередной выполняемой ко- манды. Операции по выполнению команд с регистровым методом адресации являются внутренними по отношению к микропроцессору и не требуют вы- полнения циклов обращения к каналу (за исключением цикла выборки ко- манды). Обмен же данными с памятью и внешними устройствами выполня- естся через канал и занимает более длительное время. Таким образом, использование РОН для хранения операндов при процессорных операциях повышает быстродействие ПК.

5.2. Слово состояния процессора

Слово состояния процессора (ССП) содержит информацию о текущем

состоянии процессора. Это информация о текущем приоритете процессо-

ра, значения кодов условий ветвления, зависящем от результата выпол-

нения команды в состоянии Т-разряда, используемого при отладке про-

граммы. На рис.2 показан формат ССП. Разряд приоритета процессора

(7- й разряд ССП) может находиться в состоянии "О" или "1". В по-

следнем случае внешние устройства не могут вызвать прерывание теку-

щей программы.

Коды условий ветвления содержат информацию о результате послед-

ней выполненной процессором команды. Процедуру установки их в соот-

ветстсвующее состояние выполняют все арифметические и логические од-

ноадресные и двухадресные команды.

Установка отдельных разрядов этих кодов выполняется в следующих

случаях:

Z=1, если результат равен 0;

N=1, если результат < 0;

С=1, если в результате выполнения команды произошел перенос

из самого старшего разряда или, если при сдвиге вправо

или влево из самого младшего или самого старшего разря-

да была выдвинута единица;

V=1, если в результате выполнения команды произошло арифмети-

ческое переполнение.

Если T=1, то произойдет прерывание программы с вектором 14.

15 8 7 6 5 4 3 2 1 0

┌─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─--┐

│ Р Т N Z V C │

└─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─--┘

│ │ │ │ │ │

Разряд приоритета процессора ----┘ │ │ │ │ │

│ │ │ │ │

Прерывание по Т-разряду -----------------┘ │ │ │ │

│ │ │ │

Отрицательный результат ---------------------┘ │ │ │

│ │ │

Нулевой результат ------------------------ ┘ │ │

│ │

Арифметическое переполнение ---------------------------┘ │

│

Перенос старшего байта -------------------------------┘

Рис.2. Формат слова состояния процессора

5.3. Система команд

В центральном процессоре ПК используются три типа команд: без-

адресные, одноадресные и двухадресные. В безадресных командах код

команды содержит только код операции. Формат одноадресных команд

имеет следующий вид:

--------------------------------------------------

| КОП | Метод | РОН |

| | адресации | |

--------------------------------------------------

15 6 5 3 2 0

Формат одноадресных команд

Формат двухадресных команд имеет следующий вид:

-------------------------------------------------

| КОП | Метод | РОН | Метод | РОН |

| | адресации | | адресации | |

-------------------------------------------------

15 12 11 9 8 6 5 3 2 0

------------------ ...................

Поле адресации операнда Поле адресации опе-

источника (SS) ранда приемника (DD)

Формат двухадресных команд

Метод адресации кодируется тремя двоичными разрядами:

Метод адресации

------------------------------

| | | |

------------------------------

| | |--Признак прямой (0)

или косвенной (1)

|- - - -| адресации

|

|

|

- - - - Адресации:

00 - регистровая

01 - с автоувеличением

10 - с автоуменьшением

11 - индексная

Таким образом, существует всего 8 способов адресации (4 прямых

и 4 косвенных).

Система команд центрального процессора (ЦП) приведена в прило-

жении 1.

5.4. Программное обеспечение ПК

Для организации взаимодействия структурных компонентов между

собой ПК имеет резидентское программное обеспечение, которое постоян-

но находится в ПЗУ модуля процессора и начинает работать сразу же

после включения питания.

Состав резидентного ПО ПК:

I. Программа холодного старта.

2. Программа взаимодействия ПК в локальной сети.

3. Программа пультового терминала.

4. Программа обработки данных с клавиатуры.

5. Программа вывода символов на экран монитора.

6. Программа HALT-монитора.

7. Программа графических примитивов.

8. Стандартный знакогенератор.

9. Программа обмена данных с периферийными устройствами.

Программа холодного старта начинает работу при нажатии на кноп-

ку "ПУСК". Она устанавливает все устройства, входящие в ПК, в началь-

ное положение и при наличии подключения к каналу ПК платы локальной

сети передает управление программе взаимодействия ПК в локальной

сети. Программа взаимодействия ПК в локальной сети выводит на экран

видеомонитора надпись "ЖДИТЕ" настраивает ПК на прием информации

на локальной сети. При отсутствии платы локальной сети, либо при

одновременном нажатии на клавиши "УПР" и "ФСД/СТОП" (здесь и далее

в таких случаях рекоменуется первой нажать клавишу "УПР" и, зафик-

сировав ее, нажать следующую клавишу) процессор переходит на програм-

му пультового терминала.

Программа пультового терминала непосредственно взаимодействует

с программой обработки данных с клавиатуры, программой вывода сим-

волов на экран видеомонитора, стандартным знакогенератором. При этом

на экране видеомонитора появляется надпись "ПУЛЬТ". В этом режиме

монитор системы отрабатывает следующие директивы, вводимые с клавиа-

туры:

УПР и L - очистка экрана;

S - вывод на экран видеомонитора содержимого регистров

процессора;

D, 1D - загрузка операционной системы в ОЗУ с дисковода

с номером 1;

2D, 3D - загрузка операционной системы в ОЗУ с дисковода

с номером 2;

/ - раскрытие содержимого ячеек памяти;

G - выполнение программы;

N - выход на программу взаимодействия ПК в локальной

сети;

УПР и СТОП - останов выполняемой программы.

Программа вывода символов на экран видеомонитора в режиме вы-

вода алфавитно-цифровой информации формирует 25 строк по 50 символов.

Каждый символ формируется матрицей точек 8х8.

Рис.3. Матрица формирования изображения алфавитно-цифрового

знака на экране видеомонитора

Расстояние между строками формируется программно, путем запол-

нения нулями участка растра, находящегося под знакосинтезирующей

матрицей (рис.3).

Программа графических примитивов формирует изображение точки

и линии при выводе графической информации на экран видеомонитора.

5.5. Работа канала персонального компьютера

Персональный компьютер имеет модульный принцип построения, т.е.

все функциональные блоки ПК выполнены в виде конструктивно закончен-

ных устройств (модулей), связь между которыми осуществляется через

единый канал обмена информацией. Канал обмена информацией является

простой быстродействующей системой связей, соединяющей процессор,

память и все внешние устройства.

На рис.4 представлена упрощенная блок-схема ПК.

Рис.4. Блок-схема ПК

Все модули, подключенные к каналу ПК, используют одни и те же

канальные связи. Связь между двумя устройствами, подключенными к

каналу, осуществляется по принципу "УПРАВЛЯЮЩИЙ-УПРАВЛЯЕМЫЙ" (ак-

тивный-пассивный). В любой момент времени только одно устройство

является активным (процессор). Активное устройство управляет цикла-

ми обращения к каналу, удовлетворяет, если это необходимо, требова-

ниям прерывания от внешних устройств. Пассивное устройство (управляе-

мое) является только исполнительным. Оно может принимать или пере-

давать информацию только под управлением активного устройства.

Связь через канал замкнута, т.е. на управляющий сигнал, пере-

даваемый активным устройством, должен поступить ответный сигнал

пассивного устройства. Асинхронное выполнение операции передачи

данных устраняет необходимость в тактовых импульсах. В результате

этого обмен с каждым устройством может происходить с максимально

возможным для данного устройства быстродействием.

5.5.I. Сигналы управления каналом

Как адрес, так и данные (слова или байты) передаются по одним

и тем же I6 линиям адреса/данных К ДА(00-I5)Н. Любой цикл обращения

к каналу начинается с адресации пассивного устройства. После завер-

шения адресной части цикла активное устройство выполняет прием или

передачу данных, которые выполняются асинхронно и требуют ответа

от адресуемого устройства.

Функции синхронизации при передаче адреса и приеме/передаче

данных выполняют сигналы управления каналом К СИА Н, К БАЙТ Н, К

ВВОД Н, К ВЫВОД Н, К СИП Н.

Сигнал синхронизации активного устройства (К СИА Н) вырабатыва-

ется активным устройством (процессором). Передний фронт этого сигна-

ла означает, что адрес находится на линиях К ДА(00-I5)Н. Сигнал

К СИА Н сохраняет активный уровень до окончания текущего цикла обра-

щения к каналу.

Сигнал синхронизации пассивного устройства (К СИП Н) информи-

рует активное устройство о том, что данные приняты с линией К ДА(00-I5)Н

или данные установлены на информационных линиях. Этот сигнал выраба-

тывается в ответ на сигнал К ВВОД Н и К ВЫВОД Н.

Сигнал К ВВОД используется в двух случаях:

I. При вырабатывании во время действия сигнала К СИА Н он озна-

чает ввод данных по отношению к активному устройству. Сигнал К ВВОД

вырабатывается, когда активное устройство готово принять данные от

пассивного устройства;

2. При вырабатывании вместе с сигналом К ВПР Н (сигнал К СИА Н-

ПАССИВНЫЙ) означает, что выполняется операция ввода адреса вектора

при прерывании программы. Сигнал К ВЫВОД Н означает, что по отноше-

нию к активному устройству выполняется операция вывода, и на линиях

К ДА(00-I5)Н помещены истинные данные. Выработка сигнала К ВЫВОД Н

активным устройством по отношению к подаваемым в канал данным задер-

жана не менее чем на I50 нс. Пассивное устройство, отвечая на сигнал

К ВЫВОД Н, должно вырабатывать ответный сигнал К СИП Н, чтобы завер-

шить операцию передачи данных.

Сигнал вывода байта (К БАЙТ Н) используется в двух случаях:

I. При вырабатывании в адресной части цикла для указания, что

далее следует операция "ВЫВОД БАЙТА";

2. При передаче данных в цикле ВЫВОД В для указания, что выво-

дится байт.

Сигнал запрос прерывания К ЗПР Н вырабатывается пассивным уст-

ройствром, если его триггеры запроса прерывания и разрешения прерыва-

ния установлены. Этот сигнал информирует процессор о том, то уст-

ройство готово передавать или принимать данные. Если 7 разряд ССП уста-

новлен в ноль, процессор разрешит прерывание, вырабатывая сигналы

К ВВОД Н и КППРОН (выходной сигнал подтверждения прерывания).

Сигнал выбора (внешнего устройства (К ВУ Н) вырабатывается

активным устройством, когда в канал передается адрес, относящийся к

последним 4К адресов (с I60000 по I77776). Сигнал К ВУ Н остается

активным на время адресной части цикла обращения к каналу.

Сигнал К СБРОС Н вырабатывается процессором, чтобы выполнить

начальную установку всех устройств, подключенных к каналу. Сигнал

К СБРОС Н вырабатывается программно по команде и при пуске програм-

мы (нажмите клавиши "G").

5.5.2. Циклы обращения к каналу

Для выполнения любой команды процессору требуется выполнить

хотя бы одну операцию обращения к каналу. Для некоторых команд тре-

буется выполнить несколько операций. Первой такой операцией для всех

команд является ввод данных из ячейки памяти, адрес которой опреде-

ляется счетчиком команд (CK). Все операции обращения к каналу для

ввода и вывода данных называются циклами обращения к каналу. Если

для выполнения команды не требуется обращаться за операндами к па-

мяти или к внешним устройствам, дополнительных циклов канала не

требуется. Однако, если выполняется команда с обращением к памяти

или устройствам, то в этом случае могут выполняться любые из следую-

щих циклов: ввод; ввод-пауза-вывод: вывод; вывод Б.

5.5.2.I. Цикл ВВОД

Направление передачи при выполнении операций обмена данными

определяется по отношению к активному устройству. При выполнении

цикла ВВОД данные передаются от пассивного устройства к активному.

Временная диаграмма выполнения цикла ВВОД представлена на рис.5.

Рис.5. Временная диаграмма выполнения цикла ВВОД

Порядок выполнения операций следующий:

Активное устройство в адресной части передает по линиям К

ДА(00-I5) H адрес, a также вырабатывает сигнал K BУ H, если адрес

находится в диапазоне I60000-I77777. Hе менее чем через I50 нc после

установки адреса активное устройство вырабатывает сигнал К СИА H,

предназначенный для запоминания адреса во входной логике выбранного

устройства.

Пассивное устройство дешифрирует адрес и запоминает его.

Активное устройство снимает адрес с линий К ДА (00-I5) H, очища-

ет линию К ВУ H и вырабатывает сигнал K ВВОД H, сигнализируя о том,

что оно готово принять данные от пассивного устройства и ожидает по-

ступления сигнала К СИП Н.

Пассивное устройство помещает данные на линии К ДА(00-I5)Н

и вырабатывает сигнал К СИП H, сигнализирующий о том, что данные

находятся в канале. Если сигнал К СИП H не вырабатывается в течение

I0 мкс после выработки сигнала К ВВОД Н, центральный процессор пе-

реходит к обслуживанию внутреннего прерывания по ошибке обращения

к каналу с адресом вектора 4.

Активное устройство принимает сигнал К СИП Н, принимает данные,

снимает сигнал К ВВОД Н.

Пассивное устройство снимает сигнал К СИП H, завершая операцию

передачи данных.

Активное устройство снимает сигнал К СИА Н по заднему фронту

сигнала К СИП H, завершая тем самым канальный цикл ВВОД.

Во время выполнения цикла ВВОД сигнал К БАЙТ H не вырабаты-

вается.

5.5.2.2. Цикл ВЫВОД

При выполнении цикла ВЫВОД данные передаются от активного уст-

ройства к пассивному, например, происходит запись данных в память.

Временная диаграмма выполнения цикла ВЫВОД представлена на

рис.6.

Рис.6. Временная диаграмма выполнения цикла ВЫВОД

Порядок выполнения операций следующий:

Активное устройство в адресной части цикла передает по линиям

К ДА(00-I5)Н адрес, а также сигнал К ВУ Н, если это необходимо.

Кроме того, в цикле "ВЫВОД" в адресной части вырабатывается

сигнал К БАЙТ H. He менее чем через 150 нс после установки адреса

вырабатывается сигнал К СИА Н. Функции, выполняемые этими двумя

сигналами, те же, что и в цикле ВВОД.

Пассивное устройство дешифрирует адрес и запоминает его. Актив-

ное устройство снимает адрес с линий К ДА(00-I5)Н, очищает линию

К ВУ H и снимает сигнал К БАЙТ Н. После этого активное устройство

помещает данные на линии К ДА(00-I5) и вырабатывает сигнал

К ВЫВОД Н.

Пассивное устройство принимает данные с линий К ДА(00-I5)Н и

вырабатывает сигнал К СИП Н.

Активное устройство снимает сигнал К CИА H, завершая цикл кана-

ла ВЫВОД.

В цикле ВЫВОД сигнал К БАЙТ Н в части передачи данных может

быть как пассивным, так и активным, определяя тем самым вывод

I6-разрядного слова или вывод байта.

5.5.2.3. Цикл ВВОД-ПАУЗА-ВЫВОД

Этот цикл аналогичен операции считывание-модификация-запись.

Временная диаграмма выполнения цикла ВВОД-ПАУЗА-ВЫВОД представлена

на рис.7.

Адресная часть и ввод данных выполняется аналогично циклу ВВОД.

Однако К СИА Н остается активным и после окончания ввода данных, что

позволяет осуществлять вывод модифицированных данных без повторения

адресной части цикла.

Операция по выводу данных может быть байтовой, поэтому сигнал

К БАЙТ Н в это время может быть как пассивным, так и активным.

5.6. Средства обеспечения программной совместимости ПК с машинами семейства "Электроника-60"

Основная сложность переноса существующего системного и приклад-

ного программного обеспечения, разработанного для машин семейства

Рис. 7. Временная диаграмма выполнения цикла ВВОД-ПАУЗА-ВЫВОД

"Электроника-60", заключается в том, что в качестве системного тер-

минала предполагается использование самостоятельного устройства,

подключаемого к каналам ИРПС или МПИ. Терминал должен выполнять

достаточно широкий набор функций ввода, вывода и редактирования сим-

вольной и, возможно, графической информации. Обычно для решения этих

задач используют дополнительную микроЭВМ, подключаемую как внешнее

устройство. Однако в данном ПК использовано решение, позволяющее

на системном процессоре полностью эмулировать некоторые внешние уст-

ройства, в том числе системный терминал.

Основная идея заключается в следующем:

В общем объеме оперативной памяти "открываются" ячейки, соот-

ветствущие адресам регистров внешних устройств, подлежающих эмуляции;

При обращении программы к этим ячейкам вырабатывается запрос

на прерывание, в прикладном программном обеспечении неиспользуемое,

и фиксируется источник прерывания; сигнал подтверждения прерывания

приводит к перераспределению карты памяти - появляются системные

области, в которых расположены программа обработки прерывания и ее

рабочие ячейки;

По источнику прерываний определяется эмулируемое устройство

И/ИЛИ по содержимому ячейки-регистра этого устройства – действия,

которые необходимо выполнить;

Эмулируется работа устройства;

Если других источников прерывания зафиксировано не было, управ-

ление возвращается к прерванной программе (при этом карта памяти

возвращается к исходному виду).

6. УСТРОЙСТВО И РАБОТА СОСТАВНЫХ ЧАСТЕЙ ПК

Конструктивно ПК состоит из следующих функционально закончен-

ных узлов и блоков:

модуль процессора 6.I20.I07;

модуль ОЗУ 6.I20.I08;

модуль локальной сети и таймер 6.I20.I09;

модуль электронный 2MБ5 2.087.024;

модуль электронный 2МБI2 2.087.024-0I;

блок клавиатуры 3.059.007;

видеоконтрольное устройство (ВКУ).

6.1. Модуль процессора

Функционально модель процессора 6.120.107 ЭЗ состоит:

процессорное ядро;

системное ПЗУ;

контроллер клавиатуры;

аппаратный умножитель;

HALT-монитор.

Процессорное ядро включает в себя центральный процессорный эле-

мент D1 , выполняющий функции арифметико-логического устройства (АЛУ).

пять БИС управляющей памяти D2...D6, системный контроллер D18, два

магистральных приемопередатчика (МПП) D21, D24.

АЛУ предназначено для приема, хранения, обработки I6-разрядных

чисел. Преобразование данных выполняется в соответствии c I2-разряд-

ным кодом микрокоманды.

Последовательность фаз работы микросхемы определяет внутренний

блок синхронизации, функционирование которого начинается с поступ-

лением отрицательного фронта по входу сигнала сопровождения микро-

команды ВК (вывод 30).

Выполнение любой микрокоманды состоит из комбинации следующих

фаз:

приема (приема и дешифрации микрокоманды и в некоторых микро-

командах приема операнда по магистрали данных);

чтения (чтения информации из источника (РОН, АКК, СК, К) в

АЛУ и ее обработки);

записи (окончание обработки информации и ее запись в прием-

ник (РОН, АКК, СК, К);

выдачи (выдача результата операции в МД).

Прием микрокоманд и обмен данными по магистрали производится

асинхронно и соответственно квитируется сигналами по выводам ВК-ФI

и В-П, т.к. по шине микрокоманд информация может только приниматься

в АЛУ, выводы ВК и ФI - однонаправленные. Сигналы В и П двунаправ-

ленные, т.к. квитируют передачу данных по МД. При приеме данных в МД

сигнал на входе В генерируется системным контроллером D18 и иниции-

рует начало фазы ввода данных, сигнал на выходе П служит квитанцией

о приеме информации в АЛУ. При выдаче данных в МД сигнал на выходе В

инициирует начало фазы вывода данных, сигнал на входе П служит кви-

танцией для ЦПЭ о приеме информации во внешние схемы. Ограничений на

время ответа не существует.

Управляющая память (УП) представляет собой программируемую ло-

гическую матрицу (ПЛМ) с памятью.

Она предназначена для управления работой процессорного ядра и

сочетает в себе функции БИС блока микропрограммного управления и ПЗУ

микрокоманд. Микросхемы с номерами кодировок 0001, 0002, 0004 пред-

назначены для управления АЛУ, БИС УП с кодировкой 0007 - для управ-

ления системным контроллером D18, БИС с кодировкой 0006 предназ-

начена для аппаратной реализации команд расширенной арифметики (ум-

ножение, деление, сдвиги – MUL, DIV, ASH, ASHC).

Сигналы на входах R0 и RI по положительному фронту устанавли-

вают микросхему УП в исходное состояние. При наличии логического

нуля на выводе В происходит прием информации с магистрали данных

во входной регистр и по магистрали признаков ветвление в регистр

признаков. Приняв информацию, микросхема устанавливает уровень ло-

гического нуля на выводе П и активный низкий уровень на выводе КК.

При снятии сигнала "ЛОГИЧЕСКИЙ НОЛЬ" на выводе В снимается сигнал

и на выводе П.

По отрицательному фронту сигнала ФI прекращается выдача микро-

команды и происходит "ПОДБРОС" в высокий потенциал состояния выво-

дов МК (0-12). Если к этому времени сформирована следующая микроко-

манда, то происходит ее запись в регистры с последующей выдачей.

Системный контроллер предназначен для связи внутреннего интер-

фейса процессора с внешним стандартным интерфейсом канала типа

Q-шины (OCT II305.903-80).

Внутренний интерфейс процессора содержит символы, обеспечиваю-

щие работу процессорного ядра. Это сигналы квитирования АЛУ и УП,

I6-разрядная информационная магистраль, четырехразрядная магистраль

кода прерывания, сигналы управления МПП. Сигналы квитирования KBI,

KB2, КВЗ, КП обеспечивают передачу по I6-разрядной двунаправленной

магистрали, адресов, данных, векторов прерывания в данный момент

обслуживания.

Внешний интерфейс процессора содержит сигналы, обеспечивающие

работу всех устройств, подключенных к каналу.

Вывод КОШ служит для подключения RС-цепочки, задающей длитель-

ность сигналов "ДЧТ", "ДЗП" до сигнала "OTB" и длительность сигнала

"СБРОС".

Вход установки режима начального пуска НП, путем подачи на не-

го высокого потенциала, установлен в режим выхода на системное ПЗУ

через адрес-вектор 24.

Выходы C1, C2 управляют направлением передачи данных через ма-

гистральные приемопередатчики.

Системный контроллер D18 через входы Р, Т принимает информа-

цию o седьмом и четвертом разряде регистра слова состояния процес-

сора для обработки прерываний.

При нажатии на кнопку "ПУСК" на передней панели на выводах

8, 12 микросхемы D40 формируются сигналы начального пуска, которые

устанавливают микросхемы управляющей памяти и системного контролле-

ра в начальное положение и запускают микропрограмму начального пус-

ка. Данная микропрограмма формирует обращение процессорного ядра к

ячейкам памяти с адресами 160006 и 160010, где читает и устанавли-

вает программный счетчик и слово состояния процессора соответственно.

В адресном пространстве процессора с адреса 160000 по 167776

занимает системное ПЗУ. Адресное пространство процессора 140000-157776

зарезервировано под дополнительные 4к слов системного ПЗУ.

При обращении к области памяти обязательного системного ПЗУ

контроллер запоминающего устройства D15 вырабатывает сигнал ВКО,

который разрешает выборку данных из ПЗУ D9, D10. Адрес, по которо-

му ведется обращение, фиксируется в регистре D7, D8. Сигнал ОТВ фор-

мирует микросхема D15 с задержкой относительно сигнала ОБМ, опреде-

ляемой времязадающей цепочкой R4, C4.

После установки счетчика команд и ССП процессор выходит на про-

грамму "ХОЛОДНОГО" старта, записанной в системном ПЗУ.

После программы "ХОЛОДНОГО" старта процессор выходит на програм-

му обработки данных с клавиатуры.

Контроллер клавиатуры собран на микросхемах D26, D27. Данные

c клавиатуры в последовательном коде через элемент D30.1 поступают

на нулевой разряд канала К0 D26. На вход ЗП D26 поступают тактовые

импульсы с частотой в 2 раза меньшей частоты импульсов, на основе

которых формируется информационная последовательность в блоке кла-

виатуры. Выходы канала KI D26 соединены с входами канала К0 D26 со

смещением на один разряд, т.е. последовательный код с клавиатуры

преобразуется в параллельный. По достижении стартовой посылки послед-

него разряда KI D26 триггер D37.2 формирует сигнал готовности конт-

роллера клавиатуры к выдаче данных. Этот сигнал поступает в HALT-мо-

нитор. Инверсным сигналом с триггера D37.2 код символа переписыва-

ется в регистр D27. По окончании записи вырабатывается сигнал ЗЗП,

который сбрасывает входной регистр D26.

После обработки сигнала Н2 (обращение к регистру данных клавиа-

туры, сформированного в модуле ОЗУ), HALT-монитор выдает сигнал

чтения содержимого регистра D27 и код символа вводится в процессор.

Команды умножения (деления) выполняются БИС умножителя D17

совместно с БИС селектора каналов D19 и БИС УП D4.

После поступления команды умножения (деления) на шину ДА БИС УП

(0006) микросхема вырабатывает микрокоманды, под действием которых

происходит обработка двух операндов. Умножение начинается с засылки

двух операндов в регистры умножителя. При операциях чтения, записи

данных умножитель формирует сигнал ГОТ, отмечающий окончание опера-

ции. Чтение результата производится с младших разрядов произведения.

Последним читается регистр состояния. Время умножения < 2 мкс отсчи-

тывается с загрузки второго операнда до чтения первого слова резуль-

тата. При этом используются адреса 170000, 170002, 170004, которые

дешифрируются селектором каналов D19.

HALT-монитор является процедурой, предназначенной для управле-

ния процессами, "невидимыми" для основного программного обеспечения.

К ним относятся: эмуляция системной консоли (клавиатуры), операции

пультового терминала, работа с расширенной памятью.

Запросы не использование ресурсов HALT-монитора формируются

двумя способами: команда HALT или запрос по линии прерывания ОСТ.

Для диспетчеризации запросов предусмотрен регистр запросов с адресом

170007. Младший байт этого регистра 170006 является регистром данных

клавиатуры. Запросы обрабатываются согласно их приоритету. По окон-

чании обработки содержимое регистра сбрасывается. Случаи возникнове-

ния прерываний по линии ОСТ (согласно приоритету):

появление канального сигнала СБРОС;

запрос на обслуживание локальной сети;

обращение к группе ячеек 177560-177566, соответствующих ре-

гистрам системной консоли;

нажатие клавиши на клавиатуре.

Выполнение команды HALT‚ также как и ввод с клавиатуры кода 0

переводит процессор в режим пультового терминала.

Использование для входа в HALT-монитор прерывания HALT объяс-

няется тем, что это единственное прерывание, адрес вектора которого

лежит в адресном пространстве системного ПЗУ. Для своих нужд HALT-

монитор использует область памяти 177600-177776, доступ к которой

разрешается сигналом подтверждения прерывания HALT. Этим достигает-

ся полная "прозрачность" процедур HALT-монитора.

В схему аппаратной поддержки HALT-монитора входят:

регистр приема запросов;

регистр фиксации запросов;

схема формирования сигнала прерывания OCT;

регистр управления памятью.

Регистр приема запросов D32 осуществляет накопление запросов

до следующей обработки. При разрешении прерывания по линии OCT его

содержимое переписывается в регистр фиксации запросов D28, откуда

может быть считано на шину данных. Сигналом "подтверждения прерыва-

ния ОСТ" содержимое регистра сбрасывается. Обрабатывается запрос с

высшим приоритетом, после чего содержимое регистра фиксации очища-

ется. Схема формирования сигнала по линии ОСТ привязывает прерыва-

ние к сигналу КВЗ (вывод 11 D18, ввод команды), исключая этим вло-

женные прерывания ОСТ.

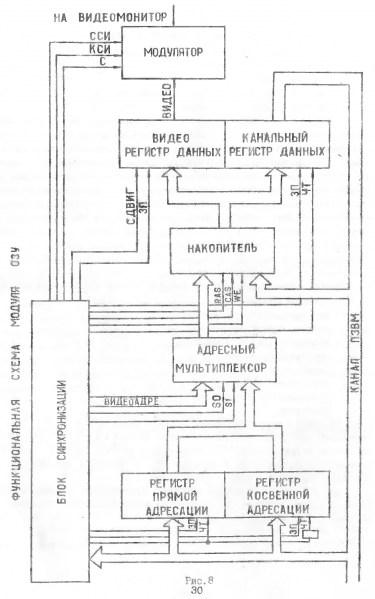

6.2. Модуль ОЗУ

Функционально модуль ОЗУ 6.120.108 ЭЗ состоит из следующих узлов:

адресный дешифратор;

блок синхронизации;

регистр прямой адресации;

регистр косвенной адресации;

адресный мультиплексор;

накопитель;

видеорегистр данных;

канальный регистр данных;

модулятор.

Адресный дешифратор собран на микросхемах D12, D13, D15. При

обращении процессора к области памяти, занимаемой ПЗУ (160000-170000),

на выходе мультиплексора D12 формируется высокий уровень, который

фиксируется сигналом СИА в регистре D13 и блокирует прохождение

сигналов обращения к памяти через элемент D4.1

Для эмуляции стандартных устройств клавиатуры и терминала в

массиве памяти разрешен доступ по адресам 17560-177576. Сигналы

выборки формируются микросхемой D15.

Рис.8

177566 - обращение к регистру данных терминала (выход D0).

Ha основе данного сигнала формируется запрос на

прерывание HI.

177564 - обращение к регистру состояния терминала (выход D1).

177562 - обращение к регистру данных клавиатуры (выход D2).

На основе данного сигнала формируется запрос на

прерывание Н2.

177560 - обращение к регистру состояния клавиатуры (выход D3).

177572 - обращение к регистру адреса косвенной адресации

(выход Е2).

177570 - обращение к регистру данных косвенной адресации

(выход E3).

Блок синхронизации построен на базе кварцевого генератора, со-

бранного на микросхеме D1. Последовательность импульсов стабильной

частоты 8 МГц делится микросхемой D8 на последовательности со сле-

дующими частотами: 4 МГц, 2 МГц, 1 МГц.

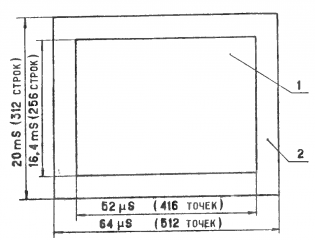

Видеосчетчик, собранный на микросхемах D18...D21 , делит вход-

ную последовательность импульсов 1 МГц на последовательности, убы-

вающими по частоте кратными двум. Ha последнем разряде видеосчетчи-

ка (конт.6 D21) формируется частота 50 Гц, запускающая формирова-

тель кадровых синхроимпульсов, собранный на одновибраторах D22.1,

D22.2. Одновибратор D22.1 формирует импульсы нижнего бланка, опре-

деляющие расстояние от нижней кромки рабочего растра до конца полно-

го рабочего поля видеомонитора. Одновибратор D22.2 формирует стан-

дартный кадровый синхронизирующий импульс.

Строчный синхронизирующий импульс формируется элементом D23.1.

Элемент D23.2 вырабатывает импульс сброса видеосчетчика при

подсчете 3I2 простейших линий в растре.

Формирование рабочего поля растра приведено на рис.9.

Обмен данными с накопителем может производиться байтами и сло-

вами. Для этого используются регистры косвенной и прямой адресации.

При прямой адресации адрес ячейки памяти записывается в регистр D26,

D27 непосредственно из канала по сигналу СИА.

1. Рабочее поле растра, формируемое контроллером видеотерминала

2. Рабочее поле растра, формируемое контроллером видеомонитора

Рис.9. Формирование рабочего растра синхроимпульсами

При обращении к расширенной памяти (128 Кбайт) используется

регистр косвенной адресации (D28, D29). Запись в этот регистр осу-

ществляется при обращении к ячейке памяти с адресом I77572. При об-

рещении к ячейке с адресом 177570 происходит чтение или запись по

адресу, хранящемуся в регистре косвенной адресации D28, D29 . Выхо-

ды регистра прямой адресации D27, D26 соединены параллельно с выхо-

дами регистра косвенной адресации со сдвигом на один разряд. Нулевой

разряд регистра прямой адресации поступает на схему обработки сигна-

ла К БАЙТ Н ( D9.4, D9.5, D30 ). При наличии сигнала К БАЙТ Н на

внешней шине управления при операции записи или чтения нулевой раз-

ряд данного регистра участвует в выборе ячейки памяти и таким обра-

зом организуется доступ к I28 Кбайтам накопителя. При обмене дан-

ными размером в слово регистр косвенной адресации отключается и

элемент D16.5 формирует логический ноль в разряде AI7 регистра кос-

венной адресации.

В зависимости от вида адресации один из адресов поступает на

входы адресного мультиплексора, собранного на микросхемах D31 ...D34

Ha четырехвходовую ячейку адресного мультиплексора поступают разря-

ды от младшей и старшей части адреса и младшей и старшей части ви-

деоадреса, формируемого видеосчетчиком и необходимого для регенера-

ции динамической памяти. Под управлением сигналов S1, S0 адресный

мультиплексор пропускает на адресные входы накопителя старший или

младший байт адреса обращаемой ячейки, либо адреса регенерации ди-

намической памяти.

Поступление старшего или младшего байта сопровождается квити-

рованием сигналов RAS и CAS. Сигналы RAS и CAS формируются бло-

ком синхронизации.

В то время, когда на входы накопителя подается адрес от ви-

деосчетчика, т.е. происходит процесс регенерации памяти, одновремен-

но считывается информация из области памяти, называемой видео ЗУ.

Информация, записанная в видео ЗУ, считывается в видеорегистр

D53...D56 , который разделен на старший и младший байт. После защел-

кивания информации сигналом, она последовательно выводится по сигна-

лу C из старшего и младшего байтов и поступает на модулятор.

Модулятор смешивает строчные, кадровые синхроимпульсы с инфор-

мационным сигналом и на эмиттере VT1 формируется полный видеосигнал.

Наличие двух битов информации o точке растра позволяет получить 4

градации яркости при выводе изображения на экран монитора.

При каждом обращении процессора к памяти вырабатывается сигнал

СИП триггером D11.2‚ сигнализирующий о завершении приема.

Канальный регистр данных D51, D52 служит для фиксации данных,

предназначенных для вывода в канал.

Доступ к рабочему полю видеотерминала (32 Кбайта) осуществляет-

ся с помощью косвенной адресации, начиная с адреса I40000. Оставшие-

ся 32 Кбайта расширенной памяти отведены под электронный стек. Доступ

к ним осуществляется также с помощью косвенной адресации (адреса

100000 - 137777).

6.3 Модуль локальной сети и таймер

При построении локальной сети ЭВМ (ЛС ЭВМ, в дальнейшем ЛС) одна

из ЭВМ является ведущей, главной, центральной (ГЭВМ), остальные ведо-

мыми, периферийными (ВЭВМ). Каждая ЭВМ в своем составе имеет адаптер

локальной сети (АЛС).

Модуль ЛС 6.120.109 33, кроме БИС адаптера канала (АК), содер-

жит схемы приемопередатчиков линии, схемы сопряжения с магистралью

микроЭВМ, внутренние схемы адаптера локальной сети.

6.3.1. Сопряжение адаптера локальной сети с магистралью микроЭВМ

Для микроЭВМ модуль АЛС является набором ячеек, которые пред-

ставляют собой внутренние регистры адаптера ЛС, БИС АК (D38) имеет

три внутренних 16-разрядных регистра: регистр данных приемника

(RGL), регистр данных передатчика (RGD), регистр инструкций (RGINS).

При этом RGL доступен по чтению (сигнал SED), RGD доступен по за-

писи (SED), RGINS доступен по записи (сигнал SEINS). Это позволяет

ввести дополнительное обращение к внутренним схемам АЛС, не затраги-

вающее БИС АК. Такое дополнительное обращение — это «ЧТЕНИЕ RGINS»

(SEINS). По этой команде можно передать в микроЭВМ состояние неко-

торых внутренних триггеров АЛС, совокупность которых можно назвать

регистром состояния адаптера локальной сети. Таким образом, модуль

АЛС занимает два адреса в адресном пространстве микроЭВМ.

Шина адреса/данных модуля АЛС развязана от системной шины маги-

стральными приемопередатчиками К588 (D1, D2). Выбор модуля АЛС де-

лается сигналами SEL0, SEL1 от селектора адреса, при этом адреса

регистров следующие:

170010 — регистр RGINS АЛС (D30) при записи,

— регистр состояния АЛС при чтении;

170012 — регистр RGD АЛС при записи,

— регистр RGL АЛС при чтении.

Сигналы SEL0 и SEL1 через логические элементы поступают на

входы SEINS и SED БИС АК. Системный сигнал чтения (RD) поступает

на входы ERD1 и ERD2 БИС АК. Системные сигналы записи (WRL, WRH)

совместно с сигналами ВП («ВЫПОЛНЕНО») магистральных приемопередат-

чиков (МПП) BA1 поступают после логического преобразования на

входы EWR1 и EWR2 БИС АК. Сигнал ВП микросхем МПП используется

для учета задержек информационных битов в МПП.

Для управления работой модуля АЛС в него введены следующие про-

граммно доступные триггеры:

триггер (D26.2) разрешения прерывания (РПР) (доступен по

чтению и по записи);

триггер (D31.2) требования прерывания (ТПР) (доступен по

чтению);

триггер (D26.1) разрешения опроса сети — для АЛС ГЭВМ/триг-

гер активности для АЛС ВЭВМ (РОП/АКТ) (доступен по записи и чтению):

триггер (D31.1) ошибки (ТОШ) (доступен по чтению).

Информация, загружаемая из микроЭВМ в RGD БИС АК, посылается

затем в линию в виде слова данных (СД). Информация, загружаемая из

микроЭВМ в RGINS БИС АК, посылается в линию в виде командного сло-

ва (КС) - для АЛС ГЭВМ (ОС) - для АЛС ВЭВМ.

Принимаемая из ЛС информация загружается в RGL БИС АК и может

быть прочитана в микроЭВМ. Кроме того, БИС АК после принятия из ли-

нии сообщения вырабатывает некоторые сигналы, характеризующие это

сообщение: CHD - определяет достоверность сообщения, CHA - укахыва-

ет на совпадение кода в адресной части КС с собственным адресом БИС

АК, INS - тип сообщения (КС/ОС или СД), SAINS - наличие определен-

ной комбинации внутри сообщения, МО - указывает на наличие общего

(группового) режима.

Все указанные сигналы обрабатываются логикой АЛС на основе

ПЗУ (D36) (анализ пришедшего сообщения). Кроме того, сигналы

MO, CHA и INS доступны при чтении РС АЛС в микроЭВМ.

Передача информации из БИС АК в линию инициируется сигналами

SID (передача RGD) и SAINS (передача RGINS). БИС АК может работать

в двух режимах: контроллера (в составе АЛС ГЭВМ) или оконечного уст-

ройства (в составе АЛС ВЭВМ). Физически инициатором обмена по линии

может быть только контроллер (т.е. АЛС ГЭВМ). Поэтому запись в RGINS

БИС АК мредусмотрена двух модификаций: "со стартом" (т.е. передача

в линию после записи) и "без старта" (т.е. передача в линию не выпол-

няется). Модификация определяется значением младшего (0-го) разряда

слова, загружаемого в RGINS из микроЭВМ. В этом участвуют элемен-

ты D8.2, D4.3, D24.1.

6.3.2. Порядок установления связи в сети

Ввиду того, что АЛС ВЭВМ физически не может быть инициатором

обмена по линии, то необходим постоянный опрос всех оконечных уст-

ройств (АЛС ВЭВМ). Цель опроса — выявить, нет ли среди них такого,

который имеет требование на обслуживание (то есть «хочет» обменяться

информацией с ГЭВМ). Этот постоянный опрос сети можно выполнить

под контролем и при участии ГЭВМ, используя системный таймер

микроЭВМ. Однако, такой постоянный опрос сети, очевидно, будет из-

лишне перегружать ГЭВМ, требуя от нее дополнительных ресурсов вре-

мени. Поэтому инициируется опрос сети аппаратно, без

участия ГЭВМ. Для этого АЛС ГЭВМ имеет собственный таймер и при на-

личии разрешения опрос сети (РОП=1) периодически посылает в линию

КС с комбинацией, вызывающей в выбранном оконечном устройстве форми-

рование активного SAINS.

Элементы, входящие в состав схемы циклического опроса:

на ВЭВМ — D36 (выход 11), D4.3, D24.1

на РМП — D17.2, D14.6, D27.2, D14.3, D14.4

АЛС ГЭВМ имеет также регистр и инкрементор номера оконечного

устройства. Это обеспечивает циклический опрос по сети всех оконеч-

ных устройств. Схема учитывает количетво оконечных устройств, за-

даваемое перемычками. Инкрементор построен на элементах D6 и D7,

в формировании номера следующей опрашиваемой ВЭВМ участвуют элемен-

ты D22.2, D14.1. Для сохранения значения разрядов 10, 9, 8 (в стар-

шем байте) RGINS при записи в него нового номера ВЭВМ используется

регистр D5, из которого значения этих трех разрядов записываются в

БИС АК.

Каждый АЛС ВЭВМ имеет свой номер, задаваемый перемычками. Полу-

чение достоверного КС с кодом в адресной части, совпадающим с собст-

венным номером, делает АЛС ВЭВМ выбранными. Если АЛС ВЭВМ выбран,

принятое КС достоверно и вырабатывается активный сигнал SAINS, то

БИС АК посылает в линию ответное слово, не обращаясь при этом к мик-

роЭВМ. Посылаемое ОС содержит признак требования обмена — комбина-

ция, активизирующая SAINS в АЛС ГЭВМ.

6.3.3. Алгоритм установления связи

Установление связи в сети по требованию обмена от АЛС ВЭВМ со-

стоит из трех этапов:

1.1. Аппаратный циклический опрос сети.

1.2. Начало установления связи с АЛС ВЭВМ, потребовавщим

обмена.

1.3. Успешное установление связи с АЛС ВЭВМ.

Этап 1.1 состоит из следующих шагов:

1.1.1. ГЭВМ загружает в RGINS код с активным SAINS без

старта.

1.1.2. ГЭВМ устанавливает РОП=1.

1.1.3. Таймер АЛС ГЭВМ инициирует периодическую посылку в ли-

нию КС, при этом текущий номер АЛС ВЭВМ инкрементируется.

1.1.4. АЛС ВЭВМ в исходном состоянии пассивное (АКТ=0).

1.1.5. Получив КС с активным СИА, если нет ошибки (CHD) и

если активен сигнал SAINS, АЛС ВЭВМ выдает в линию ОС.

1.1.6. При необходимости обмена ВЭВМ загружает в RGINS код с

активным SAINS (в противном случае — с пассивным SAINS) без старта,

то есть 0-й бит равен нулю.

1.1.7. Получив ОС от АЛС ВЭВМ, адаптер ЛС ГЭВМ аппаратно выяв-

ляет SAINS. Если есть активный SAINS (и данные достоверны), то

АЛС ГЭВМ устанавливает триггер ТПР в «1», если установлен ранее

программно) триггер разрешения прерываний (РПР), то вырабатывается

требование в ГЭВМ.

В ГЭВМ идет требование прерывания Н4. Одновременно в АЛС ГЭВМ

сбрасывается триггер РОП, то есть прекращается дальнейший опрос сети.

1.1.8. АЛС ГЭВМ останавливает опрос сети и ждет обслуживания Н4.

1.1.9. ГЭВМ входит в программу обслуживания Н4.

...

6.5.3. Форматы служебных сообщений

Командное слово/ответное слово имеет следующий формат.

Биты 15-11 — код адреса АЛС БЭВМ (в КС - это номер АЛС ВЭВМ,

к которой послано КС, в ОС — это номер АЛС, пославшего ОС).

Биты 7-4 — биты SAINS. Комбинация 0000 и 1111 - это активный

SAINS. Кроме того, бит 6 — разрешение прерывания (РПР) устанавли-

вает триггер РПР в АЛС.

Бит 9 — для АЛС ГЭВМ должен устанавливаться в "1". От АЛС ВЭВМ

в линию идет ОС с «0» в 9-м бите.

Бит 1 — установка триггера разрешения опроса/триггера актив-

ности (РОП/АКТ).

Таймер

Таймер, конструктивно расположенный на плате модуля локальной

сети, предназначен для отсчета программируемых временных интервалов

и прерывания процессора в составе систем реального времени. Основу

таймера составляет БИС программируемого интервального таймера D42,

которая состоит из двух независимых каналов, организованных на осно-

ве 2 шестнадцатиразрядных счетчиков. Первый счетчик может работать

в режиме программируемого интервального таймера и в режиме програм-

мируемого делителя частоты, а второй счетчик работает лишь в режиме

программируемого интервального таймера. Кроме того, в состав данной

БИС входит независимый семиразрядный делитель частоты, который имеет

фиксированные коэффициенты деления соответственно 2, 4, 8, 16, 32,

64, 128.

На микросхеме D39 выполнен селектор адреса. Микросхема сравни-

вает коды в адресных посылках общей шины с адресом, заданным на вхо-

дах А (12-4). При совпадении уровней на выводах АД (12-4) с уровнями

на А (12-4), селектор адреса дешифрует разряды АД (1-3) и в соот-

ветствии с этим выдает сигнал выборки кристалла на одном из выходов

ВК0-ВК7.

В табл.6.1 дана зависимость состояния выходов ВК0-ВК7 от вход-

ного адреса.

Сигналы с выходов ВК5-ВК7 микросхемы D39 поступают на входы

выборов кристалла первого счетчика, второго счетчика, регистра со-

стояния микросхемы D42. Причем адресу 170020 соответствует выбор ре-

гистра состояния, 170022 - выбор первого счетчика, 170024 - выбор

второго счетчика.

Таблица 6.1

────────┬─────┬─────┬─────┬─────┬─────┬─────┬─────┬─────

│ ВК0 │ ВК1 │ ВК2 │ ВК3 │ ВК4 │ ВК5 │ ВК6 │ ВК7

────────┼─────┼─────┼─────┼─────┼─────┼─────┼─────┼─────

170020 │ 1 │ 1 │ 1 │ 1 │ 1 │ 1 │ 1 │ 0

170022 │ 1 │ 1 │ 1 │ 1 │ 1 │ 1 │ 0 │ 0

170024 │ 1 │ 1 │ 1 │ 1 │ 1 │ 0 │ 1 │ 0

170026 │ 1 │ 1 │ 1 │ 1 │ 0 │ 1 │ 1 │ 0

170030 │ 1 │ 1 │ 1 │ 0 │ 1 │ 1 │ 1 │ 0

170032 │ 1 │ 1 │ 0 │ 1 │ 1 │ 1 │ 1 │ 0

────────┴─────┴─────┴─────┴─────┴─────┴─────┴─────┴─────

Импульсы с частотой 8 МГц поступают на вход делителя на 2, вы-

полненного на D-триггере D41.2 и далее на тактовый вход С1 1-го счет-

чика. На тактовый вход С2 2-го счетчика поступают импульсы с часто-

той 50 Гц.

10-разрядный регистр состояния программируемого таймера D42 оп-

ределяют режим и условия работы таймера, разряды его по сигналу

СБРОС устанавливаются в "0" и имеют следующее значение:

разряд 0 - разряд полезный пользователю;

разряд 1 - режим работы 1-го счетчика. Если значение этого

разряда 0, то канал 1-го счетчика работает в режиме программируемо-

го интервального таймера, если - 1, то в режиме программируемого

делителя частоты;

разряды 2 и 3 - определяют режим пуска 1-го счетчика. Если

значения этих разрядов соответственно равны 1 и 0, то I-й счетчик

запускается по управляющему входу СО1 (при СО1=0 1 счетчик начи-

нает отсчет), если значения равны 0 и 1, то работа 1 счетчика бло-

кируется, а если значения равны 1 1, то запуск счетчика происходит

по тактовому входу С1;

разряды 4 и 5 - определяют режим пуска 2 счетчика. Если зна-

чения этих разрядов соответственно равны 1 и 0, то запуск 2 счетчи-

ка происходит по управляющему входу С2, и если значения равны 0

и 1, то работа 2 счетчика блокируется;

разряд 6 - блокировка выдачи сигнала ЗПР1. Если значение

равно 1, то происходит блокировка выдачи сигнала ЗПР1;

разряд 7 - блокировка выдачи сигнала ЗПР2. Если значение

равно 1, то происходит блокировка выдачи сигнала ЗПР2;

разряды 8 и 9 - фиксация прерывания соответственно 1 и 2

счетчика.

...

6.6. Накопитель на гибких магнитных дисках

Накопитель на гибких магнитных дисках НГМД-I служит для записи

и считывания информации, хранящейся на магнитных дисках. Он состоит

из модуля сопряжения, двух дисководов и двух модулей электронных

типа 2МБ для питания модуля сопражения и дисководов.

Модуль сопряжения выполняет функции контроллера накопителя и

Устройства сопряжения ПК с цифропечатающим устройством.

Контроллер накопителя на гибком магнитном диске (КНГМД) поддер-

живает подорожечную структуру записи с одной продольной плот-

ностью (метод записи ФМ), совместимую со структурой записи КНГМД

ДВК-2,3. Контроллер рассчитан на пдключение до 4-х накопителей типа

TEAC FD-55FV-003 или аналогов. Контроллер обеспечивает информационную

емкость форматированной дискеты 459 Кбайт (2 стороны по 80 дорожек).

Контроллер обеспечивает автоматическое отключение мотора при

отсутствии обращения от ЭВМ. КНГМД обменивается с процессором 8-ми

битными данными. Цикл обмена в режимах чтения-записи 64 мкс.

Структурная схема КНГМД представлена на рис.11. КНГМД включает

следующие узлы:

узел синхронизации;

кодер;

декодер;

сдвиговый и буферный регистры;

схема опознавания маркера;

схема формирования сигналов обмена;

схема управления накопитерем;

схема контроллера Q-шины;

таймера.

Узел синхронизации предназначен для выработки сигналов, управ-

ляющих процессами передачи и приема данных в/из накопителя. Узел

синхронизации состоит из задающего генератора 1 МГц (D12), стаби-

лизированного кварцевым резонатором и двух счетчиков Джонсона (D18,D30).

с коэффициентом деления 8. Сигналы с выходов первого счетчика ис-

пользуются для формирования бита, второго – для формирования байта.

На рис.12 представлена временная диаграмма работы счетчика D18.

Кодер (D27.1, D27.2, D27.3, D35) предназначен для преоб-

разования бита данных во временную последовательность, отвечающую

методу записи фазовой модуляции (ФМ).

... (рисунки)

Кодер использует две синхропоследовательности – Ф1 и Ф5. После-

Довательность Ф1 определяет положение синхроимпульсов, последователь-

Ность Ф5 – положение импульсов данных (рис.13).

Декодер предназначен для преобразования сигнала RDDATA (ДАННЫЕ

ЧТЕНИЯ), поступающего из накопителя, в поток двоичных данных. Деко-

дер состоит из формирователя импульсов (D11.4, D13.1), формирова-

теля окна детектирования (D25.1), триггера поиска (D13.2) и триг-

гера данных (D25.2).

Работа декодера заключается в следующем:

в исходном состоянии формирователь синхропоследовательностей

Ф1...Ф8 (D18) остановлен сигналом, снимаемым с инверсного плеча

триггера поиска;

из сигнала RDDATA по переднему фронту формируются короткие

импульсы. Первый импульс установит триггер поиска в состояние "1"

и отпустит тем самым счетчик D18;

сигнал Ф1 сбрасывает триггер данных;

сигналы Ф2 и Ф6 формируют начало и конец окна детектирования

(рис.14). Если в окно детектирования попадает импульс данных, уста-

Навливается триггер данных;

сигналом Ф6 сбрасывается триггер поиска и декодер возвращает-

Ся в исходное состояние.

Декодер обеспечивает правильную синхронизацию по фазе при прие-

ме последовательности хотя бы двух нулей.

Сдвиговый регистр (D28) предназначен для преобразования данных

из последовательной формы в параллельную при чтении с диска, и наобо-

рот, при записи. При чтении данные с декодера поступают на последова-

тельный вход S1 и вдвигаются по положительному фронту сигнала Ф0.

Преобразованные данные снимаются из канала A. При записи данные из

буферного регистра (D22) записываются через канал А положительным

фронтом сигнала Ф0 при условии, что счетчик битов D30 находится в

состоянии "0". Каждый следующий импульс Ф0 сдвигает содержимое ре-

гистра D28 на один бит в сторону старших разрядов. Данные с выхода

"7" канала B поступают на кодер.

Буферный регистр (D22) предназначен для временного хранения

передаваемых и принимаемых данных. В режиме чтения канал B является

входом, канал A – выходом на внутреннюю шину данных контроллера. За-

грузка данных синхронная по сигналу счетчика битов D30. В режиме

записи данные с шины записываются в регистр через канал A асинхрон-

но по сигналу интерфейса Q-шины.

Схема опознавания маркера (D32, D37) предназначена для синхро-

низации читаемой с диска информации по байтам. Работает только в ре-

жиме чтения. Формирует сигнал MARKER (03.D37) уровня "1", если в

регистре сдвига находится байт 363 (8).

Схема управления обменом информацией предназначена для выработ-

ки сигналов, синхронизируютщих отдельные узлы контроллера. Содержит

следующие узлы:

синхронизации операций с дорожкой;

синхронизации обмена с Q-шиной;

формирования сигналов контроля.

Синхронизатор операции с дорожкой (D31, D10.3, D7.5) выра-

батывает импульс (КТ1), начало и конец которого определяются сигна-

лом INDEX, при условиях:

накопитель готов к работе;

пришел импульс запуска операции RUN.

В режиме записи начало импульса дорожки точно соответствует мо-

менту установки сигнала INDEX. В режиме чтения начало дорожки опре-

деляется по сигналу MARKER. Импульс дорожки отпускает счетчик битов

D30, разрешая таким образом все операции по формированию и обмену

информацией.

Синхронизатор обмена с Q-шиной (D16, D26.1) вырабатывает сиг-

нал требования обмена TR, используемый для программного опроса. В ре-

жиме чтения сигнал TR устанавливается при записи прочитанного с диска

байта данных в буферный регистр, сбрасывается при чтении процессором

регистра данных. В режиме записи сигнал TR устанавливается при запи-

си байта данных из буферного регистра в сдвиговый регистр, сбрасыва-

ется при записи данных процессором в регистр данных.

Узел формирования сигналов контроля предназначен для выдачи про-

цессору информации о текущем состоянии контроллера накопителя. Фор-

мируются следующие сигналы:

RELOAD – устанавливается при пропадении сигнала READY (готов-

ность) от накопителя. Возможные причины: неисправность

накопителя, пропадание питающего напряжения привода,

открывание кармана во время работы, отсутствие дискеты.

Возникновение сигнала RELOAD приводит к принудитель-

ной установке сигнала TR. Сигнал RELOAD сбрасывается

при записи в регистр таймера, если к этому времени

восстановился сигнал READY (D11.5, D7.3, D17.1,

D33).

OP-FAILED – аварийное прекращение операции. Устанавливается при

появлении сигнала RELOAD во время выполнения опера-

ции чтения-записи. Удерживается до конца дорожки

(D24.3, D33).

LOST-DATA – потеря данных. Устанавливается, если от момента по-

явления сигнала TR до операции обмена прошло более

64 мкс. Сбрасывается по команде RUN (пуск). (D29.1,

D26.2, D33).

Сигналы накопителя INDEX (индекс), TR00 (дорожка 0), WRPRT

(защита записи) транслируются схемой в регистр состояния (D11.1-3,

D16, D33).

Схема управления накопителем предназначена для формирования

сигналов, подаваемых на накопитель. Состоит из регистра управления

(D14, D19), дешифратора номера привода (D36), формирователя им-

пульса шага (D15.1?, выходных усилителей (D35) и схемы отключения

мотора накопителя.

Регистр управления хранит код номера накопителя, код поверхности,

содержит разряд управления включением мотора и два разряда кода опе-

рации (чтение, запись, шаг вперед, шаг назад). Содержимое регистра

управления может быть прочитано процессором (формирователь D20).

Дешифратор номера привода преобразует двоичный код из соотвест-

вующих разрядов регистра управления в унитарный код.

Формирователь импульсов при записи "1" в 0-й разряд регистра со-

стояния вырабатывает сигнал STEP (шаг) длительностью около 1 мкс, ес-

ли в регистре записан код операции "шаг вперед" или "шаг назад". В

противном случае вырабатывается импульс RUN начала операции чтения-

записи, используемый внутри схемы контроллера.

Схема автоматического отключения мотора привода состоит из за-

дающего генератора частоты около 1 Гц (D7.1, D7.2) и счетчика-де-

лителя на 8 (D9). Обращение к любому из регистров контроллера сбра-

сывает счетчик в "0". При отсутствии обращения к контроллеру в тече-

ние 8 с на выходе счетчика формируется сигнал, сбрасывающий разряд

управления мотором в регистре управления.

Интерфейс Q-шины предназначен для поддержания протокола обмена

с процессором. Реализован на БИС селектора адреса (D1) и двунаправ-

ленного формирователя (D2). Элементы D3, D4, D6 формируют сигналы

чтения и записи логических регистров контроллера.

Таймер предназначен для отсчета времени с дискретностью 3 мс.

Таймер состоит из одновибратора (D15.2), запускаемого по записи

в регистр таймера. Состояние одновибратора можно прочитать (D23)

в нулевом разряде регистра контроллера.

С точки зрения программиста КНГМД представляет собой четыре ре-

гистра, доступных по чтению и записи. КОнтроллер рассчитан только на

программный обмер наддыми и программный опрос бита требования пере-

дачи TR. Цикл обмена данными в режиме чтения – записи не должен пре-

вышать 64 мкс. Формат регистра данных – 1 байт.

Форматы и адреса регистров контроллера:

разряды доступны по: ЧТЕНИЮ ЗАПИСИ

177100 – регистр состояния:

0 RELOAD RUN/STEP

1 - -

2 INDEX -

3 TR00/WRPRT -

4 - -

5 OP-FAILED -

6 LOST-DATA -

7 TR -

8-15 - -

177102 – регистр данных:

0-7 ДАННЫЕ ЧТЕНИЯ ДАННЫЕ ЗАПИСИ

8-15 - -

177104 – регистр управления:

0-1 НОМЕР ПРИВОДА

2 НОМЕР ПОВЕРХНОСТИ

3 ВКЛЮЧЕНИЕ МОТОРА

4-5 КОД ОПЕРАЦИИ

6-15 -

177106 – регистр таймера:

0 ПУСК ТАЙМЕРА СОСТОЯНИЕ ТАЙМЕРА

1-15 -

Контроллер выполняет также неявные операции:

сброс бита RELOAD по записи в регистр управления или

таймера;

прекращение текущей операции с дорожкой по записи в регистр

состояния.

Бит RELOAD принимает значение "1", если возникла ситуация,

когда накопитель не готов к работе (например, при смене дискеты),

т.е. накопителем был снят сигнал READY. Случаи возникновения подоб-

ной ситуации, а также время установления сигнала READY описаны в ТД

на используемый накопитель.

Бит INDEX отражает состояние сигнала INDEX накопителя. Прини-

мает значение "0", если в момент чтения индексное отверстие дискеты

проходит под фотодатчиком накопителя. Бит INDEX можно использовать

для проверки скорости вращения шпинделя накопителя.

Бит TR00/WRPRT в зависимости от кода операции, записанного в

регистре управления, отражает состояние сигналов накопителя:

TR00 (дорожка 0), если код операции ШАГ НАЗАД;

WRPRT (защита записи), если код операции ЗАПИСЬ.

В обоих случаях "0" обозначает активность соответствующего

сигнала.

Бит LOST-DATA устанавливается в "1", если цикл обмена данными

в операции чтения-записи превысил 64 мкс. Сбрасывается по началу

следующей операции. Поскольку информационная часть дорожки заканчи-

вается раньше индексного отверстия (физического конца), бит LOST-DATA

должен быть прочитан сразу же после чтения последнего информацион-

ного байта.

Бит OP-FAILED устанавливается в "1", если при выполнении опе-

рации чтения-записи исчезла готовность накопителя. При этом контрол-

лер переводится в режим ЧТЕНИЕ. Бит сбрасывается автоматически по

окончании текущей дорожки.

Бит TR синхронизирует обмен данными с накопителем. Установлн

в "1" всегда при операциях ШАГ ВПЕРЕД и ШАГ НАЗАД, а также при

возникновении ошибок чтения-записи (LOST-DATA или OP-FAILED). При

выполнении операции ЧТЕНИЕ бит TR устанавливается первый раз, ког-

да контроллер находит маркер дорожки, при этом код маркера передает-

ся в регистр данных. Сбрасывается при чтении регистра данных. Далее

бит TR устанавливается на каждый прочитанный байт вплоть до физичес-

кого конца дорожки. При выполнении операции ЗАПИСЬ после выдачи

команды RUN (пуск операции) бит TR сбрасывается до физического на-

чала дорожки. Далее TR устанавливается на каждый требуемый для за-

писи байт. Сбрасывайте по записи в регистр данных.

Запись "1" в бит RUN/STEP при установленном коде операции

ЧТЕНИЕ или ЗАПИСЬ запускает соответствующую операцию. Операция

должн быть завершена записью "0" в этот бит. Если установлен код

операции ШАГ ВПЕРЕД или ШАГ НАЗАД, запись "1" в бит RU/STEP

приведет к формированию импульса шага на линии STEP контроллера.

Направление DIRECT определяется кодом операции.

Несмотря на то, что регистр данных доступен по чтению и записи,

читаемая из этого регистра информация не соответствует записанной.

Номера накопителей 0...3.

Нижняя поверхность дискеты имеет номер 0.

Запись "1" в 3-й разряд регистра управления активизирует линию

MOTORON накопителя. Разряд автоматически сбрасывается, если к конт-

роллеру не было обращения в течение 6..10 секунд.

Разряды [5,4] регистра управления определяются следующими ко-

дами операций:

00 – ЧТЕНИЕ дорожки;

10 – ЗАПИСЬ дорожки;

01 – ШАГ НАЗАД (от центра дискеты);

11 – ШАГ ВПЕРЕД (к цендру дискеты).

При установке бита RELOAD или сигнала сброса канала ЭВМ код

текущей операции может быть изменен.

Любая запись в регистр таймера запускает одновибратор. В тече-

ние 3...3.5 мс после записи бит 0 регистра таймера установлен в "1".

...

7. МАРКИРОВАНИЕ И ПЛОМБИРОВАНИЕ

...

8. ОБЩИЕ УКАЗАНИЯ ПО ЭКСПЛУАТАЦИИ

...

9. УКАЗАНИЯ МЕР БЕЗОПАСНОСТИ

...

10. ПОДГОТОВКА К РАБОТЕ

...

11. ПОРЯДОК РАБОТЫ

...

12. ПРОВЕРКА ТЕХНИЧЕСКОГО СОСТОЯНИЯ

...

13. ХАРАКТЕРНЫЕ НЕИСПРАВНОСТИ И МЕРЫ ИХ УСТРАНЕНИЯ

...

14. ТЕХНИЧЕСКОЕ ОБСЛУЖИВАНИЕ

...

15. ПРАВИЛА ХРАНЕНИЯ И ТРАНСПОРТИРОВАНИЯ

...