К588/Гришин: различия между версиями

Nzeemin (обсуждение | вклад) |

Panther (обсуждение | вклад) (категория) |

||

| (не показана 1 промежуточная версия 1 участника) | |||

| Строка 42: | Строка 42: | ||

=== 6.2. МИКРОСХЕМА К588ВУ2 (КР588ВУ2) === | === 6.2. МИКРОСХЕМА К588ВУ2 (КР588ВУ2) === | ||

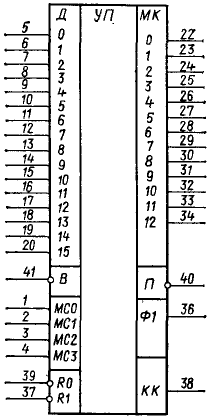

[[Файл:Grishin-6-1.png|210px|thumb|Рис. 6.1. Условное графическое обозначение микросхемы К588ВУ2]] | [[Файл:Grishin-6-1.png|210px|thumb|Рис. 6.1. Условное графическое обозначение микросхемы К588ВУ2]] | ||

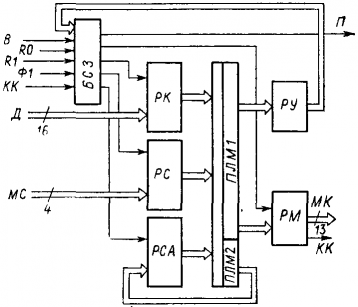

[[Файл:Grishin-6-2.png|358px|thumb|Рис. 6.2. Структурная схема микросхемы К588ВУ2]] | |||

Представляет управляющую память микрокоманд (УП). Основой УП являются программируемые логические матрицы ПЛМ. Программирование УП выполняют на за воде-изготовителе масочным способом. В настоящее время выпускают семь типов УП — К588ВУ2-0001 … К588ВУ2-0007. Кодировки микросхем УП полностью реализуют систему команд микроЭВМ «Электроника-60» | Представляет управляющую память микрокоманд (УП). Основой УП являются программируемые логические матрицы ПЛМ. Программирование УП выполняют на за воде-изготовителе масочным способом. В настоящее время выпускают семь типов УП — К588ВУ2-0001 … К588ВУ2-0007. Кодировки микросхем УП полностью реализуют систему команд микроЭВМ «Электроника-60» | ||

и операции расширенной арифметики. К последним относятся команды умножения, деления, сдвига. Кодировка К588ВУ2-0005 содержит микропрограммы работы микросхемы системного контроллера. | и операции расширенной арифметики. К последним относятся команды умножения, деления, сдвига. Кодировка К588ВУ2-0005 содержит микропрограммы работы микросхемы системного контроллера. | ||

На рис. 6.1 и 6.2 изображены соответственно условное графическое обозначение и структурная схема БИС УП. В табл. 6.2 дано назначение выводов этой микросхемы. | На рис. 6.1 и 6.2 изображены соответственно условное графическое обозначение и структурная схема БИС УП. В табл. 6.2 дано назначение выводов этой микросхемы. | ||

| Строка 151: | Строка 150: | ||

блок синхронизации БСЗ; вырабатывает управляющие сигналы записи во внутренние регистры БИС УП и сигнал квитирования П, свидетельствующий об окончании приема команды. На БСЗ поступают разряды регистра РУ. | блок синхронизации БСЗ; вырабатывает управляющие сигналы записи во внутренние регистры БИС УП и сигнал квитирования П, свидетельствующий об окончании приема команды. На БСЗ поступают разряды регистра РУ. | ||

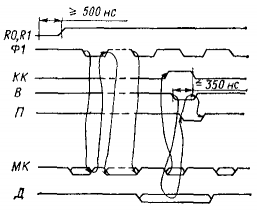

: Рис. 6.3. Временная диаграмма работы микросхемы К588ВУ2 | [[Файл:Grishin-6-3.png|257px|thumb|Рис. 6.3. Временная диаграмма работы микросхемы К588ВУ2]] | ||

Функционирование БИС УП начинается с подачи на входы R0 и R1 отрицательных сигналов, которые переводят БИС в исходное состояние. | Функционирование БИС УП начинается с подачи на входы R0 и R1 отрицательных сигналов, которые переводят БИС в исходное состояние. | ||

Длительность сигналов R0 и R1 не менее 500 нс. | Длительность сигналов R0 и R1 не менее 500 нс. | ||

| Строка 1299: | Строка 1297: | ||

46. Мильнер А. Д. и др. Принципы построения проблемно-ориентированного комплекса для программирования МП-устройств и система отладки на его базе // Машинное моделирование. М.: МДНТП им. Ф. Э. Дзержинского, 1980. С. 83—91. | 46. Мильнер А. Д. и др. Принципы построения проблемно-ориентированного комплекса для программирования МП-устройств и система отладки на его базе // Машинное моделирование. М.: МДНТП им. Ф. Э. Дзержинского, 1980. С. 83—91. | ||

[[Категория:Микропроцессорные комплекты]] | |||

Текущая версия от 10:40, 26 марта 2024

Глава 6

МИКРОПРОЦЕССОРНЫЙ КОМПЛЕКТ СЕРИИ К588 (КР588)

6.1. ОБЩИЕ СВЕДЕНИЯ

Микропроцессорный комплект серии К588 создан на базе КМОП-технологии и предназначен для построения аппаратуры средней производительности. Отличительными особенностями микросхем комплекта являются малое потребление мощности от источника питания, асинхронный принцип обмена информацией, а также широкий набор периферийных БИС комплекта. В состав БИС комплекта входят, в частности, БИС управляющей памяти, кодировки которых полностью реализуют систему команд микроЭВМ «Электроника-60» и операции расширенной арифметики. Однако комплект серии К588 может реализовывать устройства не только с этой системой команд. Пользователь строит собственную микропрограммную память, реализующую практически любую систему команд [9, 34, 45, 46].

Микросхемы комплекта обеспечивают выходные сигналы, соответствующие уровням сигналов ТТЛ-микросхем. Однако ввиду того, что входные напряжения сигналов «1» микросхем комплекта превышают нижнюю границу ТТЛ-сигналов, стыковку по входам можно обеспечить ТТЛ-микросхемами с открытым коллектором и нагрузочными резисторами.

В состав комплекта входят БИС системного контроллера для сопряжения устройства на базе микросхем комплекта с каналом типа Q-шина, БИС аппаратного умножителя, магистрального приемопередатчика, буферного регистра, контроллера ЗУ и селектора адреса. Состав комплекта приведен в табл. 6.1.

| Тип микросхемы | Назначение | Краткая характеристика | Тип корпуса |

|---|---|---|---|

| К588ВУ2 (КР588ВУ2) | Управляющая память | Время цикла ≤ 0,8 мкс; Pccs ≤ 0,5 мВт; Pcc ≤ 20 мВт; 12-разрядная микрокоманда; число БИС — 7 |

429.42-3 (2206.42-2) |

| К588ВС2 (КР588ВС2) | Арифметическое устройство | Время цикла (среднее) ≤ 1,82 мкс; Pccs ≤ 1 мВт; Pcc ≤ 30 мВт; 16-разрядное | |

| К588ВГ1 (КР588ВГ1) | Системный контроллер | Время выдачи адреса ≤ 150 нс; Pccs ≤ 0,5 мВт; Pcc ≤ 15,0 мВт | |

| К588ВР2 | Умножитель | Время умножения ≤ 2,0 мкс; Pccs ≤ 5,0 мВт; Pcc ≤ 35,0 мВт 16-разрядный |

4118.24-2 |

| К588ВА1 (КР588ВА1) | Магистральный приемо-передатчик | Время передачи ≤ 150 нс; Pccs ≤ 0,50 мВт; Pcc ≤ 25,0 мВт 8-разрядный |

4119.28-4 (2121.28-4) |

| К588ИР1 (КР588ИР1) | Многофункциональный буферный регистр | Время записи ≤ 100 нс; Время считывания ≤ 150 нс; Pccs ≤ 0,3 мВт; Pcc ≤ 10,0 мВт 8-разрядный | |

| К588ВГ2 (КР588ВГ2) | Контроллер запоминающего устройства | Время выборки ≤ 200 нс; Pccs ≤ 0,3 мВт; Pcc ≤ 10,0 мВт |

4116.18-2 (2107.18-1) |

| К588ВТ1 | Селектор адреса | Время выборки ≤ 300 нс; Pccs ≤ 2,5 мВт; Pcc ≤ 30 мВт |

429.42-3 |

Микросхемы комплекта обладают высокой помехоустойчивостью.

Комплект серии К588 (КР588) служит для построения систем управления периферийными устройствами. В основном его используют в устройствах, действующих в условиях сильных электромагнитных полей, в аппаратуре, работающей в режиме длительного автономного плавания и др.

Микросхемы выпускают в корпусах с горизонтальным (К588) и вертикальным (КР588) расположением выводов. Электрические параметры, а также функциональные возможности микросхем с индексами К и КР идентичны.

6.2. МИКРОСХЕМА К588ВУ2 (КР588ВУ2)

Представляет управляющую память микрокоманд (УП). Основой УП являются программируемые логические матрицы ПЛМ. Программирование УП выполняют на за воде-изготовителе масочным способом. В настоящее время выпускают семь типов УП — К588ВУ2-0001 … К588ВУ2-0007. Кодировки микросхем УП полностью реализуют систему команд микроЭВМ «Электроника-60» и операции расширенной арифметики. К последним относятся команды умножения, деления, сдвига. Кодировка К588ВУ2-0005 содержит микропрограммы работы микросхемы системного контроллера.

На рис. 6.1 и 6.2 изображены соответственно условное графическое обозначение и структурная схема БИС УП. В табл. 6.2 дано назначение выводов этой микросхемы.

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1 | Магистраль состояния | 0 | МС0 | Вход |

| 2 | 1 | МС1 | ||

| 3 | 2 | МС2 | ||

| 4 | 3 | МС3 | ||

| 5 | Шина команд | 0 | Д0 | |

| 6 | 1 | Д1 | ||

| 7 | 2 | Д2 | ||

| 8 | 3 | Д3 | ||

| 9 | 4 | Д4 | ||

| 10 | 5 | Д5 | ||

| 11 | 6 | Д6 | ||

| 12 | 7 | Д7 | ||

| 13 | 8 | Д8 | ||

| 14 | 9 | Д9 | ||

| 15 | 10 | Д10 | ||

| 16 | 11 | Д11 | ||

| 17 | 12 | Д12 | ||

| 18 | 13 | Д13 | ||

| 19 | 14 | Д14 | ||

| 20 | 15 | Д15 | ||

| 21 | Общий | — | GND | — |

| 22 | Магистраль микрокоманд | 0 | МК0 | Вход |

| 23 | 1 | МК1 | ||

| 24 | 2 | МК2 | ||

| 25 | 3 | МК3 | ||

| 26 | 4 | МК4 | ||

| 27 | 5 | МК5 | ||

| 28 | 6 | МК6 | ||

| 29 | 7 | МК7 | ||

| 30 | 8 | МК8 | ||

| 31 | 9 | МК9 | ||

| 32 | 10 | МК10 | ||

| 33 | 11 | МК11 | ||

| 34 | 12 | МК12 | ||

| 35 | Не используется | — | — | — |

| 36 | Завершение выполнения микрокоманды | — | Ф1 | Вход |

| 37 | Установка | 1 | R1 | |

| 38 | Конец команды | — | КК | Вход-выход |

| 39 | Установка | 0 | R0 | Вход |

| 40 | Команда принята | — | П | Выход |

| 41 | Команда выдана | — | В | Вход |

| 42 | Напряжение питания | — | Ucc | — |

В состав структурной схемы БИС УП входят следующие функциональные узлы:

регистр команд РК; принимает команду по шине команд Д;

программируемые логические матрицы ПЛМ1 и ПЛМ2; в них запрограммированы не только информация о выбираемой микрокоманде и адрес следующей микрокоманды, но и разряды, управляющие внутренними узлами БИС УП;

регистры состояния PC и следующего адреса РСА; принимают соответственно признаки результата выполнения операции и адрес следующей микрокоманды. Информация состояния поступает, как правило, из арифметического устройства и включает 4-разрядное слово-состояние, состоящее из признаков нулевого результата, переполнения, переноса из старшего знакового разряда (Z, V, С, N);

регистры управления РУ и микрокоманд РМ;

блок синхронизации БСЗ; вырабатывает управляющие сигналы записи во внутренние регистры БИС УП и сигнал квитирования П, свидетельствующий об окончании приема команды. На БСЗ поступают разряды регистра РУ.

Функционирование БИС УП начинается с подачи на входы R0 и R1 отрицательных сигналов, которые переводят БИС в исходное состояние. Длительность сигналов R0 и R1 не менее 500 нс.

Работа микросхемы УП начинается по положительному фронту сигнала R0 (либо R1). По отрицательному сигналу В происходит прием команды во входной регистр РК, а также информации состояния в регистр PC. После приема этой информации БИС УП выдает отрицательный сигнал П, свидетельствующий о том, что команда принята. Отрицательный фронт сигнала П инициирует положительный фронт сигнала В, который, в свою очередь, сбрасывает сигнал П в состояние «1».

Затем начинается выдача первой микрокоманды принятой команды. Положительный фронт сигнала Ф1 инициирует выдачу очередной микрокоманды на магистраль МК. Микрокоманда может находиться на магистрали до отрицательного фронта сигнала Ф1. После этого происходит «подброс в единицу» магистрали МК. Если к этому времени сформирована следующая микрокоманда, то происходит ее запись в РМ с последующей выдачей. Одновременно с выдачей последней микрокоманды текущей команды выдается сигнал КК, сигнализирующий контроллеру (либо внешнему ЗУ) о необходимости подачи новой команды.

На рис. 6.3 приведена временная диаграмма работы БИС УП.

Реализация всей системы команд микроЭВМ «Электроника-60» и ограниченные возможности внутренних ПЛМ БИС УП привели к необходимости использования не менее пяти «зашивок» микрокоманд в БИС УП (0001 … 0005). Первые четыре реализуют собственно команды «Электроники-60», пятая — управляет системным контроллером и разрешением прерываний. Четыре микросхемы БИС УП (0001 … 0004) соединяются параллельно (по выходам) и выдают информацию в арифметическое устройство (АУ); 12-разрядный код является собственно микрокомандой для АУ. Разряд 12 используется в качестве строба микрокоманды. Микросхема К588ВУ2-0005 разрядами 0…6 вырабатывает сигналы разрешения прерывания, разряды 7…12 управляют микросхемой К588ВГ1 (КР588ВГ1).

В табл. 6.3 приведены основные электрические параметры БИС УП.

| Параметр, единица измерения | Обозначение | Значение |

|---|

6.3. МИКРОСХЕМА К588ВС2 (КР588ВС2)

Представляет БИС 16-разрядного арифметического устройства (БИС АУ). БИС АУ предназначена для построения процессоров микроЭВМ, а также центральных устройств обработки программируемых контроллеров.

БИС АУ осуществляет обмен информацией с внешними устройствами по 16-разрядной двунаправленной магистрали данных. Операции обмена информацией сопровождаются сигналами квитирования. Микросхема реализует асинхронную дисциплину обмена.

Назначение выводов БИС АУ представлено в табл, 6.4. Условное графическое обозначение и структурная схема БИС АУ изображены соответственно на рис. 6.4 и 6.5. В состав структурной схемы БИС АУ входят следующие функциональные узлы:

регистр микрокоманд РМ и дешифратор ДШ; предназначены для приема и дешифрации кода микрокоманды;

буферный регистр данных БРг; через БРг осуществляют связь между внутренней шиной данных ВШД и внешней магистралью данных Д;

арифметико-логическое устройство АЛУ (16-разрядное); в нем происходят основные действия, связанные с арифметико-логической обработкой данных. Прием информации в АЛУ, а также ее выдача осуществляются через ВШД;

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1 | Шина микрокоманд | 7 | МК7 | Вход |

| 2 | 8 | МК8 | ||

| 3 | 9 | МК9 | ||

| 4 | 10 | МК10 | ||

| 5 | Магистраль данных | 0 | Д0 | Вход-выход |

| 6 | 1 | Д1 | ||

| 7 | 2 | Д2 | ||

| 8 | 3 | Д3 | ||

| 9 | 4 | Д4 | ||

| 10 | 5 | Д5 | ||

| 11 | 6 | Д6 | ||

| 12 | 7 | Д7 | ||

| 13 | 8 | Д8 | ||

| 14 | 9 | Д9 | ||

| 15 | 10 | Д10 | ||

| 16 | 11 | Д11 | ||

| 17 | 12 | Д12 | ||

| 18 | 13 | Д13 | ||

| 19 | 14 | Д14 | ||

| 20 | 15 | Д15 | ||

| 21 | Общий | — | GND | — |

| 22 | Знак результата | — | N | Выход |

| 23 | Признак нулевого результата | — | Z | |

| 24 | Признак переполнения | — | V | |

| 25 | Перенос | — | C | |

| 26 | Не используются | — | — | — |

| 27 | — | — | — | |

| 28 | — | — | — | |

| 29 | — | — | — | |

| 30 | Строб микрокоманды | — | ВК | Вход |

| 31 | Завершение выполнения макрокоманды | — | Ф1 | Выход |

| 32 | Строб данных по магистрали Д | — | В | Вход-выход |

| 33 | Конец приема данных | — | П | |

| 34 | Шина микрокоманд | 0 | МК0 | Вход |

| 35 | 1 | МК1 | ||

| 36 | 2 | МК2 | ||

| 37 | 3 | МК3 | ||

| 38 | 4 | МК4 | ||

| 39 | 5 | МК5 | ||

| 40 | 6 | МК6 | ||

| 41 | 11 | МК11 | ||

| 42 | Напряжение питания | — | Ucc | — |

аккумулятор АКК и. блок регистров общего назначения БРОН; используют в качестве источников и приемников информации при выполнении микрокоманд;

регистр состояния PC; в PC заносятся признаки результата операции. Программно доступен, может участвовать в операциях АДУ;

блок синхронизации БСЗ; осуществляет обработку и выдачу внешних и внутренних сигналов управления. Работа БСЗ начинается с отрицательного фронта сигнала ВК;

- Рис. 6.4. Условное графическое обозначение микросхемы К588ВС2

- Рис. 6.5. Структурная схема микросхемы К588ВС2

буферный регистр состояния БРС; через БРС происходит выдача признаков результата операции;

внутренняя шина данных ВШД; обеспечивает связь между БРг, АЛУ, АКК, БРОН, PC.

6.3.1. Описание функционирования микросхемы К588ВС2

Работа БИС АУ осуществляется под управлением микрокоманды. Выполнение любой микрокоманды состоит из комбинации фаз приема, чтения, записи и выдачи.

Фаза приема включает прием и дешифрацию микрокоманды. В некоторых микрокомандах в этой фазе происходит прием операнда по магистрали данных.

Фаза чтения включает чтение информации в АЛУ из БРОН, АКК, PC или БРг с последующей ее обработкой (рис. 6.6 … 6.9).

В фазе записи происходят завершение обработки информации и ее запись в приемник информации. Приемником может быть один из внутренних функциональных узлов БИС АУ — РОН, АКК, РС или БРг в соответствии с кодом микрокоманды.

В фазе выдачи осуществляется выдача результата операции в магистраль данных.

В табл. 6.5 … 6.8 приведены микрокоманды, выполняемые БИС АУ.

- Рис. 6.6.

- Рис. 6.7.

- Рис. 6.8.

- Рис. 6.9.

Начало выполнения всех микрокоманд одинаковое. Если БИС АУ готова к приему микрокоманды, то на выходе Ф1 (см. рис. 6.6 … 6.9) устанавливается сигнал «1». После этого БИС УП (либо другое устройство микропрограммного управления) выдает микрокоманды на шину микрокоманд МК 12-разрядным кодом (0…11); 12-й разряд шины микрокоманд, как правило, используется для стробирования микрокоманды и поступает на вход ВК сигналом «0». По отрицательному фронту этого сигнала происходит запись микрокоманды в регистр РМ и дешифратор ДШ. По окончании приема микрокоманды БИС АУ устанавливает сигнал «0» на выходе Ф1.

После этого БИС АУ переходит к исполнению микрокоманды.

Окончание выполнения микрокоманды инициируется положительным фронтом сигнала Ф1. Если микрокоманда выполняется без обмена, то не происходит ни приема операнда, ни выдачи результата операции в магистраль данных.

Выполнение микрокоманды с выдачей результата операции в магистраль данных обусловлена выдачей результата в магистраль совместно с формированием на выводе В сигнала «0». Одновременно с выдачей информации БИС АУ может принять следующую микрокоманду и начать ее выполнение. Этап выдачи информации в магистраль данных продолжается до поступления извне на вывод П БИС АУ отрицательного фронта сигнала. Последний инициирует положительный фронт сигнала В и снятие информации с магистрали данных. По положительному фронту сигнала В может сбрасываться сигнал П. На этом заканчивается выдача информации в магистраль. Если во время этапа ыдачи информации в магистраль данных поступила микрокоманда без обмена, то последняя выполняется независимо от того, закончился или нет этап обмена информации в предыдущей микрокоманде. Если данная микрокоманда с приемом информации и еще не закончился этап выдачи данных в предыдущей микрокоманде, то БИС АУ не устанавливает уровень «0» на выходе Ф1, а ожидает появления «0» на выводе П (окончания этапа выдачи). Если следующая микрокоманда с выдачей и еще не закончился этап выдачи информации в текущей микрокоманде, то после окончания выполнения фаз чтения и записи и выработки сигнала Ф1 = «1» БИС А У останавливается и ожидает сигнала П = «0». После появления этого сигнала сбрасывается сигнал В и после сброса сигнала П выдается новая информация в магистраль данных.

При выполнении микрокоманды с приемом информации по магистрали данных БИС АУ после приема и дешифрации кода этой микрокоманды переходит в режим ожидания приема операнда. Этап приема начинается с появления извне сигнала В = «0». Закончив прием, БИС АУ устанавливает сигнал П — «0» и сигнал Ф1 = «0». После этого внешнее устройство (источник операнда) сбрасывает сигнал В, после чего БИС АУ сбрасывает сигнал П.

Окончание выполнения микрокоманды сигнализируется сигналом Ф1 = «1». Микрокоманда с приемом операнда и выдачей результата операции аналогична микрокоманде с приемом информации из магистрали и фазой выдачи результата операции в магистраль данных.

| Разряды МК | Выполняемая операция | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | |

| 1 | 0 | КОП1 | РОН | АЛУ(РОН, АКК) -> РОН | ||||||

| X | X | X | X | |||||||

| 0 | 1 | X | X | X | X | АЛУ(РОН, АКК) -> АКК | ||||

| 0 | 0 | То же | АЛУ(РОН, АКК) -> РС | |||||||

| 1 | 1 | То же | АЛУ(РОН, АКК) -> АКК; БРг | |||||||

| 0 | 0 | X | 1 | 1 | 1 | X | X | X | X | Начальная установка |

| 0 | 1 | 0 | 1 | 1 | 1 | КОП2 | АЛУ(БРг, АКК) -> РС | |||

| X | X | X | X | |||||||

| 1 | 1 | 0 | 1 | 1 | 1 | X | X | X | X | АЛУ(БРг, АКК) -> БРг, АКК |

| 0 | 1 | 1 | 1 | 1 | 1 | КОП2 | АЛУ(РС, АКК) -> АКК | |||

| 1 | 0 | 1 | 1 | 1 | 1 | АЛУ(РС, АКК) -> РС | ||||

| 1 | 1 | 1 | 1 | 1 | 1 | АЛУ(РС, АКК) -> БРг, АКК | ||||

| Разряды МК | Выполняемая операция | |||

|---|---|---|---|---|

| 1 2 | 3 4 5 6 | 7 8 9 10 | 11 | |

| 0 X | КОП3 любой, кроме: X 1 0 1 X 1 1 1 |

РОН | X | АЛУ(РОН) -> РОН |

| 0 X | 0 1 0 1 | X | БРг -> РОН | |

| 1 0 | 0 | МК(7…10) -> АКК(0…3) | ||

| 1 0 | 1 | МК(7…10) -> АКК(4…7) | ||

| 1 1 | 0 1 0 1 | 0 | МК(7…10) -> АКК(8…11) | |

| 1 1 | 1 | МК(7…10) -> АКК(12…15) | ||

| 0 1 | 1 1 1 1 | КОП4 | — | АЛУ(РС) -> РС |

| 1 X | Любой КОП4, кроме 1 1 0 1 |

— | АЛУ(РС) -> БРг; РС | |

| 0 X | 1 1 0 1 | X | АЛУ(АКК) -> АКК | |

| 1 X | X | АЛУ(АКК) -> БРг; АКК | ||

| 0 X | 0 1 1 1 | КОП4 | X | АЛУ(БРг) -> АКК |

| 1 X | X | АЛУ(БП) -> АКК; БРг | ||

| Операция | КОП1(2) | Действие | Признаки | Примечание |

|---|

| Операция | КОП3(4) | Действие | Признаки | Примечание |

|---|

6.3.2. Система микрокоманд БИС АУ

Система микрокоманд БИС АУ (см. табл. 6.5 … 6.8) содержит бинарные (с двумя операндами) и унарные (с одним операндом) микрокоманды. При описании микрокоманд использованы следующие обозначения: МК — микрокоманда; РОН — регистр общего назначения; КОП — код операции; БРг — буферный регистр данных; АКК — аккумулятор; РС — регистр состояний; А, В — первый и второй операнды; ДД — приемник результата операции; С, N, Z, V — признаки результата; X — безразличное состояние разряда.

Все микрокоманды можно условно разделить на следующие типы: без обмена информацией с магистралью данных; с приемом операнда по магистрали данных; с выдачей операнда в магистраль данных; с приемом и выдачей результата в магистраль данных.

В БИС АУ четыре формата микрокоманд. Бинарные и унарные микрокоманды имеют по два формата.

Во всех форматах нулевой разряд используется как идентификатор бинарной (МКО = «0») или унарной (МКО = «1») операций.

Одиннадцатый разряд является признаком выдачи информации состояния на магистраль состояния.

Для бинарных микрокоманд в форматах 1 и 2 разряды МК1 и МК2 определяют адрес приемника.

Для унарных микрокоманд разряд МК1 в форматах 3 и 4 определяет адрес приемника, а МК2 — указывает длину операнда (байт либо два байта).

Для форматов 1 и 3 разряды МК3 … МК6 определяют код операций КОП1 и КОП3 соответственно.

Для форматов 2 и 4 эти разряды определяют признаки формата.

Для форматов 1 и 3 разряды МК7 … МК10 в двоичном коде определяют номер РОНа.

Для форматов 2 и 4 эти разряды определяют код операций КОП2 и КОП4 соответственно.

Широкий спектр микрокоманд позволяет реализовать на базе БИС АУ практически любую систему команд вычислительного устройства.

| Параметр, единица измерения | Обозначение | Значение |

|---|

На временных диаграммах (см. рис. 6.6 … 6.9) иллюстрируется работа БИС АУ при выполнении различных микрокоманд. Индексы В и П указывают, что данный сигнал является выдаваемым либо принимаемым в БИС АУ.

В заключение следует отметить, что при проектировании устройств на базе БИС АУ необходимо разряды магистрали состояния «подвязывать» через резистор к источнику питания.

Величина резистора В. определяется из формулы

- Формула (6.1)

В табл. 6.9 приведены электрические параметры БИС АУ.

6.4. МИКРОСХЕМА К588ВГ1 (КР588ВГ1)

Большая интегральная схема системного контроллера (БИС СК.) предназначена для согласования и сопряжения процессора на базе микросхем серии К588 (КР588) с каналом типа Q-шина. Назначение выводов БИС СК дано в табл. 6.10. На рис. 6.10 и 6.11 изображены соответственно условное обозначение и структурная схема БИС СК.

В состав структурной схемы БИС СК входят следующие функциональные узлы: блок прерываний БП, дешифратор микрокоманд ДШМ, блок управления обменом данных БУО, блок управления прямым доступом к памяти БУНД, блок правления магистральными приемопередатчиками БУПП, блок синхронизации БСЗ.

Следует отметить, что линии управления обменом ЛУО включают следующие сигналы обмена (см. рис. 6.11): ОБМ, ДЧТ, ДЗП, ПЗП, ОТВ, ЗПР, ПРР и ПВС.

Линии передачи управления ЛПУ включают сигналы ЗМ, РЗМ и ПЗ (см. рис. 6.11).

БИС СК предназначена для связи внутреннего интерфейса процессора, построенного на базе микросхем серии К588 (КР588), с внешним стандартным интерфейсом канала Q-шина.

Внутренний интерфейс процессора содержит сигналы, обеспечивающие работу процессора, состоящего из магистральных приемопередатчиков, управляющей памяти и арифметического устройства. Это сигналы квитирования БИС АУ и БИС УП, 16-разрядная информационная магистраль, 4-разрядная магистраль кода прерывания, сигналы управления магистральными приемопередатчиками. Сигналы квитирования КВ1 … КВЗ и КП обеспечивают передачу информации по 16-разрядной магистрали. Информация может включать команду, данные, адрес, вектор прерывания. Магистраль кода прерывания ПРЗ … ПРО служит для сообщения в УП о том, какое прерывание в данный момент обслуживается.

Сигналы управления приемопередатчиками С1 и С2 предназначены для организации двунаправленного обмена информацией через МПП.

- Рис. 6.10. Условное графическое обозначение микросхемы К588ВГ1

- Рис. 6.11. Структурная схема микросхемы К588ВГ1

Внешний интерфейс процессора содержит сигналы, обеспечивающие работу всех устройств канала. Это информационные шины, шины управления вводом-выводом, шины прерываний и шины прямого доступа к памяти. Сигналы на шинах ввода-вывода ОБМ, ДЧТ, ДЗП, ПЗП, ОБМ обеспечивают передачу по двунаправленной шине данных Д15 … ДО команд, адресов, данных и векторов прерываний.

Шины и сигналы прерываний ЗПРЗ…ЗПР0, ОСТ, АИП, ЗПР, ПРР, ЛВС служат для приема запросов на прерывание и для сброса прерываний от внешних устройств.

Шины прямого доступа ЗМ, РЗМ, ПЗ служат для приема запросов на прямой доступ к памяти и сброса этих запросов.

Сигнал УСТ служит для приведения системы в исходное состояние, КОШ — вывод для подключения внешней времязадающей цепи для формирования длительности сигналов УСТ, ДЧТ или ДЗП.

БИС СК управляется микрокомандно. В табл. 6.11 приведена система микрокоманд БИС СК. Код микрокоманды поступает на входы МК4 … МКО.

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1 | Регистр состояния | T | T | Вход |

| 2 | P | P | ||

| 3 | Подключение времязадающей цепи | — | КОШ | |

| 4 | Шина прерывания | 3 | ПР3 | Выход |

| 5 | 2 | ПР2 | ||

| 6 | 1 | ПР1 | ||

| 7 | 0 | ПР0 | ||

| 8 | Начальная установка | — | R | |

| 9 | Квитирование выдачи | 1 | КВ1 | Вход-выход |

| 10 | 2 | КВ2 | Выход | |

| 11 | 3 | КВ3 | ||

| 12 | Квитирование приема | — | КП | Вход-выход |

| 13 | Шина микрокоманд | 4 | МК4 | Вход |

| 14 | 3 | МК3 | ||

| 15 | 2 | МК2 | ||

| 16 | 1 | МК1 | ||

| 17 | 0 | МК0 | ||

| 18 | Строб микрокоманды | — | ВК | |

| 19 | Квитирование приема микрокоманды | — | Ф1 | Выход |

| 20 | Начальный пуск | — | НП | Вход |

| 21 | Общий | — | GND | — |

| 22 | Сброс канала | — | УСТ | Выход |

| 23 | Линии управления обменом | 3 | ЛУО3 | |

| 24 | 0 | ЛУО0 | ||

| 25 | 1 | ЛУО1 | ||

| 26 | 2 | ЛУО2 | ||

| 27 | 4 | ЛУО4 | ||

| 28 | 5 | ЛУО5 | Вход | |

| 29 | 6 | ЛУО6 | Выход | |

| 30 | Внешний сигнал прерывания | — | АИП | Вход |

| 31 | Запрос прерывания с фиксированными векторами | 0 | ЗПР0 | |

| 32 | 3 | ЗПР3 | ||

| 33 | 2 | ЗПР2 | ||

| 34 | 1 | ЗПР1 | ||

| 35 | Линии управления обменом | 7 | ЛУО7 | |

| 36 | Внешний сигнал прерывания | — | ОСТ | |

| 37 | Линии передачи управления | 1 | ЛПУ1 | Выход |

| 38 | 2 | ЛПУ2 | Вход | |

| 39 | 0 | ЛПУ0 | ||

| 40 | Управление приемопередатчиком | 1 | С1 | Выход |

| 41 | 2 | С2 | ||

| 42 | Напряжение питания | — | Uco | — |

| Восьмерич- ный код |

Обозначение | Назначение |

|---|---|---|

| 00 | INIT | Инициализация работы БИС СК |

| 01 | LPSW | Загрузка слова состояния программы |

| 02 | DATIV | Ввод вектора прерывания |

| 03 | WAIT | Ожидание |

| 04 | IE | Разрешение прерывания |

| 05 | ID | Запрет прерывания |

| 10 | DATI | Ввод слова |

| 11 | DATIK | Ввод команды |

| 12 | DATO | Вывод слова |

| 13 | DATOB | Вывод байта |

| 14 | DATIO | Ввод-вывод слова |

| 15 | DATIOB | Ввод-вывод байта |

| 20 | RTO | Сброс прерывания INTO |

| 21 | NH | Запрет прерывания HALT |

| 22 | RT1 | Сброс прерывания INT1 |

| 23 | RT2 | Сброс прерывания INT2 |

| 24 | RT3 | Сброс прерывания INT3 |

| 25 | RH | Сброс прерывания HALT |

| 26 | RTM | Сброс триггера маски |

| 27 | RES | Начальная установка |

| 30 | RTE | Сброс триггера ошибки |

| 31 | RTP | Сброс триггера РОК |

| 32 | CTO | Очистка триггера ТО |

| 33 | NTI | Запрет прерывания |

| 34 | REV | Сброс триггера |

| 37 | NOP | Нет операции |

Рассмотрим выполнение трех микрокоманд, управляющих процессами ввода и вывода информации.

Микрокоманда ввода команды DАТІК (рис. 6.12) выполняется следующим образом.

На вывод КВ1 подается сигнал из БИС АУ о том, что на магистрали данных находится адрес команды. По этому сигналу БИС СК устанавливает сигналы разрешения обмена ОБМ = «0» и чтения данных ДЧТ = «0» для ОЗУ, а также разрешает БИС АУ снять с магистрали данных адрес команды, выдав сигнал КП = «О».

После снятия адреса команды БИС АУ выдает сигнал на вывод КВ1 = «1», на что БИС СК отвечает сигналом КП = «1».

Затем на вывод ОСТ подается сигнал «0», свидетельствующий о том, что на магистрали данных находится команда и БИС СК разрешает УП принять команду. Кроме этого, при отсутствии запросов на прерывание БИС СК выдает сигналы КВ2 = КВЗ = «0». Если к данному моменту запрос на прерывание поступит, то БИС СК вырабатывает сигнал КВЗ = «0».

После приема команды БИС УП отвечает сигналом КП = «0», по которому БИС СК вырабатывает сигналы КВ2 — КВЗ = «1», а также сигнал ДЧТ — «1».

После снятия сигнала ОСТ (ОСТ = «1») БИС СК снимает сигнал ОБМ (ОБМ = «1»).

Выполнение микрокоманды ввода данных ОАТІ (рис. 6.13) начинается с подачи из БИС А У на БИС СК сигнала КВ1 = «0», который свидетельствует о том, что адрес данных находится на магистрали.

По этому сигналу БИС СК устанавливает сигналы ОБМ = «0», ДЧТ = «0» (для ОЗУ или ВУ). Затем, после задержки относительно сигнала ОБМ, БИС СК устанавливает сигнал КП = «0», который разрешает снять адрес с магистрали данных. После этого АУ вырабатывает сигнал КВ1 = «1», по которому БИС СК устанавливает сигнал КП = «1».

- Рис. 6.12. Временная диаграмма выполнения микрокоманды DАТІК

- Рис. 6.13. Временная диаграмма выполнения микрокоманды DАТІ

На БИС СК подается сигнал ОСТ = «0» (данные находятся на магистрали). По этому сигналу БИС СК устанавливает сигнал КВ1 = «0», разрешая БИС АУ принять данные. После окончания приема данных БИС АУ вырабатывает сигнал КП = «0». Вслед за этим БИС СК сбрасывает сигналы КВ1 и ДЧТ в состояние «1». Получив сигнал ОСТ = «1», БИС СК вырабатывает сигнал ОБМ = «1».

| Двоичный код |

Мнемокод | Содержание прерываний |

|---|---|---|

| 1 0 1 0 | W (DBE) | Начальный пуск (двойная ошибка канала) |

| 1 1 1 0 | T (TERR0) | Прерывание по T-разряду |

| 1 1 1 1 | POK (TERR1) | Прерывание по сбою питания (ошибка канала) |

| 0 1 1 1 | HALT (TERR2) | Прерывание по входу ОСТ (ошибка канала) |

| 0 1 0 1 | INT0 | Запрос прерывания 0 от ВУ |

| 0 1 0 0 | INT1 | То же . . . 1 |

| 0 1 1 0 | INT2 | » . . . . . 2 |

| 0 0 1 0 | INT3 | » . . . . . 3 |

| 0 0 0 1 | IRQ | Запрос прерывания от ВУ с нефиксированным вводимым адресом-вектором |

| 0 0 0 0 | Нет прерывания | Нет прерывания |

Выполнение микрокоманды вывода данных ОАТО (рис. 6.14) начинается с подачи из БИС АУ на БИС СК сигнала КВ1 = «0», свидетельствующего о том, что на магистрали находится адрес данных. Поэтому сигналу БИС СК станавливает сигналы ОБМ = ПЗП = «0» (для ОЗУ или ВУ). Затем с некоторой задержкой относительно сигнала ОБМ БИС СК устанавливает сигнал КП = «0». Последний разрешает БИС АУ снять адрес данных, после чего БИС АУ вырабатывает сигнал КВ1 = «1». По этому сигналу БИС СК отвечает сигналами ПЗП = КП = «1».

АУ выставляет на магистраль данные, сигнализируя об этом сигналом КВ1 = «0», по которому БИС СК устанавливает сигнал ДЗП = «0» (для ОЗУ или ВУ). После того, как данные запишутся в ОЗУ (ВУ) на БИС СК подается сигнал ОСТ = «0». По этому сигналу БИС СК вырабатывает сигналы ДЗП = «1» и КП = «0». Получив сигнал КП = «0», БИС АУ снимает данные с магистрали и устанавливает сигнал КВ1 = «1», по которому БИС СК формирует сигнал КП = «1». По сигналу сигнал ОБМ = «1».

- Рис. 6.14. Временная диаграмма выполнения микрокоманды DATO

В табл. 6.12 приведена расшифровка кодов, вырабатываемых БИС СК на выводах ПРЗ … ПРО.

Электрические параметры БИС СК приведены в табл. 6.13.

При разработке схемы с использованием БИС СК подключение времязадающей РС-цепочки к выводу КОШ осуществляется следующим образом: резистор R — между питанием и выводом КОШ; конденсатор С — между выводом КОШ и «минусом» источника питания. Значения резистора и конденсатора подбираются из условия обеспечения нужной длительности сигналов ДЧТ, ДЗП, до сигнала ОТВ.

| Параметр, единица измерения | Обозначение | Значение |

|---|

6.5. МИКРОСХЕМА К588ВР2

Представляет собой БИС умножителя (БИС УМ) и выполняет операции умножения над 16-разрядными операндами в дополнительном коде.

На рис. 6.15 и 6.16 приведены условное графическое обозначение и структурная схема БИС УМ. Назначение выводов БИС УМ дано в табл. 6.14.

- Рис. 6.15. Условное графическое обозначение микросхемы К588ВР2

- Рис. 6.16. Структурная схема микросхемы К588ВР2

В состав структурной схемы БИС УМ входят следующие функциональные узлы:

блок синхронизации БСЗ предназначены для приема и обработки управляющих сигналов. БСЗ служит также для организации цикла выполнения операции умножения;

регистры операндов А и В — РА и РВ служат для приема, хранения и выдачи в блок умножения множимого и множителя;

регистры произведения РП1 и РП2 предназначены для приема из блока умножения БИС УМ и выдачи младшей и старшей частей произведения соответственно;

блок формирования признаков БФП служит для формирования и выдачи признаков результата операции умножения. К ним относятся признак нулевого результата (Z), признак переполнения (V), признак переноса (C), знаковый разряд (N).

блок умножения БУМН выполняет собственно операцию умножения операндов из регистров РА и РВ;

схема обмена информацией по магистрали данных МД; предназначена для обеспечения электрической «развязки» внутренней магистрали БИС УМ с внешней магистралью данных, обеспечивает двунаправленный обмен 16-разрядной информацией.

Функционирование БИС УМН определяется сигналами ВК1, ВК2, ВКЗ, ЧТ и ЗП (рис. 6.17).

- Рис. 6.17. Временная диаграмма работы микросхемы К588ВР2

В первую очередь необходимо загрузить операнды в регистры РА и РВ. Загрузка 16-разрядной информации с магистрали в РА происходит после подачи на входы ВК1, ВК2, ВКЗ, ЗП, ЧТ комбинации сигналов «0 1 1 0 1» при наличии уровня «1» на выводе ГОТ.

Загрузка информации с магистрали данных в РВ происходит после подачи на указанные входы комбинации сигналов «1 0 1 0 1».

После загрузки второго операнда начинается выполнение собственно умножения. Младшая часть произведения считывается из РП1 на магистраль данных после подачи на входы ВК1, ВК2, ВКЗ, ЗП, ЧТ комбинации сигналов «0 1 1 1 0».

Старшая часть произведения выдается из регистра РП2 на магистраль данных при подаче на указанные входы комбинации сигналов «1 0 1 1 0». Если на те же входы подать комбинацию сигналов «1 1 0 1 0», то из блока БФП выдаются признаки результата умножения N, Z, V, С на магистраль данных.

В табл. 6.15 приведены электрические параметры БИС УМН.

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1 | ||||

| 2 | ||||

| 3 | ||||

| 4 | ||||

| 5 | ||||

| 6 | ||||

| 7 | ||||

| 8 | ||||

| 9 | ||||

| 10 | ||||

| 11 | ||||

| 12 | ||||

| 13 | ||||

| 14 | ||||

| 15 | ||||

| 16 | ||||

| 17 | ||||

| 18 | ||||

| 19 | ||||

| 20 | ||||

| 21 | ||||

| 22 | ||||

| 23 | ||||

| 24 |

| Параметр, единица измерения | Обозначение | Значение |

|---|

6.6. МИКРОСХЕМА К688ВА1 (КР588ВА1)

Представляет собой 8-разрядный магистральный приемопередатчик (МПП) и предназначен для построения устройств связи, контроллеров внешних устройств, интерфейсных блоков.

На рис. 6.18 и 6.19 изображены условное графическое обозначение и структурная схема МПП. Назначение выводов МПП приведено в табл. 6.16.

В состав структурной схемы МПП входят следующие функциональные узлы;

усилители каналов К1 и К2 (УК1, УК2); обеспечивают возможность работы МПП на 5 ТТЛ-нагрузок;

блок формирования контроля по четности БФКЧ предназначен для формирования контрольных битов для информации, передаваемой по обоим каналам, а также для приема и обработки контрольных битов принимаемой информации. В случае появления ошибки по четности формируется сигнал ОШ = «0»;

блок управления передачами БУП осуществляет управление передачей информации между каналами К1 и К2 в соответствии с сигналами С1 и С2.

МПП осуществляет двунаправленный обмен информацией между каналами КІ и К2. Обмен может быть осуществлен как с инвертированием передаваемой информации, так и без инверсии. Сигнал ВП = «0» сопровождает информацию, выдаваемую из МПП.

- Рис. 6.18. Условное графическое обозначение микросхемы К588ВА1

- Рис. 6.19. Структурная схема микросхемы К588ВА1

- Рис. 6.20. Временная диаграмма работы микросхемы К588ВА1 при коммутации информации с канала К2 на К1

- Рис. 6.21. Временная диаграмма работы микросхемы К588ВА1 информации с канала К1 на К2

Функционирование МПП начинается с подачи на вход ВК сигнала «0». При подаче на входы С1 и С2 комбинации сигналов «0» и «1» происходит передача информации из канала К1 в канал К2. При подаче на эти же входы комбинации сигналов «1» и «0» происходит передача информации из канала К2 в канал К1. При подаче на входы С1 = С2 = «1» выходы каналов К1 и К2 переводятся в третье состояние.

Подавать одновременно сигналы «0» на входы С1 и С2 запрещается.

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1 | ||||

| 2 | ||||

| 3 | ||||

| 4 | ||||

| 5 | ||||

| 6 | ||||

| 7 | ||||

| 8 | ||||

| 9 | ||||

| 10 | ||||

| 11 | ||||

| 12 | ||||

| 13 | ||||

| 14 | ||||

| 15 | ||||

| 16 | ||||

| 17 | ||||

| 18 | ||||

| 19 | ||||

| 20 | ||||

| 21 | ||||

| 22 | ||||

| 23 | ||||

| 24 | ||||

| 25 | ||||

| 26 | ||||

| 27 | ||||

| 28 |

- Таблица 6.17. Работа микросхемы К588ВА1 при контроле передач информации

| Параметр, единица измерения | Обозначение | Значение |

|---|

При ИНВ = «0» происходит инверсная передача информации между каналами К1 и К2, при ИНВ = «1» — прямая.

Работа МПП при приеме и передаче контрольных битов представлена в табл. 6.17.

На рис. 6.20 и 6.21 приведены временные, диаграммы функционирования МПП при обмене информации между каналами К1 и К2.

Для обеспечения нормальной работоспособности МПП между выводами ОШ, ВП и питанием следует устанавливать доопределяющие резисторы. Значения резисторов можно определить из выражения (6.1), где UoL, IoL, Ucc, Uoh, Ioh — см. в табл. 6.18.

6.7. МИКРОСХЕМА К588ИР1 (КР588ИР1)

Представляет 8-разрядный многофункциональный буферный регистр (МБР) и может быть использована для построения регистровых блоков, контроллеров внешних устройств, запоминающих и интерфейсных устройств.

Условное графическое обозначение и структурная схема МБР представлены соответственно на рис. 6.22 и 6.23. В табл. 6.19 приведено назначение выводов МБР.

В состав структурной схемы МБР входят следующие функциональные узлы:

блок контроля четности БКЧ; осуществляет контроль на четность поступившей информации. При несоблюдении условия четности поступившей информации по каналу К1 вырабатывается сигнал ОШ = «0», при этом БКЧ блокирует запись информации во внутренний регистр Рг и сигнал ЗВ не формируется;

блок формирования бита четности БФБЧ; предназначен для генерации бита четности (сигнал БЧ) после обработки 8-разрядной информации, поступившей с выходов внутреннего регистра Рг;

внутренний регистр Рг; несет основную функциональную нагрузку в МБР. Запись в регистр осуществляется сигналом, вырабатываемым блоком БУЗ;

блок управления записью БУЗ; предназначен для формирования сигнала записи информации с канала К1 в Рг, а также для выработки сигнала квитирования ЗВ. Блокируется сигналом, вырабатываемым БКЧ при ошибке по четности;

- Рис. 6.22. Условное графическое обозначение микросхемы К588ИР1

- Рис. 6.23. Структурная схема микросхемы К588ИР1

буфер чтения БЧ; служит для приема информации с Рг и выдачи ее в канал Д2;

блок управления чтением БУЧ; управляет работой БЧ, вырабатывая внутренний сигнал разрешения выдачи информации из БЧ в канал К2. Вырабатывает сигнал сопровождения информации, выдаваемой в канал К2.

- Рис. 6.24. Временная диаграмма работы микросхемы К588ИР1 в режиме «Запись»

- Рис. 6.25. Временная диаграмма работы микросхемы К588ИР1 в режиме «Чтение»

Функционирование МБР начинается с подачи сигнала «0» на вход ВК. При подаче сигнала «0» на вход ЧТ происходит выдача информации в канал Д.2. При подаче на вход ЗП отрицательного фронта сигнала происходит запись в МБР информации с канала К2 (при отсутствии ошибки по четности). Если на входе ЧТ сигнал «1», то выходы канала К2 находятся в третьем состоянии.

Сигнал ЧВ сообщает о наличии выдаваемой информации в канале К.2, ЗВ — о завершении процесса записи информации в МБР из канала К1. Введение этих сигналов обусловлено использованием общего принципа асинхронного обмена, который был применен при построении всех микросхем серии.

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1 | ||||

| 2 | ||||

| 3 | ||||

| 4 | ||||

| 5 | ||||

| 6 | ||||

| 7 | ||||

| 8 | ||||

| 9 | ||||

| 10 | ||||

| 11 | ||||

| 12 | ||||

| 13 | ||||

| 14 | ||||

| 15 | ||||

| 16 | ||||

| 17 | ||||

| 18 | ||||

| 19 | ||||

| 20 | ||||

| 21 | ||||

| 22 | ||||

| 23 | ||||

| 24 | ||||

| 25 | ||||

| 26 | ||||

| 27 | ||||

| 28 |

- Таблица 6.20. Алгоритм функционирования микросхемы К588ИР1

Сигнал БЧ может быть для МБР как входным, так и выходным. Если ФК = «О», то Б Ч является входным для МБР и информация принимается по каналу К1. В этом случае МБР осуществляет «свертку» информации по модулю 2 и сравнение полученного результата «свертки» с входным сигналом БЧ. В случае совпадения осуществляется операция записи в МБР с выработкой выходного сигнала ЗВ = «0». При несовпадении указанных сигналов формируется сигнал ОШ = «О», запись в МБР блокируется и сигнал ЗВ = «О» не выдается.

Если на входе ФК сигнал «1», то МБР формирует бит четности информации, выдаваемой по каналу К2.

Очистка регистра (установка в нуль) происходит при подаче на вход УСТ сигнала «0» независимо от сигналов на остальных входах МБР.

Вход ИНВ используется для осуществления выдачи информации инверсным кодом. В табл. 6.20 наглядно показано действие управляющих сигналов.

- Рис. 6.26. Временная диаграмма работы микросхемы К588ИР1 в режиме «Чтение — Запись»

На рис. 6.24 … 6.26 приведены временные диаграммы работы МБР, в табл. 6.21 — его электрические параметры.

При использовании микросхемы МБР необходимо между выводами ОШ , ЧВ, ЗВ и питанием подключать резисторы. Номинальные значения резисторов определяются так же, как и для микросхемы МПП (см. п. 6.3).

| Параметр, единица измерения | Обозначение | Значение |

|---|

6.8. МИКРОСХЕМА К588ВГ2 (КР588ВГ2)

Микросхема является контроллером запоминающего устройства (КЗ У) и предназначена для создания ЗУ различной организации, совместимых с каналом микроЭВМ «Электроника-60».

На рис. 6.27 представлено условное графическое обозначение, а в табл. 6.22 — назначение выводов микросхемы КЗУ.

- Рис. 6.27. Условное графическое обозначение микросхемы К588ВГ2

- Рис. 6.28, Структурная схема микросхемы К588ВГ2

В состав структурной схемы КЗУ (рис. 6.28) входят следующие функциональные узлы:

регистр адреса модуля ЗУ РА; предназначен для приема и запоминания старших разрядов адреса ЗУ. Защелкивание информации в РА происходит по отрицательному фронту сигнала ОБМ. Выходами подключен к первой группе входов ССА;

схема селекции адреса ССА; предназначена для сравнения комбинаций разрядов адреса АД15 … АД13 с жестко заданным именным кодом модуля ЗУ (А 15 … А 13). Селектирование происходит при ОБМ = «0» и внутреннем сигнале разрешения селектирования. Последний вырабатывается блоком Б У О;

блок управления обменом БУО; управляет работой блоков БУО и БВ;

блок выборки ЗУ БВ; предназначен для формирования сигналов ВКО и ВКР,

блок моделирования цикла ЗУ БМЦ; служит для настройки КЗУ на взаимодействие с блоками ЗУ, имеющими различные времена выборки. Настройка (моделирование) осуществляется установкой внешних времязадающих ДС-цепочек. Последние подключаются к выводам ЗДЧ и ЗДЗ. Вырабатывает сигнал ОТВ = «0» по положительному фронту сигнала ЗДЧ и отрицательному фронту сигнала ДЧТ.

Функционирование КЗУ определяется управляющими сигналами ОБМ, ПЗП, АДО, ДЧТ и ДЗП (табл. 6.23).

- Рис. 6.29. Временная диаграмма работы микросхемы К588ВГ2

При выполнении цикла чтения данных из модуля ЗУ по сигналу ОБМ = «0» происходит защелкивание старших разрядов адреса АД13 … АД15 и сравнение их с заданным кодом на выводах А13 … А15 (рис. 6.29). При совпадении этих кодов на выводе ЗДЧ появляется сигнал «0» и формируются сигналы В ДО = ВД1 = «0». На выводе ЗД Ч появляется положительный фронт, длительность которого определяется внешней RС-цепочкой. После этого по приходу сигнала ДЧТ = «0» КЗУ формирует сигнал ОТВ = «0». При переходе сигнала ДЧТ в состояние «1» прекращается выборка модуля ЗУ (ВК0 = ВК1 = «1») и ОТВ переходит в состояние «1». Цикл завершается сигналом ОБМ = «1». КЗУ готов принять следующую информацию.

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1 | ||||

| 2 | ||||

| 3 | ||||

| 4 | ||||

| 5 | ||||

| 6 | ||||

| 7 | ||||

| 8 | ||||

| 9 | ||||

| 10 | ||||

| 11 | ||||

| 12 | ||||

| 13 | ||||

| 14 | ||||

| 15 | ||||

| 16 | ||||

| 17 | ||||

| 18 |

- Таблица 6.23. Операции микросхемы К588ВГ2

При выполнении цикла записи информации в модуль ЗУ так же осуществляется сравнение кодов АД13 … АД15 с кодом на выводах А13 … А15. По сигналу ДЗП = «0» формируются сигналы ВКО и ВК1. Напряжение на выводе ЗДЗ начинает расти (фронт определяется внешней RС-цепочкой) и вызывает формирование сигнала ОТВ = «0». Вслед за этим формируется положительный фронт сигнала ДЗП. Цикл заканчивается сигналом ОБМ = «1».

Следует отметить, что времязадающая RС-цепь подключается между выводами ЗДЧ и ЗДЗ и питанием (резистор и конденсатор, на каждый вывод подключаются параллельно). Кроме того, для обеспечения нормального функционирования необходимо подключать резистор между питанием и выводом ОТВ. Значение резистора находится из выражения, приведенного для микросхемы МПП. R и С времязадающих цепочек подбираются из условия согласования временной диаграммы работы модуля ЗУ с работой микросхемы СК. В табл. 6.24 приведены электрические параметры микросхемы КЗУ.

| Параметр, единица измерения | Обозначение | Значение |

|---|

6.9. МИКРОСХЕМА К588ВТ1 (КР588ВТ1)

Представляет селектор адреса (СА) и предназначен для выполнения функций селектирования одного из восьми регистров внешних устройств, подключенных к Q-шине. Микросхема СА может быть использована также для организации операций обмена содержимым внешних регистров как пословного, так и побайтного. Условное графическое обозначение СА представлено на рис. 6.30. В табл. 6.25 приведено назначение выводов СА. Структурная схема СА дана на рис. 6.31.

- Рис. 6.30. Условное графическое обозначение микросхемы К588ВТ1

- Рис. 6.31. Структурная схема микросхемы К588ВТ1

В состав структурной схемы СА входят следующие функциональные узлы:

регистр адреса РА; предназначен для буферизации поступающего 13-разрядного кода адреса. Старшая 9-разрядная его часть (АД4 … АД12) с выходов РА поступает на ССА;

схема сравнения адреса ССА; предназначена для выполнения операции поразрядного сравнения кода, поступающего о выходов РА, с кодом А4 … А12;

формирователь Ф; принимает выходную информацию с дешифратора ДШ; выдает сигналы ВК0 … ВК7;

дешифратор ДШ; дешифрирует 3-разрядный код АД1 … АДЗ при наличии сигналов ОБМ = ВУ = «0»;

схема управления СУ; обеспечивает взаимодействие микросхемы СА с Q-шиной и внешними устройствами.

Функционирование СА сводится к выполнению пяти циклов (см. п. 6.4): DATI, DATO, DАТОВ, DАTIO, DАТІОВ.

Выполнение DАТІ (ввода слова) начинается с установки (рис. 6.32) процессором адреса на шине АДО … АД12 и сигналов ВУ = ОБМ = «0». Микросхема СА сравнивает девять старших разрядов этого адреса с разрядами жестко «зашитыми» на выходах А4 … А12. Затем происходит дешифрация разрядов АД1 … АДЗ и выборка одного из восьми регистров одним из сигналов на шине ВК.

| Номер вывода |

Назначение | Разряд | Обозначение | Тип |

|---|---|---|---|---|

| 1 | ||||

| 2 | ||||

| 3 | ||||

| 4 | ||||

| 5 | ||||

| 6 | ||||

| 7 | ||||

| 8 | ||||

| 9 | ||||

| 10 | ||||

| 11 | ||||

| 12 | ||||

| 13 | ||||

| 14 | ||||

| 15 | ||||

| 16 | ||||

| 17 | ||||

| 18 | ||||

| 19 | ||||

| 20 | ||||

| 21 | ||||

| 22 | ||||

| 23 | ||||

| 24 |

Процессор снимает адрес и сигнал ВУ и формирует сигнал ДЧТ = «О», по которому СА выставляет сигнал ЧТ = «О». Последний инициирует выбранное внешнее устройство на выдачу данных. Выдаваемые данные сопровождаются сигналом ГОТ = «О», по которому СА формирует сигнал ОСТ = «О». Получив данные, процессор снимает сигнал ДЧТ, а СА — сигнал ЧТ. Затем происходит цепочное снятие сигналов ГОТ, ОСТ, ОБМ и ВК.

- Рис. 6.32. Временная диаграмма работы микросхемы К588ВТ1 в цикле DАТІ

- Рис. 6.33. Временная диаграмма работы микросхемы К588ВТ1 в цикле DATO

При выполнении цикла DATO (ввод слова) процессор выдает на шину адреса информацию АД0 … АД12 и выдает сигналы ВУ = ОБМ = ПЗП = «0» (рис. 6.33). Затем так же как и для цикла DАТІ происходит сравнение адреса, дешифрация 3-разрядного кода и выдача соответствующего разряда шины ВК. Процессор снимает адрес, сигналы ВУ и ПЗП и устанавливает данные и сигнал ДЗП = «0», по которому СА формирует сигналы ЗПС = ЗПМ = «0», разрешающие выбранному устройству запись данных. В ответ на поступившие данные внешнее устройство вырабатывает сигнал ГОТ = «0», сообщающий о том, что данные приняты. Затем СА устанавливает сигнал ОСТ = «0». Процессор снимает данные и сигнал ДЗП, по которому внешнее устройство снимает сигнал ГОТ, а СА — сигнал ОСТ.

Следующим действием является снятие процессором сигнала ОБМ, по которому СА снимает сигнал с шины ВК. Выполнение цикла DАТОВ (вывод байта) отличается от цикла DАТО тем, что процессор сбрасывает сигнал ПЗП по снятию данных и в зависимости от значения разряда АДО производятся действия над младшим (АДО = «0») либо старшим (АДО = «1») байтами слова. При этом вырабатываются сигналы ЗПМ либо ЗПС = «0».

- Рис. 6.34. Временная диаграмма работы микросхемы К588ВТ1 в цикле DATIO

Цикл DATIO (ввод — модификация — вывод слова) является смешанным. Первая его половина выполняется как в цикле DАТІ (вплоть до выработки сигнала ОСТ = «0»). Вторая половина цикла выполняется как DАТО, начиная с момента снятия процессором адреса. Однако в этом цикле процессор не устанавливает сигнал ПЗП = «0» (рис. 6.34).

Отличие выполнения цикла DATIOB (ввод — модификация — вывод байта) от DATIO в том, что при выводе данных процессор устанавливает сигнал ПЗП = «О».

На рис. 6.32 … 6.34 приведены временные диаграммы выполнения циклов обмена.

В табл. 6.26 даны электрические параметры микросхемы СА.

| Параметр, единица измерения | Обозначение | Значение |

|---|

6.10. ПРИМЕНЕНИЕ МИКРОСХЕМ СЕРИИ К588 (КР588)

На рис. 6.35 приведен пример использования микросхемы СА при совместной работе с БИС УМ. На рис. 6.36 дана структурная схема модуля ОЗУ, на которой показано включение микросхем КЗУ, МБР и МПП.

На рис. 6.37 приведена структурная схема процессора с системой команд микроЭВМ «Электроника-60». В состав процессора входят: устройство микропрограммного управления УМУ, операционный блок ОБ и распределитель информации РИ.

По магистрали данных поступает информация, в качестве которой могут быть переданы в (из) процессор(а) данные, адреса и команды. Код команды поступает на устройство УМУ. Здесь происходит преобразование команды в помикрокомандную последовательность. Разрядность микрокоманды процессора — 25. Микросхемы УП с «прошивками» 0001 … 0004 предназначены для осуществления микропрограммного управления блоком ОБ (собственно АЛУ). Четыре БИС УП для управления ОБ необходимы прежде всего ввиду широкого набора команд «Электроники-60», а также в связи с ограниченными информационными возможностями каждой БИС УП. БИС УП 0005 предназначена для выдачи микрокоманд разрешения прерывания, а также для управления блоком распределения информации.

- Рис. 6.35. Пример применения микросхемы К588ВР2 совместно с микросхемой К588ВТ1

- Рис. 6.36. Структурная схема ОЗУ

К сигналам разрешения прерывания ВУ относятся: ПРРО (МК.0) (с вектором 170); ПРР1 (МК.1) (с вектором 174); ПРР2 (МК2) (с вектором 270); ПРРЗ (МК.З) (с вектором 274); ПРРВС (МК4) (по внешнему событию); ПРР ОСТ (МК.5) (по «Останову»).

К сигналам управления обменом данных относятся: ОБМ — обмен данными; ДЧТ, ДЗП — чтение, запись данных; ОТВ — ответ; ПЗП — запись байта; ЗПРО … ЗПРЗ — запросы прерывания ВУ с фиксированным вектором; ЗПР — запрос прерывания ВУ с вводимым вектором; ПРР — разрешение прерывания ВУ с вводимым вектором; ЗМ, РЗМ, ПЗ — сигналы обеспечения режима прямого доступа в память; ОСТ — аппаратный останов; АИП — авария источника питания; ПВС — прерывание по внешнему событию.

Разряды микрокоманды МК7 … МКН управляют работой микросхемы СК. БИС СК обеспечивает выработку управляющих сигналов процессора КВ1, КВ2, которые инициируют прием командной (для БИС УП) либо операндной информации. В соответствии с этим прием информации происходит в операционный блок, либо в УМУ. Тип обмена, который обеспечивают сигналы квитирования (ответа) информации В, Ф1 — асинхронный. Ветвление (изменение последовательности выборки микрокоманд) происходит после анализа информации на магистрали МС.

- Рис. 6.37. Структурная схема процессора микроЭВМ

СПИСОК ЛИТЕРАТУРЫ

9. Бобков В. А. и др. Микромощные микропроцессорные БИС серии К588 на дополняющих МДП-транзисторах // Электронная промышленность, 1979, вып. 10. С. 36—38.

34. Интегральные микросхемы: Справочник / Тарабрин Б. В., Лунин Л. Ф., Смирнов Ю. Н. и др. Под ред. Б. В. Тарабрина. М.: Радио и связь, 1984. 528 с.

45. Микропроцессорные комплекты интегральных схем: состав и структура: Справочник / Борисов В. С., Васенков, А. А., Малашевич Б. М. идр. Под ред, A. А. Васенкова, В. А. Шахнова. М.: Радио и связь, 1982. 192 с.

46. Мильнер А. Д. и др. Принципы построения проблемно-ориентированного комплекса для программирования МП-устройств и система отладки на его базе // Машинное моделирование. М.: МДНТП им. Ф. Э. Дзержинского, 1980. С. 83—91.