Немига/ТО: различия между версиями

< Немига

Nzeemin (обсуждение | вклад) |

Nzeemin (обсуждение | вклад) |

||

| (не показано 16 промежуточных версий этого же участника) | |||

| Строка 26: | Строка 26: | ||

управляет распределением времени использования канала внешними устройст- | управляет распределением времени использования канала внешними устройст- | ||

вами и выполняет все необходимые арифметико-логические операции для | вами и выполняет все необходимые арифметико-логические операции для | ||

обработки информации. Он содержит | обработки информации. Он содержит 16 быстродействующих регистров общего | ||

назначения (РОН), 8 из них (R0...R7) программно доступны, а 8 других | назначения (РОН), 8 из них (R0...R7) программно доступны, а 8 других | ||

используются как служебные регистры при выполнении микрокоманд. | используются как служебные регистры при выполнении микрокоманд. | ||

Центральный процессор выполняет одноадресные команды, двухадресные | Центральный процессор выполняет одноадресные команды, двухадресные | ||

команды, команды расширенной арифметики, может обрабатывать как | команды, команды расширенной арифметики, может обрабатывать как 16-раз- | ||

рядные слова, та к и 8-разрядные байты. Возможность использования 8 | рядные слова, та к и 8-разрядные байты. Возможность использования 8 | ||

методов адресации позволяет вести высокоэффективную обработку данных, | методов адресации позволяет вести высокоэффективную обработку данных, | ||

| Строка 64: | Строка 64: | ||

нения команды в состоянии Т-разряда, используемого при отладке про- | нения команды в состоянии Т-разряда, используемого при отладке про- | ||

граммы. На рис.2 показан формат ССП. Разряд приоритета процессора | граммы. На рис.2 показан формат ССП. Разряд приоритета процессора | ||

(7- й разряд ССП) может находиться в состоянии " | (7-й разряд ССП) может находиться в состоянии "0" или "1". В по- | ||

следнем случае внешние устройства не могут вызвать прерывание теку- | следнем случае внешние устройства не могут вызвать прерывание теку- | ||

щей программы. | щей программы. | ||

| Строка 111: | Строка 111: | ||

имеет следующий вид: | имеет следующий вид: | ||

-┌─-------─┬─---------------------─┬─-------─┐- | |||

| КОП | Метод | | | КОП | Метод | РОН | | ||

| | адресации | | | | адресации | | | ||

-└─-------─┴─---------------------─┴─-------─┘- | |||

15 6 5 3 2 0 | |||

Формат одноадресных команд | Формат одноадресных команд | ||

| Строка 121: | Строка 121: | ||

Формат двухадресных команд имеет следующий вид: | Формат двухадресных команд имеет следующий вид: | ||

--------------------------------- | ┌─-----─┬─---------─┬─-----─┬─-----------─┬─---─┐ | ||

| КОП | Метод | | | КОП | Метод | РОН | Метод | РОН | | ||

| | адресации | | адресации | | | | | адресации | | адресации | | | ||

--------------------------------- | └─-----─┴─---------─┴─-----─┴─-----------─┴─---─┘ | ||

15 12 11 9 8 6 5 3 2 0 | |||

-------------- | ──--------------── ................... | ||

Поле адресации операнда Поле адресации опе- | Поле адресации операнда Поле адресации опе- | ||

источника (SS) ранда приемника (DD) | источника (SS) ранда приемника (DD) | ||

| Строка 137: | Строка 137: | ||

Метод адресации | Метод адресации | ||

-─┬─----─┬─-----─┬─----─┬─- | |||

| | | | | | | ||

| | | | | |||

| | | -─┴─----─┴─-----─┴─----─┴─- | ||

| | └─- Признак прямой (0) | |||

| | или косвенной (1) | |||

└- -┬- -┘ адресации | |||

| | | | ||

└─ - - - Адресации: | |||

00 - регистровая | 00 - регистровая | ||

01 - с автоувеличением | 01 - с автоувеличением | ||

| Строка 257: | Строка 256: | ||

<pre> | <pre> | ||

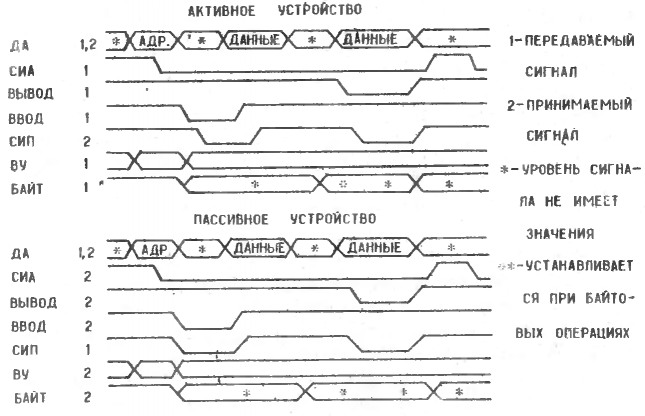

Как адрес, так и данные (слова или байты) передаются по одним | Как адрес, так и данные (слова или байты) передаются по одним | ||

и тем же | и тем же 16 линиям адреса/данных К ДА(00-15)Н. Любой цикл обращения | ||

к каналу начинается с адресации пассивного устройства. После завер- | к каналу начинается с адресации пассивного устройства. После завер- | ||

шения адресной части цикла активное устройство выполняет прием или | шения адресной части цикла активное устройство выполняет прием или | ||

| Строка 267: | Строка 266: | ||

Сигнал синхронизации активного устройства (К СИА Н) вырабатыва- | Сигнал синхронизации активного устройства (К СИА Н) вырабатыва- | ||

ется активным устройством (процессором). Передний фронт этого сигна- | ется активным устройством (процессором). Передний фронт этого сигна- | ||

ла означает, что адрес находится на линиях К ДА(00- | ла означает, что адрес находится на линиях К ДА(00-15)Н. Сигнал | ||

К СИА Н сохраняет активный уровень до окончания текущего цикла обра- | К СИА Н сохраняет активный уровень до окончания текущего цикла обра- | ||

щения к каналу. | щения к каналу. | ||

Сигнал синхронизации пассивного устройства (К СИП Н) информи- | Сигнал синхронизации пассивного устройства (К СИП Н) информи- | ||

рует активное устройство о том, что данные приняты с линией К ДА(00- | рует активное устройство о том, что данные приняты с линией К ДА(00-15)Н | ||

или данные установлены на информационных линиях. Этот сигнал выраба- | или данные установлены на информационных линиях. Этот сигнал выраба- | ||

тывается в ответ на сигнал К ВВОД Н и К ВЫВОД Н. | тывается в ответ на сигнал К ВВОД Н и К ВЫВОД Н. | ||

| Строка 285: | Строка 284: | ||

при прерывании программы. Сигнал К ВЫВОД Н означает, что по отноше- | при прерывании программы. Сигнал К ВЫВОД Н означает, что по отноше- | ||

нию к активному устройству выполняется операция вывода, и на линиях | нию к активному устройству выполняется операция вывода, и на линиях | ||

К ДА(00- | К ДА(00-15)Н помещены истинные данные. Выработка сигнала К ВЫВОД Н | ||

активным устройством по отношению к подаваемым в канал данным задер- | активным устройством по отношению к подаваемым в канал данным задер- | ||

жана не менее чем на | жана не менее чем на 150 нс. Пассивное устройство, отвечая на сигнал | ||

К ВЫВОД Н, должно вырабатывать ответный сигнал К СИП Н, чтобы завер- | К ВЫВОД Н, должно вырабатывать ответный сигнал К СИП Н, чтобы завер- | ||

шить операцию передачи данных. | шить операцию передачи данных. | ||

| Строка 341: | Строка 340: | ||

Активное устройство в адресной части передает по линиям К | Активное устройство в адресной части передает по линиям К | ||

ДА(00-I5) H адрес, a также вырабатывает сигнал K BУ H, если адрес | ДА(00-I5) H адрес, a также вырабатывает сигнал K BУ H, если адрес | ||

находится в диапазоне 160000-177777. Hе менее чем через | находится в диапазоне 160000-177777. Hе менее чем через 150 нc после | ||

установки адреса активное устройство вырабатывает сигнал К СИА H, | установки адреса активное устройство вырабатывает сигнал К СИА H, | ||

предназначенный для запоминания адреса во входной логике выбранного | предназначенный для запоминания адреса во входной логике выбранного | ||

устройства. | устройства. | ||

Пассивное устройство дешифрирует адрес и запоминает его. | Пассивное устройство дешифрирует адрес и запоминает его. | ||

Активное устройство снимает адрес с линий К ДА (00- | Активное устройство снимает адрес с линий К ДА (00-15) H, очища- | ||

ет линию К ВУ H и вырабатывает сигнал K ВВОД H, сигнализируя о том, | ет линию К ВУ H и вырабатывает сигнал K ВВОД H, сигнализируя о том, | ||

что оно готово принять данные от пассивного устройства и ожидает по- | что оно готово принять данные от пассивного устройства и ожидает по- | ||

ступления сигнала К СИП Н. | ступления сигнала К СИП Н. | ||

Пассивное устройство помещает данные на линии К ДА(00- | Пассивное устройство помещает данные на линии К ДА(00-15)Н | ||

и вырабатывает сигнал К СИП H, сигнализирующий о том, что данные | и вырабатывает сигнал К СИП H, сигнализирующий о том, что данные | ||

находятся в канале. Если сигнал К СИП H не вырабатывается в течение | находятся в канале. Если сигнал К СИП H не вырабатывается в течение | ||

10 мкс после выработки сигнала К ВВОД Н, центральный процессор пе- | |||

реходит к обслуживанию внутреннего прерывания по ошибке обращения | реходит к обслуживанию внутреннего прерывания по ошибке обращения | ||

к каналу с адресом вектора 4. | к каналу с адресом вектора 4. | ||

| Строка 380: | Строка 379: | ||

Активное устройство в адресной части цикла передает по линиям | Активное устройство в адресной части цикла передает по линиям | ||

К ДА(00- | К ДА(00-15)Н адрес, а также сигнал К ВУ Н, если это необходимо. | ||

Кроме того, в цикле "ВЫВОД" в адресной части вырабатывается | Кроме того, в цикле "ВЫВОД" в адресной части вырабатывается | ||

сигнал К БАЙТ H. He менее чем через 150 нс после установки адреса | сигнал К БАЙТ H. He менее чем через 150 нс после установки адреса | ||

| Строка 386: | Строка 385: | ||

сигналами, те же, что и в цикле ВВОД. | сигналами, те же, что и в цикле ВВОД. | ||

Пассивное устройство дешифрирует адрес и запоминает его. Актив- | Пассивное устройство дешифрирует адрес и запоминает его. Актив- | ||

ное устройство снимает адрес с линий К ДА(00- | ное устройство снимает адрес с линий К ДА(00-15)Н, очищает линию | ||

К ВУ H и снимает сигнал К БАЙТ Н. После этого активное устройство | К ВУ H и снимает сигнал К БАЙТ Н. После этого активное устройство | ||

помещает данные на линии К ДА(00- | помещает данные на линии К ДА(00-15) и вырабатывает сигнал | ||

К ВЫВОД Н. | К ВЫВОД Н. | ||

Пассивное устройство принимает данные с линий К ДА(00- | Пассивное устройство принимает данные с линий К ДА(00-15)Н и | ||

вырабатывает сигнал К СИП Н. | вырабатывает сигнал К СИП Н. | ||

Активное устройство снимает сигнал К CИА H, завершая цикл кана- | Активное устройство снимает сигнал К CИА H, завершая цикл кана- | ||

| Строка 396: | Строка 395: | ||

В цикле ВЫВОД сигнал К БАЙТ Н в части передачи данных может | В цикле ВЫВОД сигнал К БАЙТ Н в части передачи данных может | ||

быть как пассивным, так и активным, определяя тем самым вывод | быть как пассивным, так и активным, определяя тем самым вывод | ||

16-разрядного слова или вывод байта. | |||

</pre> | </pre> | ||

| Строка 410: | Строка 409: | ||

Операция по выводу данных может быть байтовой, поэтому сигнал | Операция по выводу данных может быть байтовой, поэтому сигнал | ||

К БАЙТ Н в это время может быть как пассивным, так и активным. | К БАЙТ Н в это время может быть как пассивным, так и активным. | ||

</pre> | |||

[[Файл:NemigaTO-pic7.png|645px]] | |||

<pre> | |||

Рис. 7. Временная диаграмма выполнения цикла ВВОД-ПАУЗА-ВЫВОД | |||

</pre> | </pre> | ||

=== 5.6. Средства обеспечения программной совместимости ПК с машинами семейства | === 5.6. Средства обеспечения программной совместимости ПК с машинами семейства «Электроника-60» === | ||

<pre> | <pre> | ||

Основная сложность переноса существующего системного и приклад- | Основная сложность переноса существующего системного и приклад- | ||

ного программного обеспечения, разработанного для машин семейства | ного программного обеспечения, разработанного для машин семейства | ||

"Электроника-60", заключается в том, что в качестве системного тер- | "Электроника-60", заключается в том, что в качестве системного тер- | ||

| Строка 453: | Строка 452: | ||

Конструктивно ПК состоит из следующих функционально закончен- | Конструктивно ПК состоит из следующих функционально закончен- | ||

ных узлов и блоков: | ных узлов и блоков: | ||

модуль процессора 6. | модуль процессора 6.120.107; | ||

модуль ОЗУ 6. | модуль ОЗУ 6.120.108; | ||

модуль локальной сети и таймер 6. | модуль локальной сети и таймер 6.120.109; | ||

модуль электронный 2MБ5 2.087.024; | модуль электронный 2MБ5 2.087.024; | ||

модуль электронный 2МБI2 2.087.024- | модуль электронный 2МБI2 2.087.024-01; | ||

блок клавиатуры 3.059.007; | блок клавиатуры 3.059.007; | ||

видеоконтрольное устройство (ВКУ). | видеоконтрольное устройство (ВКУ). | ||

| Строка 473: | Строка 472: | ||

Процессорное ядро включает в себя центральный процессорный эле- | Процессорное ядро включает в себя центральный процессорный эле- | ||

мент D1 , выполняющий функции арифметико-логического устройства (АЛУ). | мент D1, выполняющий функции арифметико-логического устройства (АЛУ). | ||

пять БИС управляющей памяти D2...D6, системный контроллер D18, два | пять БИС управляющей памяти D2...D6, системный контроллер D18, два | ||

магистральных приемопередатчика (МПП) D21, D24. | магистральных приемопередатчика (МПП) D21, D24. | ||

АЛУ предназначено для приема, хранения, обработки | АЛУ предназначено для приема, хранения, обработки 16-разрядных | ||

чисел. Преобразование данных выполняется в соответствии c | чисел. Преобразование данных выполняется в соответствии c 12-разряд- | ||

ным кодом микрокоманды. | ным кодом микрокоманды. | ||

Последовательность фаз работы микросхемы определяет внутренний | Последовательность фаз работы микросхемы определяет внутренний | ||

| Строка 493: | Строка 492: | ||

выдачи (выдача результата операции в МД). | выдачи (выдача результата операции в МД). | ||

Прием микрокоманд и обмен данными по магистрали производится | Прием микрокоманд и обмен данными по магистрали производится | ||

асинхронно и соответственно квитируется сигналами по выводам ВК- | асинхронно и соответственно квитируется сигналами по выводам ВК-Ф1 | ||

и В-П, т.к. по шине микрокоманд информация может только приниматься | и В-П, т.к. по шине микрокоманд информация может только приниматься | ||

в АЛУ, выводы ВК и | в АЛУ, выводы ВК и Ф1 - однонаправленные. Сигналы В и П двунаправ- | ||

ленные, т.к. квитируют передачу данных по МД. При приеме данных в МД | ленные, т.к. квитируют передачу данных по МД. При приеме данных в МД | ||

сигнал на входе В генерируется системным контроллером D18 и иниции- | сигнал на входе В генерируется системным контроллером D18 и иниции- | ||

| Строка 512: | Строка 511: | ||

начена для аппаратной реализации команд расширенной арифметики (ум- | начена для аппаратной реализации команд расширенной арифметики (ум- | ||

ножение, деление, сдвиги – MUL, DIV, ASH, ASHC). | ножение, деление, сдвиги – MUL, DIV, ASH, ASHC). | ||

Сигналы на входах R0 и | Сигналы на входах R0 и R1 по положительному фронту устанавли- | ||

вают микросхему УП в исходное состояние. При наличии логического | вают микросхему УП в исходное состояние. При наличии логического | ||

нуля на выводе В происходит прием информации с магистрали данных | нуля на выводе В происходит прием информации с магистрали данных | ||

| Строка 520: | Строка 519: | ||

При снятии сигнала "ЛОГИЧЕСКИЙ НОЛЬ" на выводе В снимается сигнал | При снятии сигнала "ЛОГИЧЕСКИЙ НОЛЬ" на выводе В снимается сигнал | ||

и на выводе П. | и на выводе П. | ||

По отрицательному фронту сигнала | По отрицательному фронту сигнала Ф1 прекращается выдача микро- | ||

команды и происходит "ПОДБРОС" в высокий потенциал состояния выво- | команды и происходит "ПОДБРОС" в высокий потенциал состояния выво- | ||

дов МК (0-12). Если к этому времени сформирована следующая микроко- | дов МК (0-12). Если к этому времени сформирована следующая микроко- | ||

| Строка 526: | Строка 525: | ||

Системный контроллер предназначен для связи внутреннего интер- | Системный контроллер предназначен для связи внутреннего интер- | ||

фейса процессора с внешним стандартным интерфейсом канала типа | фейса процессора с внешним стандартным интерфейсом канала типа | ||

Q-шины (OCT | Q-шины (OCT 11305.903-80). | ||

Внутренний интерфейс процессора содержит символы, обеспечиваю- | Внутренний интерфейс процессора содержит символы, обеспечиваю- | ||

щие работу процессорного ядра. Это сигналы квитирования АЛУ и УП, | щие работу процессорного ядра. Это сигналы квитирования АЛУ и УП, | ||

16-разрядная информационная магистраль, четырехразрядная магистраль | |||

кода прерывания, сигналы управления МПП. Сигналы квитирования | кода прерывания, сигналы управления МПП. Сигналы квитирования KB1, | ||

KB2, | KB2, КВ3, КП обеспечивают передачу по 16-разрядной двунаправленной | ||

магистрали, адресов, данных, векторов прерывания в данный момент | магистрали, адресов, данных, векторов прерывания в данный момент | ||

обслуживания. | обслуживания. | ||

| Строка 556: | Строка 555: | ||

В адресном пространстве процессора с адреса 160000 по 167776 | В адресном пространстве процессора с адреса 160000 по 167776 | ||

занимает системное ПЗУ. Адресное пространство процессора 140000-157776 | занимает системное ПЗУ. Адресное пространство процессора 140000-157776 | ||

зарезервировано под дополнительные | зарезервировано под дополнительные 4К слов системного ПЗУ. | ||

При обращении к области памяти обязательного системного ПЗУ | При обращении к области памяти обязательного системного ПЗУ | ||

контроллер запоминающего устройства D15 вырабатывает сигнал ВКО, | контроллер запоминающего устройства D15 вырабатывает сигнал ВКО, | ||

| Строка 572: | Строка 571: | ||

импульсы с частотой в 2 раза меньшей частоты импульсов, на основе | импульсы с частотой в 2 раза меньшей частоты импульсов, на основе | ||

которых формируется информационная последовательность в блоке кла- | которых формируется информационная последовательность в блоке кла- | ||

виатуры. Выходы канала | виатуры. Выходы канала K1 D26 соединены с входами канала К0 D26 со | ||

смещением на один разряд, т.е. последовательный код с клавиатуры | смещением на один разряд, т.е. последовательный код с клавиатуры | ||

преобразуется в параллельный. По достижении стартовой посылки послед- | преобразуется в параллельный. По достижении стартовой посылки послед- | ||

него разряда | него разряда K1 D26 триггер D37.2 формирует сигнал готовности конт- | ||

роллера клавиатуры к выдаче данных. Этот сигнал поступает в HALT-мо- | роллера клавиатуры к выдаче данных. Этот сигнал поступает в HALT-мо- | ||

нитор. Инверсным сигналом с триггера D37.2 код символа переписыва- | нитор. Инверсным сигналом с триггера D37.2 код символа переписыва- | ||

| Строка 651: | Строка 650: | ||

на выходе мультиплексора D12 формируется высокий уровень, который | на выходе мультиплексора D12 формируется высокий уровень, который | ||

фиксируется сигналом СИА в регистре D13 и блокирует прохождение | фиксируется сигналом СИА в регистре D13 и блокирует прохождение | ||

сигналов обращения к памяти через элемент D4.1 | сигналов обращения к памяти через элемент D4.1. | ||

Для эмуляции стандартных устройств клавиатуры и терминала в | Для эмуляции стандартных устройств клавиатуры и терминала в | ||

массиве памяти разрешен доступ по адресам | массиве памяти разрешен доступ по адресам 177560-177576. Сигналы | ||

выборки формируются микросхемой D15. | выборки формируются микросхемой D15. | ||

</pre> | </pre> | ||

| Строка 662: | Строка 661: | ||

177566 - обращение к регистру данных терминала (выход D0). | 177566 - обращение к регистру данных терминала (выход D0). | ||

Ha основе данного сигнала формируется запрос на | Ha основе данного сигнала формируется запрос на | ||

прерывание | прерывание Н1. | ||

177564 - обращение к регистру состояния терминала (выход D1). | 177564 - обращение к регистру состояния терминала (выход D1). | ||

| Строка 682: | Строка 681: | ||

частоты 8 МГц делится микросхемой D8 на последовательности со сле- | частоты 8 МГц делится микросхемой D8 на последовательности со сле- | ||

дующими частотами: 4 МГц, 2 МГц, 1 МГц. | дующими частотами: 4 МГц, 2 МГц, 1 МГц. | ||

Видеосчетчик, собранный на микросхемах D18...D21 , делит вход- | Видеосчетчик, собранный на микросхемах D18...D21, делит вход- | ||

ную последовательность импульсов 1 МГц на последовательности, убы- | ную последовательность импульсов 1 МГц на последовательности, убы- | ||

вающими по частоте кратными двум. Ha последнем разряде видеосчетчи- | вающими по частоте кратными двум. Ha последнем разряде видеосчетчи- | ||

| Строка 709: | Строка 708: | ||

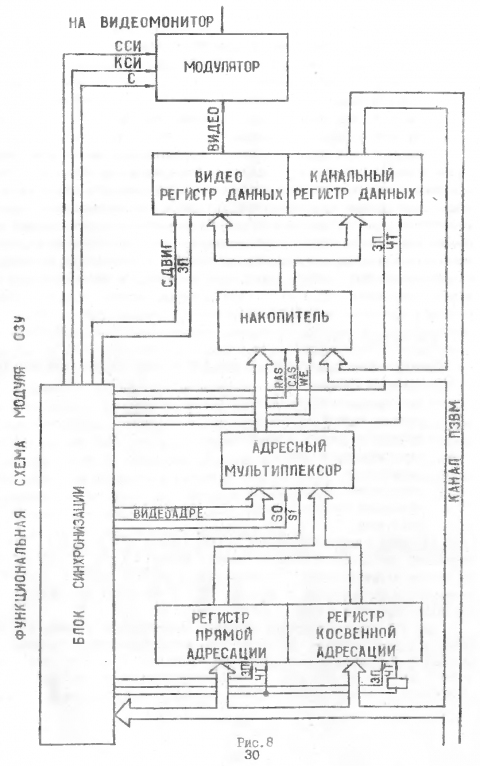

При обращении к расширенной памяти (128 Кбайт) используется | При обращении к расширенной памяти (128 Кбайт) используется | ||

регистр косвенной адресации (D28, D29). Запись в этот регистр осу- | регистр косвенной адресации (D28, D29). Запись в этот регистр осу- | ||

ществляется при обращении к ячейке памяти с адресом | ществляется при обращении к ячейке памяти с адресом 177572. При об- | ||

рещении к ячейке с адресом 177570 происходит чтение или запись по | рещении к ячейке с адресом 177570 происходит чтение или запись по | ||

адресу, хранящемуся в регистре косвенной адресации D28, D29 . Выхо- | адресу, хранящемуся в регистре косвенной адресации D28, D29. Выхо- | ||

ды регистра прямой адресации D27, D26 соединены параллельно с выхо- | ды регистра прямой адресации D27, D26 соединены параллельно с выхо- | ||

дами регистра косвенной адресации со сдвигом на один разряд. Нулевой | дами регистра косвенной адресации со сдвигом на один разряд. Нулевой | ||

| Строка 718: | Строка 717: | ||

внешней шине управления при операции записи или чтения нулевой раз- | внешней шине управления при операции записи или чтения нулевой раз- | ||

ряд данного регистра участвует в выборе ячейки памяти и таким обра- | ряд данного регистра участвует в выборе ячейки памяти и таким обра- | ||

зом организуется доступ к | зом организуется доступ к 128 Кбайтам накопителя. При обмене дан- | ||

ными размером в слово регистр косвенной адресации отключается и | ными размером в слово регистр косвенной адресации отключается и | ||

элемент D16.5 формирует логический ноль в разряде | элемент D16.5 формирует логический ноль в разряде A17 регистра кос- | ||

венной адресации. | венной адресации. | ||

В зависимости от вида адресации один из адресов поступает на | В зависимости от вида адресации один из адресов поступает на | ||

входы адресного мультиплексора, собранного на микросхемах D31 ...D34 | входы адресного мультиплексора, собранного на микросхемах D31...D34 | ||

Ha четырехвходовую ячейку адресного мультиплексора поступают разря- | Ha четырехвходовую ячейку адресного мультиплексора поступают разря- | ||

ды от младшей и старшей части адреса и младшей и старшей части ви- | ды от младшей и старшей части адреса и младшей и старшей части ви- | ||

| Строка 738: | Строка 737: | ||

но считывается информация из области памяти, называемой видео ЗУ. | но считывается информация из области памяти, называемой видео ЗУ. | ||

Информация, записанная в видео ЗУ, считывается в видеорегистр | Информация, записанная в видео ЗУ, считывается в видеорегистр | ||

D53...D56 , который разделен на старший и младший байт. После защел- | D53...D56, который разделен на старший и младший байт. После защел- | ||

кивания информации сигналом, она последовательно выводится по сигна- | кивания информации сигналом, она последовательно выводится по сигна- | ||

лу C из старшего и младшего байтов и поступает на модулятор. | лу C из старшего и младшего байтов и поступает на модулятор. | ||

| Строка 810: | Строка 809: | ||

затем в линию в виде слова данных (СД). Информация, загружаемая из | затем в линию в виде слова данных (СД). Информация, загружаемая из | ||

микроЭВМ в RGINS БИС АК, посылается в линию в виде командного сло- | микроЭВМ в RGINS БИС АК, посылается в линию в виде командного сло- | ||

ва (КС) | ва (КС) — для АЛС ГЭВМ (ОС) — для АЛС ВЭВМ. | ||

Принимаемая из ЛС информация загружается в RGL БИС АК и может | Принимаемая из ЛС информация загружается в RGL БИС АК и может | ||

быть прочитана в микроЭВМ. Кроме того, БИС АК после принятия из ли- | быть прочитана в микроЭВМ. Кроме того, БИС АК после принятия из ли- | ||

нии сообщения вырабатывает некоторые сигналы, характеризующие это | нии сообщения вырабатывает некоторые сигналы, характеризующие это | ||

сообщение: CHD | сообщение: CHD — определяет достоверность сообщения, CHA — укахыва- | ||

ет на совпадение кода в адресной части КС с собственным адресом БИС | ет на совпадение кода в адресной части КС с собственным адресом БИС | ||

АК, INS - тип сообщения (КС/ОС или СД), SAINS | АК, INS - тип сообщения (КС/ОС или СД), SAINS — наличие определен- | ||

ной комбинации внутри сообщения, МО | ной комбинации внутри сообщения, МО — указывает на наличие общего | ||

(группового) режима. | (группового) режима. | ||

Все указанные сигналы обрабатываются логикой АЛС на основе | Все указанные сигналы обрабатываются логикой АЛС на основе | ||

| Строка 903: | Строка 902: | ||

1.1.9. ГЭВМ входит в программу обслуживания Н4. | 1.1.9. ГЭВМ входит в программу обслуживания Н4. | ||

Этап 1.2 состоит из шагов: | |||

1.2.1. ГЭВМ читает RGD , определяет номер ВЭВМ, потребовавшей | |||

обмена. | |||

1.2.2. ГЭВМ загружает в RGINS КС c пассивным SAINS со стартом. | |||

1.2.3. ГЭВМ запускает программный счетчик на время tож + tобсл | |||

и ждет прихода ОС от ВЭВМ (опрашивает триггер ТРП АЛС ГЭВМ). Здесь | |||

tобсл - время, проходящее с момента обнаружения запроса Н4 до момен- | |||

та приема ОС в АЛС ГЭВМ, tож — время, в течение которого ожидается | |||

освобождение ВЭВМ для обслуживания запроса от АЛС ВЭВМ. | |||

1.2.4. АЛС ВЭВМ получает из сети КС с пассивным SAINS и, если | |||

КС достоверно, то формирует требование прерывания ВЭВМ (если есть | |||

РПР). В микроЭВМ идет запрос H4. | |||

1.2.5. Одновременно с посылкой H4 АЛС ВЭВМ запускает одновибра- | |||

тор на tож. | |||

1.2.6. Если запрос H4 обнаружен до истечения toж, то он начи- | |||

нает обслуживаться в ВЭВМ. | |||

1.2.7. Если H4 не обнаружен до истечения tож, то одновибратор | |||

сбрасывает триггер ТПР. | |||

1.2.8. После этого ГЭВМ ждет еще в течение tобсл на случай, | |||

если запрос ..Н4 успел поступить в ВЭВМ и начал обслуживаться. Если | |||

за это время не пришло ОС от ВЭВМ, то делается выход из этой про- | |||

граммы. Разрешается опрос сети (РОП). | |||

Этап 1.3 состоит из шагов: | |||

1.3.1. Если ВЭВМ успела за toж принять запрос Н4, то она за- | |||

гружает в АЛС ГЭВМ (в RGINS) ОС с информацией, сообщающей в ГЭВМ, | |||

что ВЭВМ готова к обмену. | |||

1.3.2. ГЭВМ, успевшая за toж + tобсл получить OC от ВЭВМ, пере- | |||

ходит на программу собственно обмена с ВЭВМ. | |||

Установление связи по инициативе ГЭВМ выполняется по следующе- | |||

му алгоритму: | |||

2.1. Запрещается аппаратный опрос сети. | |||

2.2. Задается номер ВЭВМ (из ГЭВМ в АЛС ГЭВМ). | |||

2.3. Формируется КС с активным SAINS (co стартом) и записыва- | |||

ется в RGINS АЛС ГЭВМ, тем самым имитируется аппаратный опрос АЛС | |||

ВЭВМ. Далее выполняются п.п. 1.1.4 - 1.1.7. | |||

2.4. Получив аппаратно ответ от АЛС ВЭВМ, АЛС ГЭВМ определяет, | |||

не требовал ли АЛС ГЭВМ обмена. При этом также ведется контроль ожи- | |||

дания ответа (tож + tобсл), если за это время не получено OC, то де- | |||

лается вывод, что АЛС ВЭВМ не включен (неисправен и т.п.). | |||

2.5. Посылается КС с пассивным SAINS, т.е. переход к п.п. | |||

1.2.2 - 1.3.2. | |||

2.6. Получив ответ, ГЭВМ входит собственно в программу обмена | |||

c ВЭВМ. | |||

</pre> | |||

==== 6.3.4. Линейные схемы адаптера локальной сети ==== | |||

<pre> | |||

Схема передатчика АЛС подключается к линейным выходам БИС AK | |||

(D30) (выходы INSD и DINS). Передающими элементами являются | |||

буферные каскады ( D32.2-3 ) c повышенной нагрузочной способностью. | |||

Для повышения выходного тока после элементов D32.2-3 включены кас- | |||

кады транзисторов VT1, VT2. | |||

Схема приемника подключается входами к приемной обмотке, a вы- | |||

ходами — к линейным входам БИС АК ( DINS, INSD ). Ha время работы | |||

передатчика АЛС его приемник отключается, чтобы БИС АК не принимал | |||

в RGL свои передаваемые сообщения. Все остальное время приемник | |||

воспринимает передаваемые по линии сообщения. В качестве приемника | |||

использованы микросхемы D37 и D46. | |||

</pre> | </pre> | ||

==== 6.5 | ==== 6.3.5. Форматы служебных сообщений ==== | ||

<pre> | <pre> | ||

Командное слово/ответное слово имеет следующий формат. | |||

Биты 15-11 — код адреса АЛС ВЭВМ (в КС — это номер АЛС ВЭВМ, | |||

к которой послано КС, в | к которой послано КС, в ОС — это номер АЛС, пославшего ОС). | ||

Биты 7-4 — биты SAINS. Комбинации 0000 и 1111 — это активный | |||

SAINS. Кроме того, бит | SAINS. Кроме того, бит 6 — разрешение прерывания (РПР) устанавли- | ||

вает триггер РПР в АЛС. | вает триггер РПР в АЛС. | ||

Бит 9 — для АЛС ГЭВМ должен устанавливаться в "1". От АЛС ВЭВМ | |||

в линию идет ОС с | в линию идет ОС с "0" в 9-м бите. | ||

Бит 1 — установка триггера разрешения опроса/триггера актив- | |||

ности (РОП/АКТ). | ности (РОП/АКТ). | ||

Бит 0 — установка триггера разрешения опроса/триггера актив- | |||

ности (РОП/АКТ). | |||

При чтении регистра состояния АЛС доступны следующие биты: | |||

Бит 15 — триггер ошибки (ОШ) — чтение со сбросом. | |||

Бит 5 — триггер требования прерывания (TПP) — чтение со сбросом. | |||

Бит 4 — выход СНД БИС АК. | |||

Бит 3 — выход МО БИС AK. | |||

Бит 2 — выход INS БИС AK. | |||

Бит 1 — триггер РОП/АКТ. PМП=ГЭВМ; РМУ=ВЭВМ. | |||

</pre> | </pre> | ||

| Строка 967: | Строка 1033: | ||

ределяют режим и условия работы таймера, разряды его по сигналу | ределяют режим и условия работы таймера, разряды его по сигналу | ||

СБРОС устанавливаются в "0" и имеют следующее значение: | СБРОС устанавливаются в "0" и имеют следующее значение: | ||

разряд 0 | разряд 0 — разряд полезный пользователю; | ||

разряд 1 | разряд 1 — режим работы 1-го счетчика. Если значение этого | ||

разряда 0, то канал 1-го счетчика работает в режиме программируемо- | разряда 0, то канал 1-го счетчика работает в режиме программируемо- | ||

го интервального таймера, если | го интервального таймера, если — 1, то в режиме программируемого | ||

делителя частоты; | делителя частоты; | ||

разряды 2 и 3 | разряды 2 и 3 — определяют режим пуска 1-го счетчика. Если | ||

значения этих разрядов соответственно равны 1 и 0, то | значения этих разрядов соответственно равны 1 и 0, то 1-й счетчик | ||

запускается по управляющему входу СО1 (при СО1=0 1 счетчик начи- | запускается по управляющему входу СО1 (при СО1=0 1 счетчик начи- | ||

нает отсчет), если значения равны 0 и 1, то работа 1 счетчика бло- | нает отсчет), если значения равны 0 и 1, то работа 1 счетчика бло- | ||

кируется, а если значения равны 1 1, то запуск счетчика происходит | кируется, а если значения равны 1 1, то запуск счетчика происходит | ||

по тактовому входу С1; | по тактовому входу С1; | ||

разряды 4 и 5 | разряды 4 и 5 — определяют режим пуска 2 счетчика. Если зна- | ||

чения этих разрядов соответственно равны 1 и 0, то запуск 2 счетчи- | чения этих разрядов соответственно равны 1 и 0, то запуск 2 счетчи- | ||

ка происходит по управляющему входу С2, и если значения равны 0 | ка происходит по управляющему входу С2, и если значения равны 0 | ||

и 1, то работа 2 счетчика блокируется; | и 1, то работа 2 счетчика блокируется; | ||

разряд 6 | разряд 6 — блокировка выдачи сигнала ЗПР1. Если значение | ||

равно 1, то происходит блокировка выдачи сигнала ЗПР1; | равно 1, то происходит блокировка выдачи сигнала ЗПР1; | ||

разряд 7 | разряд 7 — блокировка выдачи сигнала ЗПР2. Если значение | ||

равно 1, то происходит блокировка выдачи сигнала ЗПР2; | равно 1, то происходит блокировка выдачи сигнала ЗПР2; | ||

разряды 8 и 9 | разряды 8 и 9 — фиксация прерывания соответственно 1 и 2 | ||

счетчика. | счетчика. | ||

Код деления частоты и код временного интервала заносится в | |||

таймер D5 непосредственно с шестнадцатиразрядной магистрали данных | |||

(Д0-Д15). Центральный процессор устанавливает данные на шинах Д0-Д15‚ | |||

которые записываются в таймер D5 по принципу сигналов (с селектора | |||

адреса D1) BK1...BK3 и 4Т, после чего таймер информирует селектор | |||

адреса об окончании записи данных установкой сигнала ОТВ в "0". Ce- | |||

лектор, получив сигнал ОТВ=0, информирует центральный процессор об | |||

окончании записи данных и устанавливает сигнал на входе 4Т D5 в "1", | |||

по которому таймер D5 устанавливает сигнал 0ТВ в "1". Ha этом запись | |||

данных в таймер заканчивается. | |||

По прохождении числа тактовых импульсов, соответствующих коду | |||

временного интервала микросхема D42 выдает сигнал ЗПР1 (ЗПР2), кото- | |||

рый снимается сигналом ППP1 (ППP2), поступающим от центрального | |||

процессора. | |||

На триггере D43 выполнен регистр управляющего слова схемы вы- | |||

бора уровня громкости и октавы. Запись в него происходит по адресу | |||

170030. В разряды D1, D2, D3 заносится код октавы, при этом на | |||

выход мультиплексора D45 поступает последовательность импульсов с | |||

одного из выходов ЧД1...ЧД6 микросхемы D42. В разряды D4, D5 реги- | |||

стра D43 заносится код уровня громкости. Этот код подается на уп- | |||

равляемый делитель, выполненный на элементах микросхемы D7, резисто- | |||

рах R2...R5 и транзисторе VT1. Разряд P6 регистра D6 используется | |||

для блокировки выдачи центральному процессору сигнала прерывания. | |||

Ha D-триггере D41.1 выполнена схема разрешения подачи сигналов | |||

с выхода мультиплексора D45 на схему управляемого делителя. Причем | |||

при обращении к таймеру по адресу 170026 триггер D41.1 устанавлива- | |||

ется в единичное состояние, a при каждом обращении по адресу 170032 | |||

происходит переключение триггера в противоположное состоящие. Регу- | |||

лировка громкости таймера производится потенциометром R1, выведенным | |||

на переднюю панель блока системного. | |||

</pre> | |||

=== 6.4. Модуль электронный 2МБ === | |||

<pre> | |||

Модуль электронный 2МБ5, основным узлом которого является узел | |||

печатный 3.219.002 Э3, предназначен для обеспечения электронных | |||

устройств постоянным напряжением 5 B при токе нагрузки до 1,5 A. | |||

Модуль электронный 2МБI2, основным узлом которого является узел пе- | |||

чатный 687281.005, обеспечивает постоянное напряжение 12 B при то- | |||

ке нагрузки до 2 A. Принципиальных отличий в схемах 2МБ5 и 2МБI2 | |||

нет. Модуль представляет собой регулируемый преобразователь напряже- | |||

ния c широтно-импульсным методом стабилизации выходного напряжения. | |||

На входе и выходе модуля подключаются помехоподавляющие фильтры С1...С8, | |||

L1 и С24...С30, L4, ослабляющие распространение помех во входные и вы- | |||

ходные цепи. Питание модуля осуществляется от нестабилизированного | |||

выпрямителя с напряжением 27 B. На элементах VD1, VD4, VT3, VT4, R1, | |||

R4 собран стабилизатор напряжения для питания двухтактного автогене- | |||

ратора на VT1, VT2, TI. Стабилизатор напряжения состоит из токостаби- | |||

лизирующего двухполосника VD1, VD2, R1, R4, VT3, источника опорного | |||

напряжения VD3, VD4, эмиттерного повторителя на VT4. | |||

Двухтактный автогенератор выполнен по схеме с насыщающимся | |||

трансформатором на элементах VT1, VT2, VD5, R2, R3, R5, TI. Прямо- | |||

угольные импульсы с частотой 50 кГц с обмоток 8-9 и 9-10 трансформа- | |||

тора TI выпрямляются диодами D10, D11 и сглаживаются конденсато- | |||

ром С11. Полученное положительное напряжение 6,3 B питает микросхе- | |||

мы D1, D2‚ D3 и однотактный преобразователь на VT5, R9, C12, VD8, T2, VD12. | |||

Выпрямленное диодами VD7, VD9 отрицательное напряжение сглаживает- | |||

ся конденсатором C14. Полученное отрицательное напряжение -6‚3 В пи- | |||

тает микросхемы D1‚ D2‚ D3. | |||

C однополупериодного выпрямителя на VD6 и конденсатора C13 по- | |||

ложительное напряжение подается на параметрический стабилизатор, | |||

собранный на R14, VD17. Полученное образцовое напряжение 9 В по- | |||

дается на вход 11 D2 и вход 10 D3. Однотактный преобразователь на- | |||

пряжения выполнен на элементах VT5, R9, C12, VD8, VD12‚ T2. Пос- | |||

ле запирания VT5, энергия, накопленная в Т2, возвращается через | |||

обмотку 1-2 T2 и диод VD8 во входной источник (VD10, VD11‚ С11). | |||

Импульсы с обмотки 4-5 T2 усиливаются в однотактном транзи- | |||

сторном усилителе мощности на элементах R6...R8, VT6‚ VT7, | |||

VD13...VD15. Дроссель L2 развязывает стабилизатор напряжения от уси- | |||

лителя мощности. Обмотка 1-2 ТЗ также возвращает накопленную энергию | |||

T3 во входную цепь. В схеме VD14 отпирается при открывании VT6, | |||

VT7 и передает энергию в нагрузку через отталкивающий фильтр L3, | |||

C16, C17. | |||

Выходное напряжение подается через делитель: R23, R24, R25, R19 | |||

на вход 11 микросхемы D3 и сравнивается с образцовым, подающимся на | |||

вход 10 микросхемы D3. Управляющее напряжение с выхода 7 микросхемы | |||

D3 через VD18, R30 подается на вход 10 микросхемы D1. На вход 11 | |||

микросхемы D1 подается напряжение линейно изменяющейся формы. | |||

Выходное напряжение c выхода 7 микросхемы D1 управляет рабо- | |||

той однотактного преобразователя на VT5. Схема защиты от КЗ на вы- | |||

ходе модуля электронного выполнена на D2. | |||

Ha вход 11 микросхемы D2 с делителя R13, R12 подается образцо- | |||

вое напряжение с параметрического стабилизатора R14, VD17. C помощью | |||

резистора R11 устанавливается порог ограничения тока нагрузки. Ток | |||

нагрузки, протекая через R28‚ R29‚ создает на нем падение напряжения, что | |||

приводит к изменению напряжения на выходе 7 микросхемы D2. Через VD16 | |||

и R16 управляющее напряжение передается на вход 10 микросхемы D1‚ что | |||

приводит к уменьшению выходного напряжения и установлению тока корот- | |||

кого замыкания, равного току ограничения, устанавливаемого резистора- | |||

ми R28, R29 и R11. | |||

</pre> | </pre> | ||

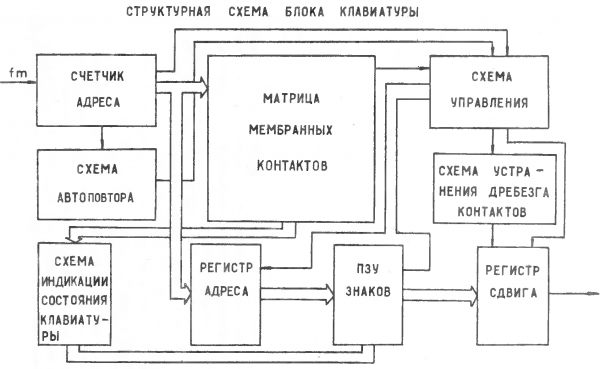

=== 6.5. Блок клавиатуры === | === 6.5. Блок клавиатуры === | ||

... | <pre> | ||

Блок клавиатуры 3.059.007 предназначен для ввела команд и данных. | |||

Блок обеспечивает формирование 8-разрядных двоичных кодов букв рус- | |||

ского и латинского алфавита (прописных и строчных), цифр и других | |||

символов, нанесенных на клавиши. В состав клавиатуры входят: | |||

устройство коммутирующее 5.280.064; | |||

плата управления клавиатурой 6.120.112. | |||

Устройство коммутирующее представляет собой матрицу мембранных | |||

контактов. | |||

Плата управления клавиатурой состоит из следующих функциональ- | |||

ных узлов: | |||

счетчика адреса; | |||

регистра адреса; | |||

ПЗУ знаков; | |||

схемы индикации состояния клавиатуры; | |||

схемы управления; | |||

схемы устранения дребезга контактов; | |||

регистра сдвига; | |||

схемы автоповтора. | |||

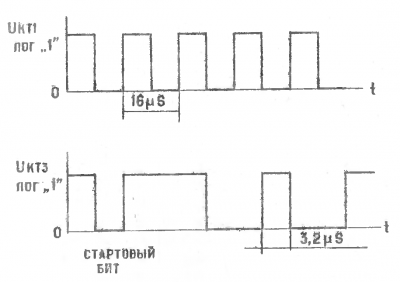

По принципу действия блок клавиатуры относится к клавиатурам на | |||

основе сканируемой матрицы. | |||

Сканируемая матрица (матрица мембранных контактов) представля- | |||

ет собой набор замыкающих контактов. Матрица имеет организацию 12 | |||

строк на 8 столбцов, а также одиночные контакты. Структурная схема | |||

блока клавиатуры приведена на рис.10. | |||

С помощью счетчика адреса происходит последовательный опрос мат- | |||

рицы мембранных контактов. В случае обнаружения нажатой клавиши ад- | |||

рес клавиши фиксируется в регистре адреса. Этот адрес поступает на | |||

ПЗУ знаков, где хранятся коды символов. Сюда же поступает код со схе- | |||

мы индикации состояния клавиатуры, которая предназначена для уста- | |||

новки режима работы клавиатуры и его индикации. | |||

Параллельный код символа, соответствующий адресу нажатой клави- | |||

ши, считывается из ПЗУ знаков и поступает на регистр сдвига, где пре- | |||

образуется в последовательный код и поступает на выход блока. Выход- | |||

ные коды символов приведены в приложении. | |||

Схема автоповтора предназначена для организации выдачи кода сим- | |||

волов с частотой около 15 Гц при длительном (более 1 сек) нажатии на | |||

какую-нибудь клавишу. | |||

Схема устранения дребезга контактов устраняет ложное срабатыва- | |||

ние блока клавиатуры при нажатии на клавиши. Схема управления форми- | |||

рует управляющие и синхронизирующие сигналы, необходимые для работы | |||

всего блока клавиатуры. | |||

Описание всего блока работы клавиатуры по принципиальной схеме. | |||

Ha вход счетчика адреса (микросхема D1) поступают тактовые им- | |||

пульсы частотой 62,5 кГц с блока системного. На выходах счетчика фор- | |||

мируется адрес в двоичном коде, изменяющийся через такт (так как | |||

младший разряд кода не используется для адресации). Старшие 3 разряда | |||

кода поступают на адресные входы демультиплексоров D10, D11. Демуль- | |||

типлексоры работают поочередно. Импульсная последовательность (с ча- | |||

стотой в 2 раза меньше тактовой), поступающая на входы демультиплек- | |||

соров, проходит на их выходы, которые соединены с шинами строк матри- | |||

цы мембранных контактов. Шины столбцов матрицы соединены со входами | |||

мультиплексора D14. На адресные входы этого мультиплексора поступают | |||

</pre> | |||

[[Файл:NemigaTO-pic10.png|600px]] | [[Файл:NemigaTO-pic10.png|600px]] | ||

<pre> | |||

Рис. 10 | |||

... | младшие разряды адресного кода. Таким образом сканирование обеспе- | ||

чивается последовательным опросом 12 строк матрицы выходными сигна- | |||

лами с демультиплексоров и поиском мультиплексором нажатой клавиши во | |||

всех 8 местах для каждой из этих строк. | |||

При нажатии любой из клавиш (кроме клавиш, не входящих в матри- | |||

цу) на выходе мультиплексора D14 появляются импульсы, частота кото- | |||

рых в 96 раз меньше частоты спроса матрицы. Частота спроса равна | |||

31,25 кГц. Конденсатор C5 служит для устранения помех, возникающих | |||

при работе цифровых микросхем. | |||

На элементах D7.3, D4.3, D9.1, D5.2, D5.3, D6.1 собрана | |||

схема управления записью адресного когда в регистр адреса. В исход- | |||

ном состоянии на инверсном выходе триггера D3.2 высокий уровень. | |||

При нажатии какой-либо клавиши на выходе инвертора D5.2 появляются | |||

импульсы, которые устанавливают триггер D9.1 в единичное состояние. | |||

Элементы D7.3, D4.3 формируют сигнал конца опроса матрицы мембран- | |||

ных контактов, по переднему фронту которого логическая единица со | |||

входа триггера D3.2 проходит на его выход, при этом на инверсном | |||

выходе D3.2 появляется низкий уровень, который устанавливает триг- | |||

гер D9.1 в нулевое состояние. Низкий уровень на выходе триггера D3.2 | |||

закрывает элемент D5.3, что обеспечивает формирование на выходе D5.3 | |||

одиночного импульса из группы импульсов. Конденсатор С3 необходим | |||

для устранения помех, возникающих при переключении элемента D7.3. | |||

Регистр адреса (D15, D16) служит для хранения адреса нажатой | |||

клавиши. Запись адресного кода в регистр адреса проходит по импуль- | |||

су, приходящему с выхода D5.3 через инвертор D6.1 после нажатия | |||

клавиши. С выхода регистра адреса код поступает на адресные входы | |||

ПЗУ знаков (микросхема D17). Кроме кода с регистра адреса, на ад- | |||

ресные входы ПЗУ А7-А10 поступает код со схемы индикации состояния | |||

клавиатуры, который зависит от режима работы клавиатуры. В эту схему | |||

входят: RS-триггер на элементах D6.3, D7.1 (для установки режима | |||

"ЦИФ" или "ДОП". R3-триггер на элементах D6.4, D7.2, D8.1, D8.2 | |||

(для установки режимов "РУС" или "ЛАТ"), триггер D13.1 и элементы | |||

D8.3, D8.4 (для установки режима "ВЕРХ"). На триггере D9.2 собра- | |||

на схема устранения дребезга, возникающего при нажатии клавиши "ФПБ". | |||

Резистор RЗС, конденсатор С1 и инвертор D12.4 образуют схему началь- | |||

ной установки режимов работы клавиатуры при включении питания (уста- | |||

навливаются режимы "ЛАТ", "ВЕРХ", "ЦИФ"). Режим работы отображается | |||

на светодиодных индикаторах VD1 - VD4, включенных через ключи на | |||

транзисторах VT1-VT4. С выхода ПЗУ знаков параллельный код нажа- | |||

той клавиши поступает на входы данных регистра сдвига (D18 - D20) | |||

для преобразования в последовательный код, который по гибкому кабелю | |||

поступает в системный блок. На вход 8 регистра D20 подан высокий | |||

уровень для формирования стартового бита. Сигнал разрешения на запись | |||

в регистр данных приходит с триггера D13.2 , которым управляет триг- | |||

гер D9.3 При кратковременном нажатии какой-либо клавиши импульс за- | |||

писи в регистр адреса проходит через элемент D5.4, так как на выво- | |||

де 9 этого элемента высокий уровень. Триггер D9.3 устанавливается в | |||

единичное состояние. По переднему фронту синхроимпульса триггер D13.2 | |||

также устанавливается в единичное состояние и стартовый бит появля- | |||

ется на выводе 13 регистра D16, затем поступает на схему устранения | |||

дребезга мембранных контактов, собранную на триггере D9.4. Пройдя | |||

схему устранения дребезга, стартовый бит сбрасывает в нулевое состоя- | |||

ние триггеры D9.3. D13.2 и на выходе регистра сдвига появляется по- | |||

следовательный код нажатой клавиши. После инвертора D12.2 сформиро- | |||

ванный код поступает на выход блока клавиатуры. | |||

Схема автоповтора работает следующим образом. В исходном состоя- | |||

нии триггер D3.1 установлен в нулевое состояние высоким уровнем с | |||

триггера D3.2. При нажатии клавиши на входе установки в ноль тригге- | |||

ра D3.1 низкий уровень. Если клавиша нажата более 1 сек, то на выводе | |||

14 счетчика D2 появляется импульс, который, пройдя инвертор D4.1 пе- | |||

редним фронтом, устанавливает триггер D3.1 в единичное состояние. В | |||

этом случае импульсы частотой около 15 Гц с вывода 6 счетчика D2 про- | |||

ходят через элемент D5.1 и поступают на элемент D5.4, разрешаю- | |||

щий запись кода символа в регистр сдвига. Таким образом при длитель- | |||

ном нажатии клавиши на выходе блока появляется последовательный код | |||

символа, повторяющийся с частотой около 15 Гц. | |||

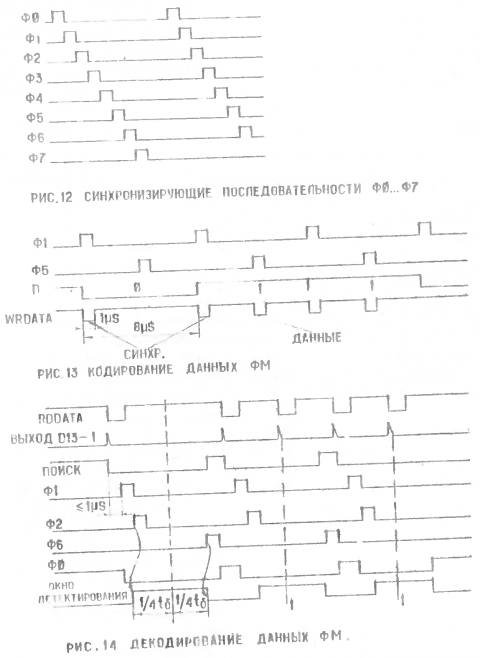

Временные диаграммы напряжений в контрольных точках приведены | |||

в приложении 2. | |||

</pre> | |||

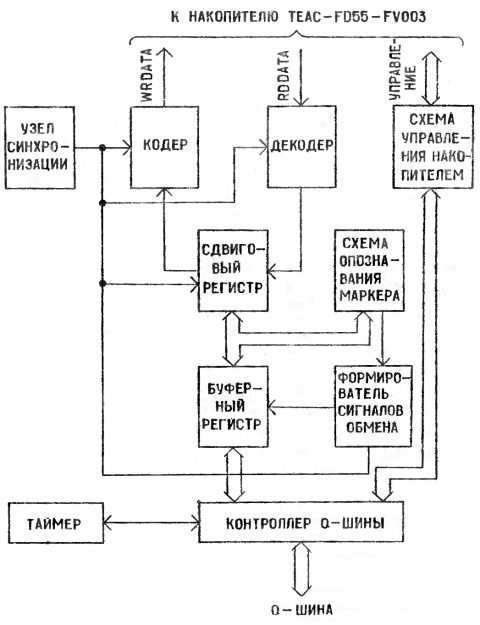

=== 6.6. Накопитель на гибких магнитных дисках === | === 6.6. Накопитель на гибких магнитных дисках === | ||

| Строка 1116: | Строка 1394: | ||

цессору информации о текущем состоянии контроллера накопителя. Фор- | цессору информации о текущем состоянии контроллера накопителя. Фор- | ||

мируются следующие сигналы: | мируются следующие сигналы: | ||

RELOAD | RELOAD — устанавливается при пропадении сигнала READY (готов- | ||

ность) от накопителя. Возможные причины: неисправность | ность) от накопителя. Возможные причины: неисправность | ||

накопителя, пропадание питающего напряжения привода, | накопителя, пропадание питающего напряжения привода, | ||

| Строка 1126: | Строка 1404: | ||

восстановился сигнал READY (D11.5, D7.3, D17.1, | восстановился сигнал READY (D11.5, D7.3, D17.1, | ||

D33). | D33). | ||

OP-FAILED | OP-FAILED — аварийное прекращение операции. Устанавливается при | ||

появлении сигнала RELOAD во время выполнения опера- | появлении сигнала RELOAD во время выполнения опера- | ||

ции чтения-записи. Удерживается до конца дорожки | ции чтения-записи. Удерживается до конца дорожки | ||

(D24.3, D33). | (D24.3, D33). | ||

LOST-DATA | LOST-DATA — потеря данных. Устанавливается, если от момента по- | ||

явления сигнала TR до операции обмена прошло более | явления сигнала TR до операции обмена прошло более | ||

64 мкс. Сбрасывается по команде RUN (пуск). (D29.1, | 64 мкс. Сбрасывается по команде RUN (пуск). (D29.1, | ||

| Строка 1170: | Строка 1448: | ||

гистра, доступных по чтению и записи. КОнтроллер рассчитан только на | гистра, доступных по чтению и записи. КОнтроллер рассчитан только на | ||

программный обмер наддыми и программный опрос бита требования пере- | программный обмер наддыми и программный опрос бита требования пере- | ||

дачи TR. Цикл обмена данными в режиме чтения | дачи TR. Цикл обмена данными в режиме чтения — записи не должен пре- | ||

вышать 64 мкс. Формат регистра данных | вышать 64 мкс. Формат регистра данных — 1 байт. | ||

Форматы и адреса регистров контроллера: | Форматы и адреса регистров контроллера: | ||

разряды доступны по: ЧТЕНИЮ ЗАПИСИ | разряды доступны по: ЧТЕНИЮ ЗАПИСИ | ||

177100 | 177100 — регистр состояния: | ||

0 RELOAD RUN/STEP | 0 RELOAD RUN/STEP | ||

1 - - | 1 - - | ||

| Строка 1185: | Строка 1463: | ||

7 TR - | 7 TR - | ||

8-15 - - | 8-15 - - | ||

177102 | 177102 — регистр данных: | ||

0-7 ДАННЫЕ ЧТЕНИЯ ДАННЫЕ ЗАПИСИ | 0-7 ДАННЫЕ ЧТЕНИЯ ДАННЫЕ ЗАПИСИ | ||

8-15 - - | 8-15 - - | ||

177104 | 177104 — регистр управления: | ||

0-1 НОМЕР ПРИВОДА | 0-1 НОМЕР ПРИВОДА | ||

2 НОМЕР ПОВЕРХНОСТИ | 2 НОМЕР ПОВЕРХНОСТИ | ||

| Строка 1194: | Строка 1472: | ||

4-5 КОД ОПЕРАЦИИ | 4-5 КОД ОПЕРАЦИИ | ||

6-15 - | 6-15 - | ||

177106 | 177106 — регистр таймера: | ||

0 ПУСК ТАЙМЕРА СОСТОЯНИЕ ТАЙМЕРА | 0 ПУСК ТАЙМЕРА СОСТОЯНИЕ ТАЙМЕРА | ||

1-15 - | 1-15 - | ||

| Строка 1254: | Строка 1532: | ||

Разряды [5,4] регистра управления определяются следующими ко- | Разряды [5,4] регистра управления определяются следующими ко- | ||

дами операций: | дами операций: | ||

00 | 00 — ЧТЕНИЕ дорожки; | ||

10 | 10 — ЗАПИСЬ дорожки; | ||

01 | 01 — ШАГ НАЗАД (от центра дискеты); | ||

11 | 11 — ШАГ ВПЕРЕД (к цендру дискеты). | ||

При установке бита RELOAD или сигнала сброса канала ЭВМ код | При установке бита RELOAD или сигнала сброса канала ЭВМ код | ||

текущей операции может быть изменен. | текущей операции может быть изменен. | ||

Любая запись в регистр таймера запускает одновибратор. В тече- | Любая запись в регистр таймера запускает одновибратор. В тече- | ||

ние 3...3 | ние 3...3,5 мс после записи бит 0 регистра таймера установлен в "1". | ||

Устройство сопряжения ПК с печатающим устройством имеет выход | |||

на интерфейс типа ИРПР (байтовый параллельный интерфейс) и включает | |||

в себя следующие узлы: | |||

1) контроллер байтового параллельного интерфейса, осуществляю- | |||

щий передачу информации с помощью регистров состояния и буферного | |||

регистра и выполнен на БИС KP1801 BП1-033 (D41) и элементах D38.5 | |||

и D40; | |||

2) буферный регистр ( D42, D43 ), предназначенный для хранения | |||

кода символа, передаваемого на печатающее устройство; | |||

3) приемопередатчик, собранный на элементах D38.3, D38.4, | |||

D39.1, D39.2; | |||

4) выходные усилители, собранные на элементах D45. D44.3, | |||

D44.5; | |||

C точки зрения программиста устройство сопряжения представляет | |||

собой два регистра, доступных по чтению и записи. Оно рассчитано на | |||

программный обмен данными и обмен по прерыванию. Формат регистра | |||

данных - 1 байт. | |||

177514 — адрес регистра состояния: | |||

разряды, допустимые по: чтение записи | |||

0 - 4 - - | |||

5 ЗВРШ - | |||

6 РПР РПР | |||

7 требование передачи - | |||

8 - 13 - начальная установка | |||

14 - - | |||

15 ошибка | |||

177516 — адрес регистра данных: | |||

разряды, допустимые по: чтение записи | |||

0 - 17 - данные | |||

8 - 15 - - | |||

</pre> | </pre> | ||

... | === 6.8. Конструкция === | ||

<pre> | |||

Персональный компьютер, внешний вид которого приведен на риc.1, | |||

выполнен в виде пяти блоков: блока системного, блока клавиатуры, ВКУ, | |||

ГМД и печатающего устройства. | |||

Блок системный и накопитель НГМД-I выполнен в виде переносного | |||

прибора бесфутлярной конструкции. Элементы корпуса крепятся между | |||

собой винтами. Передняя и задняя панели крепятся к основным несущим | |||

кронштейнам. Внутри блока системного расположены: блок комбинирован- | |||

ный с тремя платами (модуль процессора, модуль ОЗУ и модуль ЛС) и | |||

два модуля электронных 2МБ для питания узлов ПК и ВКУ. Внутри НГМД-I | |||

расположены: два дисковода, плата модуля сопряжения и два модуля | |||

электронных 2МБ для питания узлов НГМД-I. Соединение составных ча- | |||

стей ПК осуществляется кабелями. | |||

Блок системный имеет следующие органы управления и розетки: | |||

на передней панели - кнопки переключателей СЕТЬ, ПУСК, ТАЙМЕР; | |||

ручка регулятора громкости звука таймера; | |||

на задней панели - розетки ЛОКАЛЬНАЯ СЕТЬ, ВКУ, УВИ, МПИ; | |||

переключатель N РМУ; | |||

НГМД-I имеет следующие органы управления и розетки: | |||

на передней панели - фиксаторы дисководов; | |||

на задней панели - кнопка переключателя СЕТЬ, розетки МПИ, ЦПУ. | |||

Блок клавиатуры выполнен в виде отдельного блока. Несущим эле- | |||

ментом в блоке является устройство коммутирующее c двумя боковыми | |||

кронштейнами. | |||

</pre> | |||

== 7. МАРКИРОВАНИЕ И ПЛОМБИРОВАНИЕ == | == 7. МАРКИРОВАНИЕ И ПЛОМБИРОВАНИЕ == | ||

| Строка 1286: | Строка 1623: | ||

== Приложение 1. == | == Приложение 1. == | ||

... | <pre> | ||

Система команд ЦП | |||

Таблица 1 | |||

───────────────────┬───────────────┬─────────────────────┬───────── | |||

Код команды │ Признаки │ Содержание команды │ Номер | |||

──────────┬────────┼───┬───┬───┬───┤ │кодировки | |||

Мнемоника │8-ричный│ N │ Z │ V │ C │ │ | |||

──────────┼────────┼───┼───┼───┼───┼─────────────────────┼───────── | |||

CLR (A) |*050DD | 0 | 1 | 0 | 0 |Очистка | 0001 | |||

COM (A) |*051DD | + | + | 0 | 1 |Инвертирование | 0001 | |||

INC (A) |*052DD | + | + | + | - |Инкрементация | 0001 | |||

DEC (A) |*053DD | + | + | + | - |Декрементация | 0001 | |||

NEG (A) |*054DD | + | + | + | + |Дополнение | 0001 | |||

ADC (A) |*055DD | + | + | + | + |Сложение с переносом | 0001 | |||

SEC (A) |*056DD | + | + | + | + |Вычитание переноса | 0001 | |||

TST (A) |*057DD | + | + | 0 | 0 |Проверка | 0001 | |||

ROR (A) |*060DD | + | + | + | + |Сдвиг цикл.правый | 0001 | |||

ROL (A) |*061DD | + | + | + | + |Сдвиг цикл.левый | 0001 | |||

ASR (A) |*062DD | + | + | + | + |Сдвиг арифм.правый | 0001 | |||

ASL (A) |*063DD | + | + | + | + |Сдвиг арифм.левый | 0001 | |||

MOV (A,B) |*1SSDD | + | + | 0 | - |Пересылка | 0001 | |||

CMP (A,B) |*2SSDD | + | + | + | + |Сравнение | 0001 | |||

BIT (A,B) |*3SSDD | + | + | 0 | - |Проверка разрядов | 0001 | |||

BIC (A,B) |*4SSDD | + | + | 0 | - |Очистка разрядов | 0001 | |||

BIS (A,B) |*5SSDD | + | + | 0 | - |Логическое "ИЛИ" | 0001 | |||

ADD (A,B) |06SSDD | + | + | + | + |Сложение | 0001 | |||

SUB (A,B) |16SSDD | + | + | + | + |Вычитание | 0001 | |||

| | | | | | | | |||

NOP |000240 | | | | |Нет операции | 0002 | |||

CLC |000241 | - | - | - | 0 |Очистка "С" | 0002 | |||

CLV |000242 | - | - | 0 | - |Очистка "V" | 0002 | |||

CLZ |000244 | - | 0 | - | - |Очистка "Z" | 0002 | |||

CLN |000250 | 0 | - | - | - |Очистка "N" | 0002 | |||

SEC |000261 | - | - | - | I |Установка "С" | 0002 | |||

SEV |000262 | - | - | I | - |Установка "V" | 0002 | |||

SEZ |000264 | - | I | - | - |Установка "Z" | 0002 | |||

SEN |000270 | I | - | - | - |Установка "N" | 0002 | |||

SCC |000277 | I | I | I | I |Установка "С", "V" | 0002 | |||

| | | | | | "Z", "N" | | |||

CCC |000257 | 0 | 0 | 0 | 0 |Очистка "С", "V" | 0002 | |||

| | | | | | "Z", "N" | | |||

SWAB |0003DD | + | + | 0 | 0 |Перестановка байтов | 0002 | |||

MARK |0064NN | - | - | - | - |Восстановление указа-| 0002 | |||

| | | | | |теля стека | | |||

XOR (R,A) |074RDD | + | + | 0 | - |Исключающее "ИЛИ" | 0002 | |||

BR (A) |0004XXX | |Ветвление безусловное| 0002 | |||

BNE (A) |0010XXX | Z=0 |Ветвление, если =0 | 0002 | |||

BEQ (A) |0014XXX | Z=1 |Ветвление, если =0 | 0002 | |||

BGE (A) |0020XXX | NOV=0 |Ветвление, если >0 | 0002 | |||

BLT (A) |0024XXX | NOV=1 |Ветвление, если <0 | 0002 | |||

BGT (A) |0030XXX | ZV(NOV)?0 |Ветвление, если >0 | 0002 | |||

BLE (A) |0034XXX | ZV(NOV)=1 |Ветвление, если <0 | 0002 | |||

SOB (A) |077RNN | Z=0 |Вычитание единицы, | 0002 | |||

| | |если результат =0 | 0002 | |||

BLR (A) |1000XXX | N=0 |Ветвление, если + | 0002 | |||

BMI (A) |1004XXX | N=1 |Ветвление, если - | 0002 | |||

BHI (A) |1010XXX | ZVC=0 |Ветвление, если > | 0002 | |||

BLOS (A) |1014XXX | ZVC=1 |Ветвление, если < | 0002 | |||

BVC (A) |1020XXX | V=0 |Ветвление, если нет | 0002 | |||

| | |переполнения | 0002 | |||

BVS (A) |1024XXX | V=I |Ветвление, если | 0002 | |||

| | |переполнение | 0002 | |||

BHIS (A) |1030XXX | C=0 |Ветвление, если нет | 0002 | |||

| | |переноса | | |||

BLO (A) |1034XXX | C=I |Ветвление, если | 0002 | |||

| | |перенос | | |||

MUL (R,A) |070RSS | + | + | 0 | + |Умножение | 0006 | |||

DIV (R,A) |071RSS | + | + | + | + |Деление | 0006 | |||

ASH (R,A) |072RSS | + | + | + | + |Многоразрядный сдвиг | 0006 | |||

ASHC (R,A)|073RSS | + | + | + | + |Сдвиг комбинированный| 0006 | |||

HALT |000000 | |Останов | 0004 | |||

WAIT |00000I | |Ожидание | 0004 | |||

RTI |000002 | |Возврат из прерыва- | 0004 | |||

| | |ния | | |||

BPT |000003 | |Прерыв.для отладки | 0004 | |||

IOT |000004 | |Прерыв.для ВВ/ВЫВ | 0004 | |||

RESET |000005 | |Сброс | 0004 | |||

RTT |000006 | |Возврат из прерыва- | 0004 | |||

| | |ния | | |||

JMP (A) |0001DD | |Безусловный переход | 0004 | |||

RTS (R) |00020R | |Возврат из подпрогр. | 0004 | |||

JSR (R,A) |0004RDD | |Переход к подпрограм-| 0004 | |||

| | |ме | | |||

EMT |104000- | |Командное прерывание | 0004 | |||

|104377 | | | | |||

SXT (A) |0067DD | - | + | 0 | - |Расширение знака | 0002 | |||

MTPS (A) |1064SS | + | + | + | + |Запись ССП | 0002 | |||

MFPS (A) |1067DD | - | + | 0 | - |Чтение ССП | 0002 | |||

TRAP |104400- | | | | |Командное прерывание | 0004 | |||

|104777 | | | | | | | |||

П р и м е ч а н и я: | |||

1. R - восьмеричный код РОН (0-7); | |||

SS - поле адресации операнда источника; | |||

DD - поле адресации операнда приемника; | |||

* - операция производится над байтом, если * = 1 | |||

над словом, если * = 0; | |||

XXX - смещение (8 разрядов); | |||

NN - смещение (6 разрядов). | |||

2. В графе "признаки" указаны значения признаков N,Z и C,V | |||

слова состояния процессора, которые устанавливаются после выполнения | |||

процессором каждой команды. Знак "+" означает, что данный разряд ССП | |||

будет установлен в "0" или "1" в зависимости от результата выполне- | |||

ния команды. Знак "-" означает, что команда не оказывает воздействия | |||

на данный разряд ССП. | |||

3. B графе 8 указан номер кодировки микросхемы КР588ВУ2‚ отве- | |||

чающей за выполнение соответствующей команды. | |||

</pre> | |||

== Приложение 2. == | == Приложение 2. == | ||

.. | <pre> | ||

Временные диаграммы напряжений в контрольных точках | |||

Блок клавиатуры 3.059.007 | |||

</pre> | |||

[[Файл:NemigaTO-app2.png|400px]] | [[Файл:NemigaTO-app2.png|400px]] | ||

... | <pre> | ||

П р и м е ч a н и я: I. Временная диаграмма в КТЗ приведена | |||

при нажатой клавише "КЛЮЧ". | |||

2. B контрольной точке КT2 B исходном состоянии - уровень логи- | |||

ческой единицы, a при нажатой любой из клавиш (кроме клавиш выбора | |||

регистров) - уровень логического нуля. | |||

</pre> | |||

== Приложение 3. == | == Приложение 3. == | ||

Текущая версия от 16:56, 23 мая 2020

КОМПЛЕКС ВЫЧИСЛИТЕЛЬНЫЙ "НЕМИГА"

КОМПЬЮТЕРЫ ПЕРСОНАЛЬНЫЕ ПК 588, ПК 588-01

ТЕХНИЧЕСКОЕ ОПИСАНИЕ И ИНСТРУКЦИЯ ПО ЭКСПЛУАТАЦИИ

1.700.005 ТО

Альбом 1

1. ВВЕДЕНИЕ

...

2. НАЗНАЧЕНИЕ

...

3. ТЕХНИЧЕСКИЕ ДАННЫЕ

...

4. СОСТАВ ПЕРСОНАЛЬНОГО КОМПЬЮТЕРА

...

5. УСТРОЙСТВО И РАБОТА ПК

Основным устройством ПК является центральный процессор, который

управляет распределением времени использования канала внешними устройст-

вами и выполняет все необходимые арифметико-логические операции для

обработки информации. Он содержит 16 быстродействующих регистров общего

назначения (РОН), 8 из них (R0...R7) программно доступны, а 8 других

используются как служебные регистры при выполнении микрокоманд.

Центральный процессор выполняет одноадресные команды, двухадресные

команды, команды расширенной арифметики, может обрабатывать как 16-раз-

рядные слова, та к и 8-разрядные байты. Возможность использования 8

методов адресации позволяет вести высокоэффективную обработку данных,

хранимых в любой ячейке памяти или в регистре.

5.1. Регистры общего назначения

Бис АЛУ содержит 16-разрядные РОН, способные выполнять различ- ные функции. Они могут служить в качестве накопительных регистров, индексных регистров, регистров автоинкрементной и автодекрементной адресации и т. д. РОН используются для выборки операндов и записи результатов при выполнении арифметико-логических операций, аналогич- но ячейкам памяти и регистрам внешних устройств. Два из 8 программно- доступных регистров общего назначения R6, R7 имеют, кроме того, спе- циальное назначение. Регистр R6 используется как указатель стека (УС) и содержит адрес последней заполненной ячейки стека. Регистр R7 слу- жит счетчиком команд (СК) и содержит адрес очередной выполняемой ко- манды. Операции по выполнению команд с регистровым методом адресации являются внутренними по отношению к микропроцессору и не требуют вы- полнения циклов обращения к каналу (за исключением цикла выборки ко- манды). Обмен же данными с памятью и внешними устройствами выполня- естся через канал и занимает более длительное время. Таким образом, использование РОН для хранения операндов при процессорных операциях повышает быстродействие ПК.

5.2. Слово состояния процессора

Слово состояния процессора (ССП) содержит информацию о текущем

состоянии процессора. Это информация о текущем приоритете процессо-

ра, значения кодов условий ветвления, зависящем от результата выпол-

нения команды в состоянии Т-разряда, используемого при отладке про-

граммы. На рис.2 показан формат ССП. Разряд приоритета процессора

(7-й разряд ССП) может находиться в состоянии "0" или "1". В по-

следнем случае внешние устройства не могут вызвать прерывание теку-

щей программы.

Коды условий ветвления содержат информацию о результате послед-

ней выполненной процессором команды. Процедуру установки их в соот-

ветстсвующее состояние выполняют все арифметические и логические од-

ноадресные и двухадресные команды.

Установка отдельных разрядов этих кодов выполняется в следующих

случаях:

Z=1, если результат равен 0;

N=1, если результат < 0;

С=1, если в результате выполнения команды произошел перенос

из самого старшего разряда или, если при сдвиге вправо

или влево из самого младшего или самого старшего разря-

да была выдвинута единица;

V=1, если в результате выполнения команды произошло арифмети-

ческое переполнение.

Если T=1, то произойдет прерывание программы с вектором 14.

15 8 7 6 5 4 3 2 1 0

┌─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─-─┬─--┐

│ Р Т N Z V C │

└─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─-─┴─--┘

│ │ │ │ │ │

Разряд приоритета процессора ----┘ │ │ │ │ │

│ │ │ │ │

Прерывание по Т-разряду -----------------┘ │ │ │ │

│ │ │ │

Отрицательный результат ---------------------┘ │ │ │

│ │ │

Нулевой результат ------------------------ ┘ │ │

│ │

Арифметическое переполнение ---------------------------┘ │

│

Перенос старшего байта -------------------------------┘

Рис.2. Формат слова состояния процессора

5.3. Система команд

В центральном процессоре ПК используются три типа команд: без-

адресные, одноадресные и двухадресные. В безадресных командах код

команды содержит только код операции. Формат одноадресных команд

имеет следующий вид:

-┌─-------─┬─---------------------─┬─-------─┐-

| КОП | Метод | РОН |

| | адресации | |

-└─-------─┴─---------------------─┴─-------─┘-

15 6 5 3 2 0

Формат одноадресных команд

Формат двухадресных команд имеет следующий вид:

┌─-----─┬─---------─┬─-----─┬─-----------─┬─---─┐

| КОП | Метод | РОН | Метод | РОН |

| | адресации | | адресации | |

└─-----─┴─---------─┴─-----─┴─-----------─┴─---─┘

15 12 11 9 8 6 5 3 2 0

──--------------── ...................

Поле адресации операнда Поле адресации опе-

источника (SS) ранда приемника (DD)

Формат двухадресных команд

Метод адресации кодируется тремя двоичными разрядами:

Метод адресации

-─┬─----─┬─-----─┬─----─┬─-

| | | |

| | | |

-─┴─----─┴─-----─┴─----─┴─-

| | └─- Признак прямой (0)

| | или косвенной (1)

└- -┬- -┘ адресации

|

└─ - - - Адресации:

00 - регистровая

01 - с автоувеличением

10 - с автоуменьшением

11 - индексная

Таким образом, существует всего 8 способов адресации (4 прямых

и 4 косвенных).

Система команд центрального процессора (ЦП) приведена в прило-

жении 1.

5.4. Программное обеспечение ПК

Для организации взаимодействия структурных компонентов между

собой ПК имеет резидентское программное обеспечение, которое постоян-

но находится в ПЗУ модуля процессора и начинает работать сразу же

после включения питания.

Состав резидентного ПО ПК:

1. Программа холодного старта.

2. Программа взаимодействия ПК в локальной сети.

3. Программа пультового терминала.

4. Программа обработки данных с клавиатуры.

5. Программа вывода символов на экран монитора.

6. Программа HALT-монитора.

7. Программа графических примитивов.

8. Стандартный знакогенератор.

9. Программа обмена данных с периферийными устройствами.

Программа холодного старта начинает работу при нажатии на кноп-

ку "ПУСК". Она устанавливает все устройства, входящие в ПК, в началь-

ное положение и при наличии подключения к каналу ПК платы локальной

сети передает управление программе взаимодействия ПК в локальной

сети. Программа взаимодействия ПК в локальной сети выводит на экран

видеомонитора надпись "ЖДИТЕ" настраивает ПК на прием информации

на локальной сети. При отсутствии платы локальной сети, либо при

одновременном нажатии на клавиши "УПР" и "ФСД/СТОП" (здесь и далее

в таких случаях рекоменуется первой нажать клавишу "УПР" и, зафик-

сировав ее, нажать следующую клавишу) процессор переходит на програм-

му пультового терминала.

Программа пультового терминала непосредственно взаимодействует

с программой обработки данных с клавиатуры, программой вывода сим-

волов на экран видеомонитора, стандартным знакогенератором. При этом

на экране видеомонитора появляется надпись "ПУЛЬТ". В этом режиме

монитор системы отрабатывает следующие директивы, вводимые с клавиа-

туры:

УПР и L - очистка экрана;

S - вывод на экран видеомонитора содержимого регистров

процессора;

D, 1D - загрузка операционной системы в ОЗУ с дисковода

с номером 1;

2D, 3D - загрузка операционной системы в ОЗУ с дисковода

с номером 2;

/ - раскрытие содержимого ячеек памяти;

G - выполнение программы;

N - выход на программу взаимодействия ПК в локальной

сети;

УПР и СТОП - останов выполняемой программы.

Программа вывода символов на экран видеомонитора в режиме вы-

вода алфавитно-цифровой информации формирует 25 строк по 50 символов.

Каждый символ формируется матрицей точек 8х8.

Рис.3. Матрица формирования изображения алфавитно-цифрового

знака на экране видеомонитора

Расстояние между строками формируется программно, путем запол-

нения нулями участка растра, находящегося под знакосинтезирующей

матрицей (рис.3).

Программа графических примитивов формирует изображение точки

и линии при выводе графической информации на экран видеомонитора.

5.5. Работа канала персонального компьютера

Персональный компьютер имеет модульный принцип построения, т.е.

все функциональные блоки ПК выполнены в виде конструктивно закончен-

ных устройств (модулей), связь между которыми осуществляется через

единый канал обмена информацией. Канал обмена информацией является

простой быстродействующей системой связей, соединяющей процессор,

память и все внешние устройства.

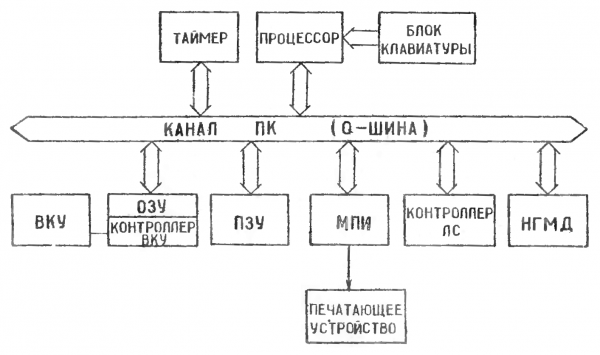

На рис.4 представлена упрощенная блок-схема ПК.

Рис.4. Блок-схема ПК

Все модули, подключенные к каналу ПК, используют одни и те же

канальные связи. Связь между двумя устройствами, подключенными к

каналу, осуществляется по принципу "УПРАВЛЯЮЩИЙ-УПРАВЛЯЕМЫЙ" (ак-

тивный-пассивный). В любой момент времени только одно устройство

является активным (процессор). Активное устройство управляет цикла-

ми обращения к каналу, удовлетворяет, если это необходимо, требова-

ниям прерывания от внешних устройств. Пассивное устройство (управляе-

мое) является только исполнительным. Оно может принимать или пере-

давать информацию только под управлением активного устройства.

Связь через канал замкнута, т.е. на управляющий сигнал, пере-

даваемый активным устройством, должен поступить ответный сигнал

пассивного устройства. Асинхронное выполнение операции передачи

данных устраняет необходимость в тактовых импульсах. В результате

этого обмен с каждым устройством может происходить с максимально

возможным для данного устройства быстродействием.

5.5.1. Сигналы управления каналом

Как адрес, так и данные (слова или байты) передаются по одним

и тем же 16 линиям адреса/данных К ДА(00-15)Н. Любой цикл обращения

к каналу начинается с адресации пассивного устройства. После завер-

шения адресной части цикла активное устройство выполняет прием или

передачу данных, которые выполняются асинхронно и требуют ответа

от адресуемого устройства.

Функции синхронизации при передаче адреса и приеме/передаче

данных выполняют сигналы управления каналом К СИА Н, К БАЙТ Н, К

ВВОД Н, К ВЫВОД Н, К СИП Н.

Сигнал синхронизации активного устройства (К СИА Н) вырабатыва-

ется активным устройством (процессором). Передний фронт этого сигна-

ла означает, что адрес находится на линиях К ДА(00-15)Н. Сигнал

К СИА Н сохраняет активный уровень до окончания текущего цикла обра-

щения к каналу.

Сигнал синхронизации пассивного устройства (К СИП Н) информи-

рует активное устройство о том, что данные приняты с линией К ДА(00-15)Н

или данные установлены на информационных линиях. Этот сигнал выраба-

тывается в ответ на сигнал К ВВОД Н и К ВЫВОД Н.

Сигнал К ВВОД используется в двух случаях:

1. При вырабатывании во время действия сигнала К СИА Н он озна-

чает ввод данных по отношению к активному устройству. Сигнал К ВВОД

вырабатывается, когда активное устройство готово принять данные от

пассивного устройства;

2. При вырабатывании вместе с сигналом К ВПР Н (сигнал К СИА Н-

ПАССИВНЫЙ) означает, что выполняется операция ввода адреса вектора

при прерывании программы. Сигнал К ВЫВОД Н означает, что по отноше-

нию к активному устройству выполняется операция вывода, и на линиях

К ДА(00-15)Н помещены истинные данные. Выработка сигнала К ВЫВОД Н

активным устройством по отношению к подаваемым в канал данным задер-

жана не менее чем на 150 нс. Пассивное устройство, отвечая на сигнал

К ВЫВОД Н, должно вырабатывать ответный сигнал К СИП Н, чтобы завер-

шить операцию передачи данных.

Сигнал вывода байта (К БАЙТ Н) используется в двух случаях:

1. При вырабатывании в адресной части цикла для указания, что

далее следует операция "ВЫВОД БАЙТА";

2. При передаче данных в цикле ВЫВОД В для указания, что выво-

дится байт.

Сигнал запрос прерывания К ЗПР Н вырабатывается пассивным уст-

ройствром, если его триггеры запроса прерывания и разрешения прерыва-

ния установлены. Этот сигнал информирует процессор о том, то уст-

ройство готово передавать или принимать данные. Если 7 разряд ССП уста-

новлен в ноль, процессор разрешит прерывание, вырабатывая сигналы

К ВВОД Н и КППРОН (выходной сигнал подтверждения прерывания).

Сигнал выбора (внешнего устройства (К ВУ Н) вырабатывается

активным устройством, когда в канал передается адрес, относящийся к

последним 4К адресов (с 160000 по 177776). Сигнал К ВУ Н остается

активным на время адресной части цикла обращения к каналу.

Сигнал К СБРОС Н вырабатывается процессором, чтобы выполнить

начальную установку всех устройств, подключенных к каналу. Сигнал

К СБРОС Н вырабатывается программно по команде и при пуске програм-

мы (нажмите клавиши "G").

5.5.2. Циклы обращения к каналу

Для выполнения любой команды процессору требуется выполнить хотя бы одну операцию обращения к каналу. Для некоторых команд тре- буется выполнить несколько операций. Первой такой операцией для всех команд является ввод данных из ячейки памяти, адрес которой опреде- ляется счетчиком команд (CK). Все операции обращения к каналу для ввода и вывода данных называются циклами обращения к каналу. Если для выполнения команды не требуется обращаться за операндами к па- мяти или к внешним устройствам, дополнительных циклов канала не требуется. Однако, если выполняется команда с обращением к памяти или устройствам, то в этом случае могут выполняться любые из следую- щих циклов: ввод; ввод-пауза-вывод: вывод; вывод Б.

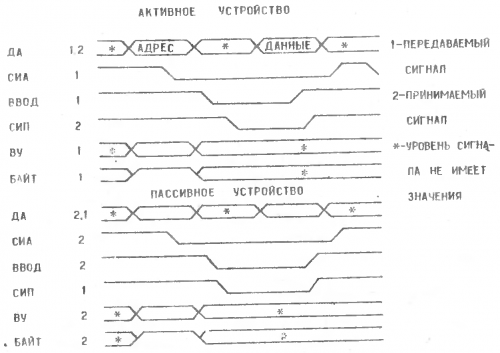

- 5.5.2.1. Цикл ВВОД

Направление передачи при выполнении операций обмена данными

определяется по отношению к активному устройству. При выполнении

цикла ВВОД данные передаются от пассивного устройства к активному.

Временная диаграмма выполнения цикла ВВОД представлена на рис.5.

Рис.5. Временная диаграмма выполнения цикла ВВОД

Порядок выполнения операций следующий:

Активное устройство в адресной части передает по линиям К

ДА(00-I5) H адрес, a также вырабатывает сигнал K BУ H, если адрес

находится в диапазоне 160000-177777. Hе менее чем через 150 нc после

установки адреса активное устройство вырабатывает сигнал К СИА H,

предназначенный для запоминания адреса во входной логике выбранного

устройства.

Пассивное устройство дешифрирует адрес и запоминает его.

Активное устройство снимает адрес с линий К ДА (00-15) H, очища-

ет линию К ВУ H и вырабатывает сигнал K ВВОД H, сигнализируя о том,

что оно готово принять данные от пассивного устройства и ожидает по-

ступления сигнала К СИП Н.

Пассивное устройство помещает данные на линии К ДА(00-15)Н

и вырабатывает сигнал К СИП H, сигнализирующий о том, что данные

находятся в канале. Если сигнал К СИП H не вырабатывается в течение

10 мкс после выработки сигнала К ВВОД Н, центральный процессор пе-

реходит к обслуживанию внутреннего прерывания по ошибке обращения

к каналу с адресом вектора 4.

Активное устройство принимает сигнал К СИП Н, принимает данные,

снимает сигнал К ВВОД Н.

Пассивное устройство снимает сигнал К СИП H, завершая операцию

передачи данных.

Активное устройство снимает сигнал К СИА Н по заднему фронту

сигнала К СИП H, завершая тем самым канальный цикл ВВОД.

Во время выполнения цикла ВВОД сигнал К БАЙТ H не вырабаты-

вается.

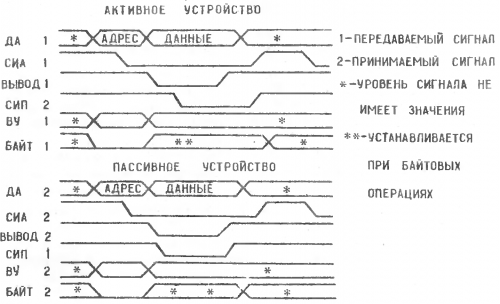

- 5.5.2.2. Цикл ВЫВОД

При выполнении цикла ВЫВОД данные передаются от активного уст-

ройства к пассивному, например, происходит запись данных в память.

Временная диаграмма выполнения цикла ВЫВОД представлена на

рис.6.

Рис.6. Временная диаграмма выполнения цикла ВЫВОД

Порядок выполнения операций следующий:

Активное устройство в адресной части цикла передает по линиям

К ДА(00-15)Н адрес, а также сигнал К ВУ Н, если это необходимо.

Кроме того, в цикле "ВЫВОД" в адресной части вырабатывается

сигнал К БАЙТ H. He менее чем через 150 нс после установки адреса

вырабатывается сигнал К СИА Н. Функции, выполняемые этими двумя

сигналами, те же, что и в цикле ВВОД.

Пассивное устройство дешифрирует адрес и запоминает его. Актив-

ное устройство снимает адрес с линий К ДА(00-15)Н, очищает линию

К ВУ H и снимает сигнал К БАЙТ Н. После этого активное устройство

помещает данные на линии К ДА(00-15) и вырабатывает сигнал

К ВЫВОД Н.

Пассивное устройство принимает данные с линий К ДА(00-15)Н и

вырабатывает сигнал К СИП Н.

Активное устройство снимает сигнал К CИА H, завершая цикл кана-

ла ВЫВОД.