Радио-86РК/Радио 05,06-87/Если нет КР580ВГ75: различия между версиями

Panther (обсуждение | вклад) (retro.h1.ru) |

Panther (обсуждение | вклад) (+ img) |

||

| Строка 7: | Строка 7: | ||

== Принципиальная схема == | == Принципиальная схема == | ||

[[Изображение:Radio-05-87-Radio-VG75-01.png|200px|right]] | |||

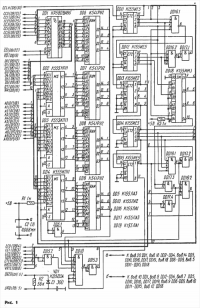

Принципиальная схема контроллера показана на рис.1. На микросхемах DD6—DD9 выполнено буферное ОЗУ, предназначенное для хранения информации, выводимой на экран дисплея. Каждая его ячейка соответствует определенному знакоместу на экране. Для микропроцессора вывод символа на экран сводится к записи его кода в соответствующую ячейку этого ОЗУ. При использовании БИС КР580ВГ75 этот буфер занимает часть ОЗУ компьютера. Второй буфер находится внутри БИС и состоит из двух регистров, емкость каждого из которых равна числу знакомест в строке. Коды символа считываются из одного из регистров и выводятся на экран. В это же время коды символов следующей строки пересылаются из экранной области ОЗУ во второй регистр. По окончании отображения строки регистры меняются местами и процесс повторяется. | Принципиальная схема контроллера показана на рис.1. На микросхемах DD6—DD9 выполнено буферное ОЗУ, предназначенное для хранения информации, выводимой на экран дисплея. Каждая его ячейка соответствует определенному знакоместу на экране. Для микропроцессора вывод символа на экран сводится к записи его кода в соответствующую ячейку этого ОЗУ. При использовании БИС КР580ВГ75 этот буфер занимает часть ОЗУ компьютера. Второй буфер находится внутри БИС и состоит из двух регистров, емкость каждого из которых равна числу знакомест в строке. Коды символа считываются из одного из регистров и выводятся на экран. В это же время коды символов следующей строки пересылаются из экранной области ОЗУ во второй регистр. По окончании отображения строки регистры меняются местами и процесс повторяется. | ||

| Строка 31: | Строка 32: | ||

== Конструкция и детали == | == Конструкция и детали == | ||

[[Изображение:Radio-05-87-Radio-VG75-02.png|200px|right]] | |||

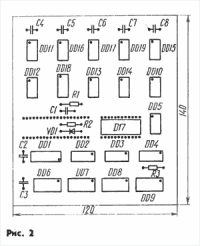

Контроллер собран на плате из фольгированного стеклотекстолита. Расположение деталей на ней показано на рис.2. Общий провод и цепь питания +5. В выполнены печатными проводниками максимальной ширины, остальной монтаж — тонким изолированным проводом. Для уменьшения паразитных связей провода рекомендуется прокладывать по кратчайшему пути между соединяемыми выводами микросхем и не объединять в жгут. Удобно использовать обмоточный провод марки ПЭПЛОТ, который можно облуживать паяльником, не удаляя изоляции. | Контроллер собран на плате из фольгированного стеклотекстолита. Расположение деталей на ней показано на рис.2. Общий провод и цепь питания +5. В выполнены печатными проводниками максимальной ширины, остальной монтаж — тонким изолированным проводом. Для уменьшения паразитных связей провода рекомендуется прокладывать по кратчайшему пути между соединяемыми выводами микросхем и не объединять в жгут. Удобно использовать обмоточный провод марки ПЭПЛОТ, который можно облуживать паяльником, не удаляя изоляции. | ||

| Строка 47: | Строка 49: | ||

Буферное ОЗУ можно выполнить практически на любых статических микросхемах памяти. Как уже говорилось, его объем должен быть не менее 2048 восьмиразрядных слов. Как правило, микросхемы ОЗУ имеют раздельные вход и выход данных. При использовании таких микросхем в контроллере эти выводы соединяют вместе. | Буферное ОЗУ можно выполнить практически на любых статических микросхемах памяти. Как уже говорилось, его объем должен быть не менее 2048 восьмиразрядных слов. Как правило, микросхемы ОЗУ имеют раздельные вход и выход данных. При использовании таких микросхем в контроллере эти выводы соединяют вместе. | ||

[[Изображение:Radio-05-87-Radio-VG75-03.png|200px|right]] | |||

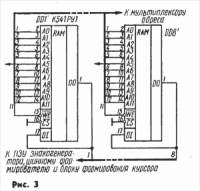

На рис.3 приведена схема буферного ОЗУ на микросхемах К541РУ1. Подключение их выводов 7 зависит от буквенного индекса в обозначении типа: у микросхем К541РУ1В его соединяют с источником питания +5В через резистор, а у К541РУ1Б — с общим проводом. В микросхемах К541РУ1А в зависимости от логического уровня напряжения на этом выводе будет работать та или иная половина из имеющихся 4096 ячеек. | На рис.3 приведена схема буферного ОЗУ на микросхемах К541РУ1. Подключение их выводов 7 зависит от буквенного индекса в обозначении типа: у микросхем К541РУ1В его соединяют с источником питания +5В через резистор, а у К541РУ1Б — с общим проводом. В микросхемах К541РУ1А в зависимости от логического уровня напряжения на этом выводе будет работать та или иная половина из имеющихся 4096 ячеек. | ||

| Строка 53: | Строка 56: | ||

Налаживание контроллера целесообразно начать с тщательной проверки монтажа, обращая особое внимание на возможность коротких замыканий между соседними выводами микросхем. Для первого включения и проверки работы основных узлов контроллера не обязательно подключать его к РК, достаточно подать на него напряжение питания и импульсы CCLK от какого-либо генератора. | Налаживание контроллера целесообразно начать с тщательной проверки монтажа, обращая особое внимание на возможность коротких замыканий между соседними выводами микросхем. Для первого включения и проверки работы основных узлов контроллера не обязательно подключать его к РК, достаточно подать на него напряжение питания и импульсы CCLK от какого-либо генератора. | ||

[[Изображение:Radio-06-87-Radio-VG75-04.png|200px|right]] | |||

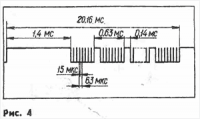

Сначала на выходах HRTC и VRTC осциллографом контролируют наличие и параметры соответственно строчных и кадровых синхроимпульсов. Форма сигнала VSP должна соответствовать показанной на рис.4. Сигнал на выходе LTEN (импульсы длительностью 63 мкс с периодом 630 мкс и частотой появления около 6 Гц) удобно наблюдать, отключив от остальной части устройства вывод 6 микросхемы DD10. | Сначала на выходах HRTC и VRTC осциллографом контролируют наличие и параметры соответственно строчных и кадровых синхроимпульсов. Форма сигнала VSP должна соответствовать показанной на рис.4. Сигнал на выходе LTEN (импульсы длительностью 63 мкс с периодом 630 мкс и частотой появления около 6 Гц) удобно наблюдать, отключив от остальной части устройства вывод 6 микросхемы DD10. | ||

| Строка 69: | Строка 73: | ||

== Программное обеспечение == | == Программное обеспечение == | ||

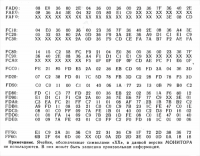

[[Изображение:Radio-06-87-Radio-VG75-05.png|200px|right]] | |||

Для работы РК с описанным контроллером в программу МОНИТОР ([], табл. 4) необходимо внести изменения в соответствии с табл.1. Из МОНИТОРА удалены все команды, связанные с настройкой и управлением БИС КР580ВГ75. Изменен и режим работы контроллера ПДП. Теперь он регенерирует динамическое ОЗУ, периодически обращаясь к 128 его ячейкам. Кроме того, изменены адреса буферного ОЗУ и некоторые константы в подпрограмме вывода символа на экран дисплея. | Для работы РК с описанным контроллером в программу МОНИТОР ([], табл. 4) необходимо внести изменения в соответствии с табл.1. Из МОНИТОРА удалены все команды, связанные с настройкой и управлением БИС КР580ВГ75. Изменен и режим работы контроллера ПДП. Теперь он регенерирует динамическое ОЗУ, периодически обращаясь к 128 его ячейкам. Кроме того, изменены адреса буферного ОЗУ и некоторые константы в подпрограмме вывода символа на экран дисплея. | ||

Текущая версия от 17:57, 31 октября 2007

| Данный материал защищён авторскими правами!

Использование материала заявлено как добросовестное, исключительно для образовательных некоммерческих целей. Автор: А. ДОЛГИЙ |

В компьютере «Радио-86РК» (далее для краткости — РК) узел формирования изображения на экране телевизора выполнен на основе специализированной БИС КР580ВГ75, которая, к сожалению, выпускается пока в очень ограниченном количестве. Для многих радиолюбителей ее дефицитность стала серьезным препятствием к повторению РК. Предлагаемый вниманию читателей контроллер электронно-лучевой трубки позволяет обойтись без этой БИС. Он построен в основном на широко распространенных микросхемах малого и среднего уровня интеграции и БИС ОЗУ, которые могут быть практически любого типа. Применение описываемого контроллера освобождает для использования в прикладных программах примерно 2.5 Кбайт ОЗУ компьютера.

Необходимо отметить, что контроллер не является точным функциональным аналогом заменяемой БИС, а выполняет только те ее функции, которые необходимы для работы РК, причем некоторые из них выполняются иначе, чем в БИС КР580ВГ75. Об этих отличиях будет рассказано ниже — при описании схемы и программного обеспечения контроллера.

Принципиальная схема

Принципиальная схема контроллера показана на рис.1. На микросхемах DD6—DD9 выполнено буферное ОЗУ, предназначенное для хранения информации, выводимой на экран дисплея. Каждая его ячейка соответствует определенному знакоместу на экране. Для микропроцессора вывод символа на экран сводится к записи его кода в соответствующую ячейку этого ОЗУ. При использовании БИС КР580ВГ75 этот буфер занимает часть ОЗУ компьютера. Второй буфер находится внутри БИС и состоит из двух регистров, емкость каждого из которых равна числу знакомест в строке. Коды символа считываются из одного из регистров и выводятся на экран. В это же время коды символов следующей строки пересылаются из экранной области ОЗУ во второй регистр. По окончании отображения строки регистры меняются местами и процесс повторяется.

В рассматриваемом контроллере буфер только один. Адрес ячейки ОЗУ, соответствующей отображаемому в данный момент символу, со счетчиков строк и знакомест поступает на адресные входы микросхем через мультиплексоры DD2--DD4. С выходов микросхем ОЗУ код символа подается на ПЗУ знакогенератора компьютера. Старший разряд этого же кода участвует в формировании курсора.

Через шинный формирователь DD1 и мультиплексоры буферное ОЗУ может быть подключено к шинам адреса и данных микропроцессора. Это происходит при обращении к нему микропроцессора и наличии низкого уровня на выводе, подключенном ранее ко входу CS БИС КР580ВГ75. Если при этом такой же уровень будет установлен и на выводе WR, то произойдет запись кода, находящегося на шине данных, в буферное ОЗУ, а если низкий уровень появится на выводе RD, то информация из буферного ОЗУ поступит на шину данных. Сигнал CS участвует также в формировании курсора и сигнала запрета отображения, что устраняет паразитную засветку экрана в моменты обращения микропроцессора к буферному ОЗУ.

Счетчик знакомест в строке, на который с процессорной платы поступают импульсы символьной синхронизации (CCLK) с периодом 0,75 мкс, построен на микросхемах DD11, DD12. С приходом 78-го по счету импульса на выходе элемента DD16.1 возникает отрицательный перепад напряжения, который изменяет состояние триггера, входящего в состав микросхемы DD12, и на ее выводе 12 появляется высокий уровень. При поступлении 84-го импульса CCLK высокий уровень с выхода элемента DD17.1 поступает на входы RO счетчиков DD11, DD12 и устанавливает их в исходное состояние (низкий уровень на всех выходах). Таким образом, на выводе 12 микросхемы DD12 формируется строчный синхроимпульс длительностью 4,5 мкс с периодом повторения 63 мкс. В каждой строке может быть отображено 64 символа, причем отображение первого из них начинается спустя 8 периодов повторения импульсов после окончания строчного синхроимпульса. Шесть младших разрядов адреса буферного ОЗУ, соответствующих номеру знакоместа в строке, получаются вычитанием числа 8 из выходного кода счетчика знакомест. Вычитание выполняет сумматор DD18. С выхода его старшего разряда строчный гасящий импульс поступает в узел формирования сигнала запрета отображения.

При использовании БИС КР580ВГ75 строчный гасящий импульс формируется программно: в ячейки ОЗУ, соответствующие знакоместам, находящимся за пределами активной части экрана, записываются коды пробела. Для отображения строки из 64 символов требуется 78 ячеек ОЗУ, а общий объем буфера равен 2340 байт. Аппаратное формирование строчного гасящего импульса позволило сократить этот объем до 2048 байт и уменьшить число микросхем в контроллере.

На микросхеме DD13 построен счетчик телевизионных строк в одной строке знакомест. Код номера строки (LC0 — LC2) поступает с выходов этого счетчика на адресные входы ПЗУ знакогенератора.

Микросхема DD14 и один триггер микросхемы DD15 образуют счетчик строк с коэффициентом пересчета 32. Для отображения символов используются 25 строк, неиспользуемые гасятся программно. Пять разрядов кода номера строки подаются со счетчика на мультиплексор адреса. Элементы DD19.1, DD17.2 формируют кадровый синхроимпульс (VRTC) длительностью 1260 мкс с периодом повторения 20160 мкс.

Узел на элементах микросхем DD19.2, DD17.3 и DD17.4 формирует сигнал запрета отображения (VSP), поступающий на вход ОЕ микросхемы ПЗУ знакогенератора и отключающий ее выходы при высоком уровне сигнала. Благодаря этому на входах регистра сдвига, входящего в узел формирования видеосигнала процессорной платы, также устанавливается высокий уровень, что соответствует гашению изображения.

Сигнал разрешения подчеркивания знакоместа (LTEN) формируется элементами DD10, DD5.2 и DD5.3 и используется для создания курсора на экране дисплея. Положение курсора задается записью единицы в старший разряд соответствующей ячейки буферного ОЗУ (в БИС КР580ВГ75 для задания положения курсора предусмотрены специальные регистры). Курсор мигает с частотой, которая получается делением частоты повторения кадровых синхроимпульсов на 8 счетчиком DD15.

Кроме формирования изображения на экране дисплея, БИС КР580ВГ75 выполняет в РК еще одну важную функцию: периодически обращаясь к ячейкам микросхем динамического ОЗУ компьютера в режиме прямого доступа к памяти (ПДП), она обеспечивает регенерацию записанной в него информации. Описываемый контроллер к ОЗУ не обращается, а необходимые для регенерации запросы ПДП искусственно формируются цепью R2C1VD1.

В исходном состоянии на выходе DAC2 (вывод 14) микросхемы контроллера ПДП КР580ИК57, находящейся на процессорной плате, и на соединенном с ним входе DACK (вывод 6 панели БИС D8) устанавливается высокий уровень, поэтому конденсатор С1 начинает заряжаться через резистор R2. Как только напряжение на нем, а следовательно, на выходе DRQ (вывод 5 панели БИС D8) и соединенном с ним входе DRQ2 (вывод 17) БИС КР580ИК57 достигает высокого уровня, контроллер принимает запрос и начинает цикл ПДП. На выходе DAC2 (вывод 14) при этом устанавливается низкий уровень, и конденсатор С1 разряжается через диод VD1. По окончании цикла ПДП на выходе DAC2 вновь устанавливается высокий уровень, и весь процесс повторяется вновь. Постоянная времени цепи R2CI выбрана таким образом, что циклы ПДП следуют с периодом около 15 мкс.

Конструкция и детали

Контроллер собран на плате из фольгированного стеклотекстолита. Расположение деталей на ней показано на рис.2. Общий провод и цепь питания +5. В выполнены печатными проводниками максимальной ширины, остальной монтаж — тонким изолированным проводом. Для уменьшения паразитных связей провода рекомендуется прокладывать по кратчайшему пути между соединяемыми выводами микросхем и не объединять в жгут. Удобно использовать обмоточный провод марки ПЭПЛОТ, который можно облуживать паяльником, не удаляя изоляции.

Для соединения с процессорной платой в контроллере предусмотрены контактные штыри, вставляемые в гнезда панелей, предназначенных для установки микросхем D8 и D17 (последняя перенесена на плату контроллера). При необходимости панели можно изготовить из гнездовых частей соединителей СНП34. Контактные штыри изготавливают из штыревых частей соединителей этого же типа.

Контроллер потребляет от источника питания ток около 800 мА. Чтобы не перегружать печатные проводники процессорной платы, рекомендуется соединить цепи общего провода и +5В контроллера непосредственно с соответствующими контактами соединителя Х1 процессорной платы проводами большого сечения.

Дополнительно контроллер крепят к процессорной плате четырьмя стойками из изоляционного материала. Их можно прикрепить к процессорной плате винтами или (если печатные проводники не позволяют просверлить отверстия) приклеить клеем БФ-2.

Возможны и другие варианты конструкции. В частности, для уменьшения числа проводов, соединяющих процессорную плату с контроллером, на плату последнего целесообразно перенести микросхемы и другие элементы узла формирования видеосигнала.

Замена микросхем

Указанные на принципиальной схеме ИС серий К155 и К555 можно заменить их функциональными аналогами серий К155, К555, К531. Вместо ИС К555КП11 можно применить К155КП14, но в этом случае между выходом Y4 (вывод 12) микросхемы DD4 и входами разрешения записи микросхем ОЗУ нужно включить инвертор, использовав в этом качестве свободный элемент микросхемы DD5. Шинный формирователь КР580ВА86 можно заменить двумя микросхемами К589АП16. В крайнем случае, можно применить КР580ВА87 или две К589АП26, но это потребует включения инверторов между выходами микросхем ОЗУ и входами ПЗУ знакогенератора и узла формирования курсора.

Буферное ОЗУ можно выполнить практически на любых статических микросхемах памяти. Как уже говорилось, его объем должен быть не менее 2048 восьмиразрядных слов. Как правило, микросхемы ОЗУ имеют раздельные вход и выход данных. При использовании таких микросхем в контроллере эти выводы соединяют вместе.

На рис.3 приведена схема буферного ОЗУ на микросхемах К541РУ1. Подключение их выводов 7 зависит от буквенного индекса в обозначении типа: у микросхем К541РУ1В его соединяют с источником питания +5В через резистор, а у К541РУ1Б — с общим проводом. В микросхемах К541РУ1А в зависимости от логического уровня напряжения на этом выводе будет работать та или иная половина из имеющихся 4096 ячеек.

Налаживание

Налаживание контроллера целесообразно начать с тщательной проверки монтажа, обращая особое внимание на возможность коротких замыканий между соседними выводами микросхем. Для первого включения и проверки работы основных узлов контроллера не обязательно подключать его к РК, достаточно подать на него напряжение питания и импульсы CCLK от какого-либо генератора.

Сначала на выходах HRTC и VRTC осциллографом контролируют наличие и параметры соответственно строчных и кадровых синхроимпульсов. Форма сигнала VSP должна соответствовать показанной на рис.4. Сигнал на выходе LTEN (импульсы длительностью 63 мкс с периодом 630 мкс и частотой появления около 6 Гц) удобно наблюдать, отключив от остальной части устройства вывод 6 микросхемы DD10.

Затем проверяют наличие сигналов, поступающих через мультиплексоры с выходов счетчиков знакомест и строк на адресные входы микросхем ОЗУ. На выходы LC0—LC2 должны поступать сигналы с выходов счетчика телевизионных строк, а на СС0—СС6 — последовательность нулей и единиц, образовавшихся в буферном ОЗУ при включении питания. Следует отметить, что некоторые микросхемы ОЗУ (в том числе К541РУ1 ранних выпусков) имеют открытый коллекторный выход. При использовании таких микросхем между их выходами и источником +5В нужно включить нагрузочные резисторы сопротивлением 1 …2 кОм. В противном случае сигналы на выходах СС0—--СС6 могут либо отсутствовать вообще, либо иметь очень низкий уровень логической 1.

Для дальнейшей проверки входы CS и WR контроллера необходимо соединить с общим проводом. При этом на выходе LTEN и входах WE микросхем ОЗУ должен установиться низкий уровень, а на выходе VSP и адресных входах микросхем — высокий. Поочередно соединяя с общим проводом входы А0—А10, D0—07 контроллера, убеждаются, что эти сигналы поступают на соответствующие входы микросхем ОЗУ,

Проверенную плату контроллера можно подключить к процессорной плате РК. В ПЗУ D17 должна быть записана программа МОНИТОР [1] с изменениями, указанными ниже. После включения питания экран телевизора может быть заполнен случайным набором символов. При нажатии на кнопку «СБРОС» экран должен очиститься и в его верхнем левом углу должна появиться надпись Р-86РК/ДМ, свидетельствующая о готовности компьютера к работе.

Возможные неисправности

Не останавливаясь на налаживании собственно РК, рассмотрим некоторые возможные неисправности узла формирования видеосигнала. Если выводимый символ появляется не на своем месте или одновременно в нескольких местах экрана, то вероятнее всего неисправны адресные цепи буферного ОЗУ. Искажение формы символа (если, конечно, а ПЗУ знакогенератора записана правильная информация) чаще всего свидетельствует об обрывах или замыканиях в цепях, соединяющих выходы ПЗУ знакогенератора со входами регистра сдвига. И, наконец, вывод одних символов вместо других возможен при неисправностях в цепях сигналов СС0— СС6, а также микросхем буферного ОЗУ и шинного формирователя.

Иногда вертикальные линии выводимых на экран телевизора символов имеют заметно меньшую яркость, чем горизонтальные, что свидетельствует о недостаточной полосе пропускания видеотракта телевизора. В этом случае на процессорной плате параллельно резистору R15 полезно включить конденсатор емкостью 56…68 пФ.

Программное обеспечение

Для работы РК с описанным контроллером в программу МОНИТОР ([], табл. 4) необходимо внести изменения в соответствии с табл.1. Из МОНИТОРА удалены все команды, связанные с настройкой и управлением БИС КР580ВГ75. Изменен и режим работы контроллера ПДП. Теперь он регенерирует динамическое ОЗУ, периодически обращаясь к 128 его ячейкам. Кроме того, изменены адреса буферного ОЗУ и некоторые константы в подпрограмме вывода символа на экран дисплея.

Как уже отмечалось, описанный контроллер позволяет освободить для программ и данных пользователя область ОЗУ, ранее занятую буфером экрана. Для этого нужно изменить коды в ячейках 0FC26H, 0FC2AH, 0FD97H и ячейках, перечисленных в табл. 7 [2], кроме 0FAFIH. 0FC15H, 0FC2BH, 0FC2FH, 0FC8CH, 0FCCBH, 0FD51H, 0FD54H, 0FDA5H и 0FDB7H. Код 35Н заменяют на ЗЕН (для ОЗУ объемом 32 Кбайт — на 7ЕН), а 36Н — на 3FH (7FH). В результате рабочие ячейки МОНИТОРА из области 3600Н—36CFH переместятся в область 3F00H—3FCFH (7F00H— 7FCFH). Верхняя граница памяти, доступной пользователю, станет равной 3EFFH (7EFFH).

Компьютер с описанным контроллером полностью программно совместим с РК, в котором использована БИС КР580ВГ75, при условии, что обращение к машинным ресурсам происходит исключительно через подпрограммы МОНИТОРА. В программах же, которые «незаконно» (с точки зрения МОНИТОРА) обращаются непосредственно к ячейкам буферного ОЗУ экрана, необходимо изменить соответствующие адреса. Например, в интерпретаторе языка Бейсик [3] в ячейки 17F0H и 17F1H нужно записать адрес 0С0С0Н, соответствующий началу верхней строки знакомест, а в ячейке 17F3Н константу 4ЕН (десятичное значение 78) заменить на 40Н (64).

| Номер строки | Адреса | |

| КР580ВГ75 | Контроллер no схеме на рис. 1 | |

| 1 | 37C2 – 3801 | C0C0 – С0CF |

| 2 | 3810 – 384F | С100 — C13F |

| 3 | 385E – 3890 | С140 - C17F |

| 4 | 38AС - 38EB | C180 – C1BF |

| 5 | 38FA – 3939 | C1C0 – C1FF |

| 6 | 3948 – 3987 | C200 - C23F |

| 7 | 3996 – 3905 | C240 - C27F |

| 8 | 39E4 - 3A23 | C280 - C2BF |

| 9 | ЗA32 - 3A71 | C2C0 - C2FF |

| 10 | 3A80 – ЗАВЕ | C300 - C33F |

| 11 | 3ACK - 3B0D | C340 - C37F |

| 12 | 3В1С - 3B5B | C380 - C3BF |

| 13 | 3B6A - 3BA9 | C3C0 - C3FF |

| 14 | 3BB8 - 3BF7 | C400 - C43F |

| 15 | 3C06 - 3C45 | C440 - C47F |

| 16 | 3C54 – 3С93 | C480 - C4BF |

| 17 | 3CA2 – 3CH1 | C4C0 - C4FF |

| 18 | ЗСКО – 3D2F | C500 - C53F |

| 19 | 3D3K – 3D7D | C540 - C57F |

| 20 | 3D8C – 3DCB | C580 - С5ВГ |

| 21 | 3DDA – 3K19 | C5C0 - C5FF |

| 22 | 3A28 – 3E67 | C600 - C63F |

| 23 | ЗE76 - 3EB5 | C640 - C67F |

| 24 | 3EC4 - 3F03 | C680 - C6BF |

| 25 | 3F12 - 3F51 | C6C0 - C6FF |

Подобная ситуация может встретиться и в некоторых программах на Бейсике. Так, например, в программе «Питон» [4] переменным SO и CN должны быть присвоены значения — соответственно 16192 и 64.

Для удобства перевода программ в табл. 2 приведены адреса ячеек, соответствующие каждой строке знакомест при использовании БИС КР580ВГ75 и описанного контроллера.

Особенности работы с магнитофоном

В заключение — несколько слов об особенностях работы с магнитофоном. Как и в компьютере с БИС КР580ВГ75, при выводе информации мигает светодиод «РУС/ЛАТ». Однако изображение на экране телевизора во время выполнения директив работы с магнитной лентой не пропадает. В новом варианте МОНИТОРА предусмотрена сигнализация о выполнении директивы ввода данных с магнитной ленты: после приема байта синхронизации уровень напряжения на выводе 16 микросхемы D20 процессорной платы повышается, а по окончании ввода — возвращается к нулю. Если подключить к этому выводу светодиод (через инвертор, аналогично светодиоду «РУС/ЛАТ»), то его загорание будет свидетельствовать о работе РК на ввод данных с магнитной ленты. Подпрограмма восстановления изображения на экране в этом случае не соответствует своему назначению — она лишь восстанавливает режим ПДП и устанавливает низкий уровень на выводе 16 микросхемы D20. Вызов ее по адресу 0F82DH сохранен в МОНИТОРЕ для обеспечения совместимости.

А. ДОЛГИЙ

г. Москва.

Отсканировано с журнала Радио № 5 1987 г.

Отредактировано Лесных Ю.